входом регистра номера сравнения и с первыми информационньоми входами блока замещения и селектора, выходы первого и второго коммутаторов выходной информации подключены к информационным входам сдвигателя, управляющий вход которого соединен с адресным входом устройства, с входом пер-вого слагаемого адресного су.мматора,

/с вторым входом блока анализа, с вторым управляющим входом второго коммутатора выходной информации, с первыми входами второго, третьего, четвертого и пятого коммутаторов адресов и с вторыми входами первого коммутатора адресов и элемента И, первый выход сдвигателя соединен с входом регистра команды, а выход с третьим входом блока анализа, первый и второй выходы которого являются соответственно сигнальным и кодовым выходами устройства, четвертый вход блока анализа подключен к третьему управляющему входу второго коммутатора выходной информации я к выходу регистра номера продолх ения, вход которого соединен с выходом третьего коммутатора выходной информации, информационный вход которого подключен к выходу блока памяти связности строк, вход управления чтением которого соединен с выходом буферного регистра, а адресный вход с выходом четвертого Koivu/iyTaTOpa адресов, второй вход которого соединен с выходом сумматора связности, а третий вход - с выходом адресного сумматора, с вторыми входами третьего и пятого коммутаторов адресов, выход которого подключен к адресному входу блока памяти замещения, информационный вход которого соединен с первым выходом блока замещения, выход блока памяти замещения соединен с вторым информационным входом блока замещения, второй выход которого подключен к второму информационному входу селектора, третий информационный вход которого соединен с выходом регистра номера сравнения, выход треTbeiO комм татора адресов подключен к адресному входу блока памят признаков действительности, выход буфе)ного регистра соединен с вторым входом второго коммутатора адресов, с третьим входом третьего коммутатора адресов и с вторым входом сумматора связности, выход блока выработки прираи ения адреса преднакачки подключен к входу второго слагаемого адресного сумматора, управляющий вход блока выработки приращения адреса преднакачки подключен к сигнальному входу устройства, выход элемента И соединен с вторым входом сумматора адреса строки выход блока памяти адресов подключен к второму информационному входу блока сравнения адресов, выход

которого соединбн с входом шифратора пятый вход блокс1 анализа соединен с входом логического нуля устройства второй вход блока выработки приращения адреса преднакачки соединен с сигнальным входом устройства.

2.Устройство по п. 1, отличающееся тем, что блок анализа содержит дешифратор, две схемы сравнения, четыре элемента НЕ, четыре элемента И и элемент ИЛИ, ыход которого подключен к первому выходу блока, входы элемента ИЛИ соединены соответственно с выходами элементов И, первые входы которых соединены

с выходом первого элемента НЕ, вход которого соединен с выходом первой схемы сравнения, второй вход перво1;о элемента И соединен с выходом второго элемента НЕ, вход которого соединен с nepBMvi входом блока.

3.Устройство лоп. 1, отличающееся тем, что блок выработки приращения адреса преднакачки содержит два элемента НЕ, два элемента И, дешифратор и счетчик преднакачки , выход которого является выходом блока и соединен с входом дешифратора, а входы - соответственно с выходами элементов И, первые входы которых являются соответственно входом микрокоманд и входом переноса устройства, а вторые входы соединены с выходами элементов НЕ, входы которых соединены с входами дешифратора.

4.Устройство по п. 1, отличающееся тем, что блок замещения содержит узел учета хронологии узел формирования кандидата на замещение и регистр хронологии, выход которого подключен к первому выходу, блока, первый вход регистра хронологии соединен с выходом узла учета хронологии, а второй вход - с вторым информационным входом блока и с входом узла формирования кандидата на замещение, вьдход которого соединен

с вторым выходом блока,, входы узла учета хронологии подключены соответственно к первому информационному и li управляющему входам блока.

5.Устройство по пп. 1 и 4, о т лишающееся тем, что узел учета хронологии содержит элемент

НЕ и группу элементов И, причем первый вход узла соединен с первыми входами элементов И группы, выходы которых соединены с выходом узла, вторые входы первого, второго и последнего элементов И группы соединены через элемент НЕ с вторым входом узла, вторые входы остальных элементов И группы соединены с вторым входом узла.

V

6.Устройство по пп. 1 и 4, о тличающееся тем, что узел формирования кандидата на замещение

содержит четыре элемента НЕ, три элемента И и элемент ИЛИ, причем вход блока через первый и второй элементы НЕ соединен с первыми входами первЬго и второго элементов И, вторые входы которых соответственно соединены с входом узла непосредственно и через третий элемент НЕ, выходы

первого и второго элементов И соединены с входами элемента ИЛИ, выход которого через четвертый элемент НЕ соединен с первым входом третьего элемента И, второй вход которого соединен с входом узла, выход которого соединен с выходами элемента ИЛИ и третьих элементов И и НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

1. УСТРОЙСТВО БУФЕРИЗАЦИИ КОМАНД ПРОЦЕССОРА, содержащее блок памяти командных слов, блок памяти адресов, блок памяти признаков действительности, первый коммутатор адресов , блок сравнения адресов, буферный регистр адреса, адресный сумматор и регистр команды, выход которого подключен к выходу команды устройства, вход первого слагаемого адресного сумматора соединен с адресным . входом устройства, выход адресного сумматора соединен с адресным выходом устройства, с входом буферного регистра адреса, с первым входом первого коммутатора адресов и с информационным входом блока памяти адресов , адресный вход которого подключен к первому выходу первого комм татора адресов, второй выход которого соединен с первым информационным входом блока сравнения адресов, информационный вход блока памяти признаков действительности подключен к входу микрокоманд устройства, а выход - к входу разрешения сравнения блока сравнения адресов, информационный вход блока памяти командных слов соединен с информационным входом устройства, отличающеес я тем, что, с целью повышения быстродействия, оно содержит блок памяти связности строк, блок памяти замещения, блок анализа, блок выработки приращения адреса преднакачки, блок замещения, три коммутатора выходной информации, сдвигатель, сумматор адреса строки, сумматор связности, второй, третий, четвертый и пятый коммутаторы адресов, буферный регистр, шифратор, регистр номера сравнения, регистр номера продолжения, селектор и элемент И, вход управления записью блока памяти командных слов соединен с выходом селектора, с информационным входом блока памяти связности строк, с управляющим входом буферного регистра, с входами управления записью блока памяти признаков действительности и блока памяти адресов, вход управления считыванием блока памяти командных слов соединен с входом микрокоманд устройства, с первым входом бло(/) ка выработки приращения адреса преднакачки, с первым входом адресного сумматора, с первым входом элемента И, с входом управления записью блока памяти связности строк, с управляющими входами коммутаторов адресов, с информационными входами буферного регистра, с управляющими входами селектора, блока замещения, блока памяти замещения, с первым входом сумматора связности и с входом управления считыванием блока памяти адресов, вход адреса записи блока памяти командных слов соединен с выходом второго коммутатора адресов и с первым О5 входом сумматора адреса строки, вход адреса считывания .блока памяти командных слов соединен с выходом сумматора адреса строки, выходы блока памяти командных слов соединены соответственно с информационными входами первого и второго коммутаторов выходной информации, управляющий вход первого и первый управляющий вход второго коммутаторов выходной информации соединены с выходом шифратора, С первым входом блока анализа, с управляющим входом третьего коммутатора выходной информации, с

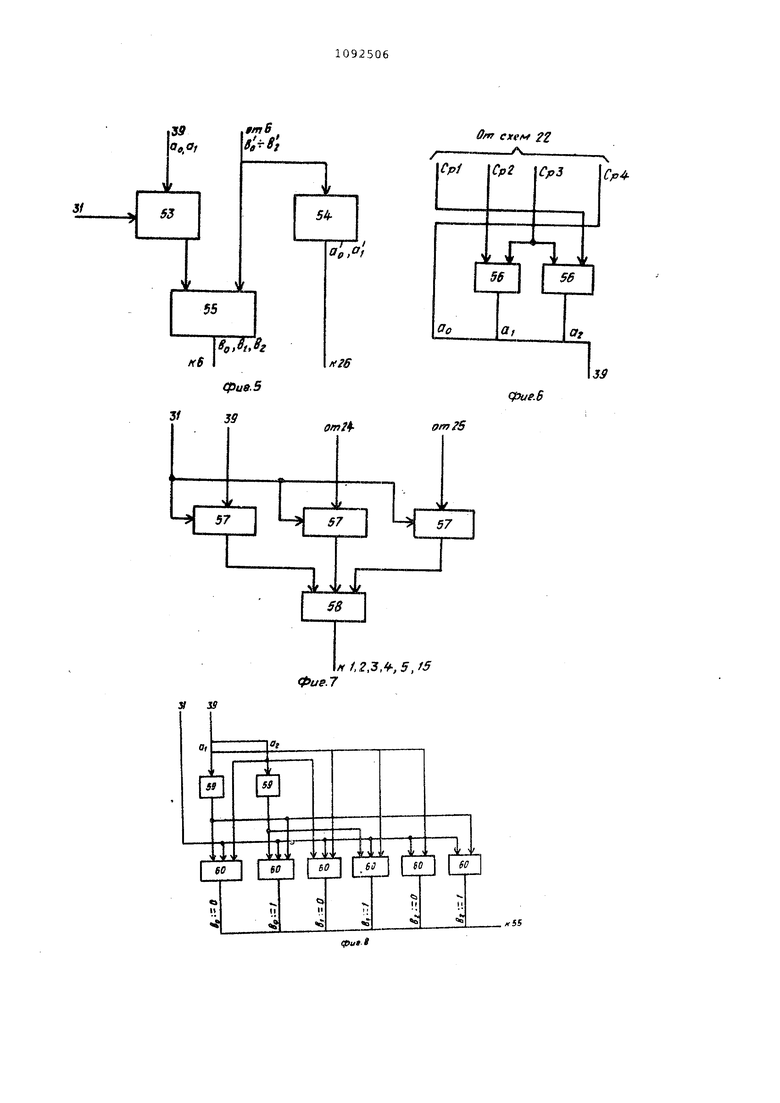

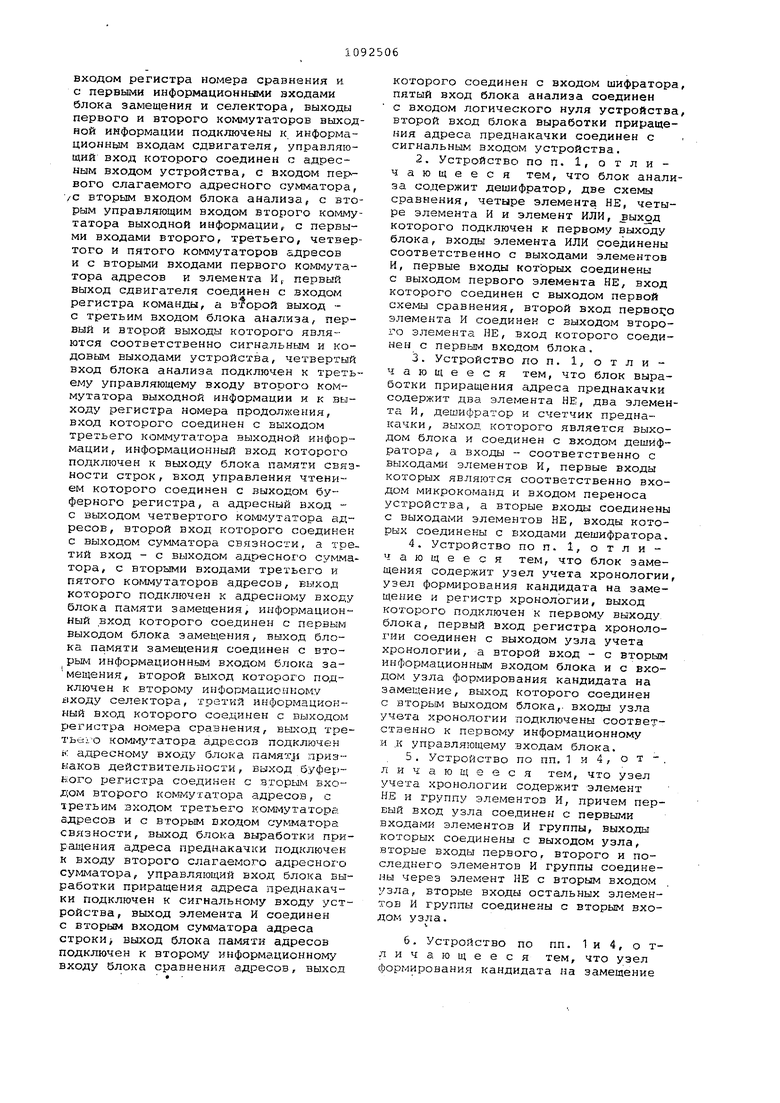

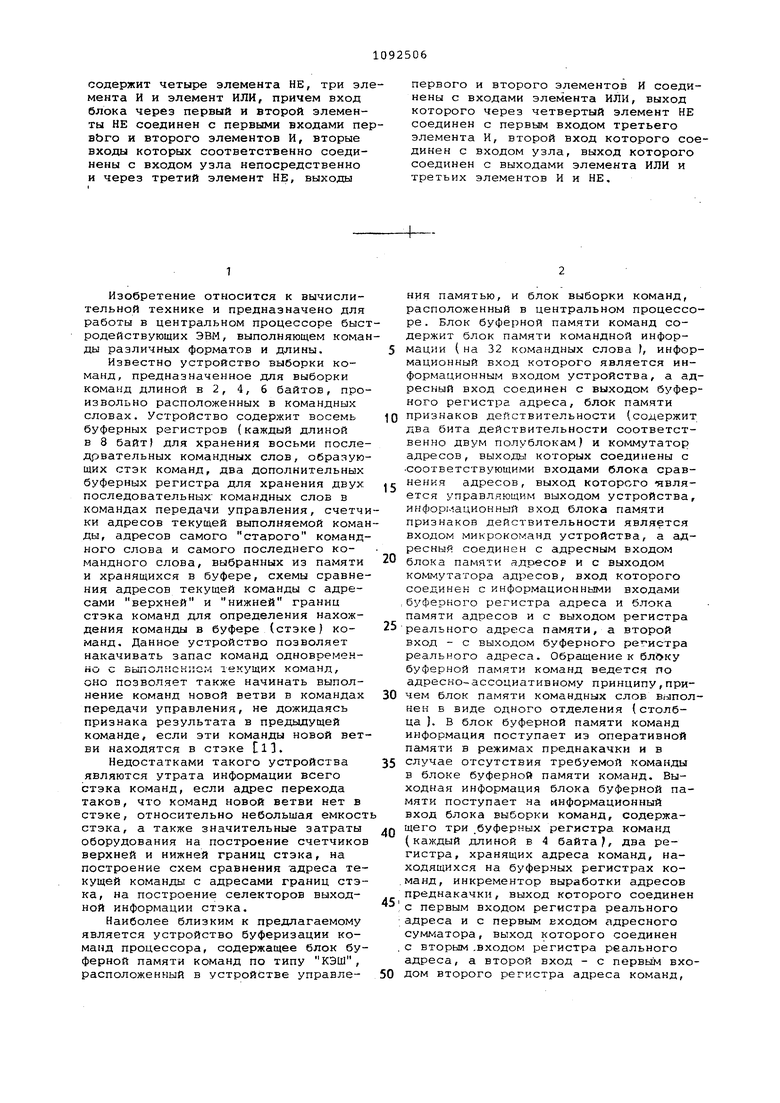

Изобретение относится к вычислительной технике и предназначено для работы в центральном процессоре быс родействующих ЭВМ, выполняющем кома ды различных форматов и длины. Известно устройство выборки команд, предназначенное для выборки команд длиной в 2, 4, 6 байтов, про извольно расположенных в командных словах. Устройство содержит восемь буферных регистров (каждый длиной в 8 байт для хранения восьми после довательных командных слов, образую щих стэк команд, два дополнительных буферных регистра для хранения двух последовательных командных слов в командах передачи управления, счетч ки адресов текущей выполняемой кома ды, адресов самого старого команд ного слова и самого последнего командного слова, выбранных из памяти и хранящихся в буфере, схемы сравне ния адресов текущей команды с адресами верхней и нижней границ стэка команд для определения нахождения команды в буфере (стэке) команд. Данное устройство позволяет накачивать запас команд одновременно с Быполмскисм текущих команд, оно позволяет также начинать выполнение команд новой ветви в командах передачи управления, не дожидаясь признака результата в предыдущей команде, если эти команды новой вет ви находятся в стэке tl3. Недостатками такого устройства являются утрата информации всего стэка команд, если адрес перехода таков, что команд новой ветви нет в стэке, относительно небольшая емкост стэка, а также значительные затраты оборудования на построение счетчиков верхней и нижней границ стэка, на построение схем сравнения адреса текущей команды с адресами границ стэка, на построение селекторов выходной информации стэка. Наиболее близким к предлагаемому является устройство буферизации команд процессора, содержащее блок буферной памяти команд по типу КЭШ, расположенный в устройстве управления памятью, и блок выборки команд, расположенный в центральном процессоре . Блок буферной памяти команд содержит блок памяти командной информации ( на 32 командных слова f, информационный вход которого является информационным входом устройства, а адресный вход соединен с выходом буферного регистра адреса, блок памяти признаков действительности (содержит два бита действительности соответственно двум полублокам) и коммутатор адресов, выходы которых соединены с соответствующими входами блока сравнения адресов, выход которого -является управляющим выходом устройства, инфор:.- ационныП вход блока памяти признаков действительности является входом микрокоманд устройства, а адресный соединен с адресным входом блока памяти адресов и с выходом коммутатора адресов, вход которого соединен с информационными входами буферного регистра адреса и блока памяти адресов и с выходом регистра реального адреса памяти, а второй вход - с выходом буферного регистра реального адреса. Обращение к блоку буферной памяти команд ведется по адресно-ассоциативному принципу,причем блок памяти командных слов выполнен в виде одного отделения (столбца ). В блок буферной памяти команд информация поступает из оперативной памяти в режимах преднакачки и в случае отсутствия требуемой команды в блоке буферной памяти команд. Выходная информация блока буферной памяти поступает на информационный вход блока выборки команд, содержащего три буферных регистра, команд (каждый длиной в 4 байта, два регистра, хранящих адреса команд, находящихся на буферных регистрах команд, инкрементор выработки адресов преднакачки, выход которого соединен с первым входом регистра реального адреса и с первым входом адресного сумматора, выход которого соединен с вторым .входом регистра реального адреса, а второй вход - с первым входом второго регистра адреса команд. первый вход которого соединен с вы ходом регистра реального адреса, а i второй - с соответствующим входом адресного сумматора, с входом инкре ментора и с выходом первого регистр адреса, выход первого регистра команд является выходом команды устройства. Известное устройство осуществляет предварительную выборку ко°Манд.и позволяет значительно снизить потери времени, связанные с выборкой команд из главной памяти ЭВМ t 2 D. Недостатками этого устройства являются его неэффективная работа в случае выполнения команд передачи уп равления, а также значительные затра ты оборудования на посуроение выборки команд. Кроме того, принят одностолбцовый вариант блока памяти командных слов. В этом варианте команды новой ветви, накачиваемые в блок памяти командных слов, могут затирать команды старой ветви, находящиеся в блоке буферной памяти команд, и, таким образом, производительность процессора еще более снижается. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в устройство буферизации команд процессора, содержащее блок памяти командных слов, блок памяти адресов блок памяти признаков действительнос ти, первый коммутатор адресов, блок сравнения адресов, буферный регистр адреса, адресный сумматор и регистр команды, выход которого подключен к выходу команды устройства, вход первого слагаемого адресного суЬМатора соединен с адресным входом устройства, выход адресного cyr iaTopa соединен с ад1зесным выходом устройства, с входом буферного регистра адреса, с первым входом первого коммутатора адресов и с информационным входом блока памяти адресов, адресный вход которого подключен .к первому выходу первого коммутатора адресов, второй выход которого соединен с первым информационным входом блока сравнения адресов, информационный вход блока памяти признаков действительности подключен к входу микрокоманд устрой ства, а выход - к входу разрешения сравнения блока сравнения адресов, информационный вход блока памяти командных слов соединен с информационным входом устройства, введены блок памяти связности строк, блок памяти замещения, блок анализа, блок выработки приращения адреса преднггкачки блок замещения, три коммутатора выходной информации, сдвигатель, сумматор адреса строки, сумматор связности, второй, третий, четвертый и пятый коммутаторы адресов, буферный регистр, шифратор, регистр номера сравнения, регистр номера продолжения, селектор и элемент И, вход управления записью блока памяти командных слов соединен с выходом селектора, с информационным входом блока памяти связности строк, с управляющим входом буферного регистра, с входами управления записью блока памяти признаков действительности и блока памяти адресов,вход управления считыванием блока памяти командных слов соединен с входом микрокоманд устройства, с первым входом блока выработки приращения адреса преднакачки, с первым входом адресного сумматора, с первым входом элемента И, с входом управления записью блока памяти связности строк, с управляющими входами коммутаторов адресов, с информационными входами буферного регистра, с управляющими входами селектора, блока замещения,, блока памяти замещения, с первым входом сумматора связности и с входом управления считыванием блока памяти адресов, вход адреса записи блока командных слов соединен с выходом второго коммутатора адресов и с первым входом сумматора адреса строки, вход сщреса считывания блока памяти комгшдных слов соединен с выходом сумматора адреса строки, Быходы блока памяти командных слов соединены соответственно с информационными входами первого и второго коммутаторов выходной информации, управляющий вход первого и первый управляющий вход второго коммутаторов выходной информации соединены с выходом шифратора, с первым входом блока анализа, с управляющим входом третьего коммутатора выходной информации , с входом регистра номера сравнения и с первыми информационными входами блока замещения и селектора, выходы первого и второго коммутаторов выходной информации подключены к информационным входам сдвигателя,. управляющий вход которого соединен с адресным входом устройства, с входом первого слагаемого адресного сумматора, с вторым входом блока анализа, с вторым управляющим входом второго KotvtMyxaTopa выходной информации, с первыми входами второго, третьего, четвертого и пятого коммутаторов адресов и с вторыми входами первого коммутатора адресов и элемента И, первый выход сдвигателя соединен с входом регистра команды, а второй выход - с третьим входом блока анализа, первый и второй выходы которого являются соответственно сигнальным и кодовым выходами устройства, четвертый вход блока анализа подключен к третьему управляющему входу второго коммутатора выходной информации и к выходу регистра номера продолжения, вход которого соединен с выходом третьего коммутатора выходной информации, информационный вход которого подключен к выходу блока памяти связности строк, вход ут1равления чтением которого соединен с выходом буферного регистра, а адресный вход - с выходом четвертого коммутатора адресов, второй вход которого соединен с выходом сумматора связности, а третий вход .с выходом адресного сумматора, с вторыми входами третьего и пятого коммутаторов адресов, выход которог подключен к адресному входу блока памяти замещения, информационный вход которого соединен с первым выходом блока замещения, выход блока памяти замещения соединен с вторым информационным входом блока замещения, второй выход которого подключен к второму информационному входу селектора, третий информационный вход которого соединен с выходом регистра номера сравнения, выход третьего ком мутатора адресов подключен к адресному входу блока памяти признаков действительности, выход буферного регистра адреса соединен с вторым входом второго коммутатора сшресов, с третьим входом третьего коммутатора адресов и с вторым входом сумматора связности, выход блока выработки приращения адреса преднакачки под ключен к входу второго слагаемого адресного сумг«1атора, управляющий вход блока выработки приращения адре са прзднакачки подключен к сигнальному входу устройства, выход элемента И соединен с вторым входом сумматора адреса строки, выход блока памяти адресов подключен к второму информационному входу блока сравнения адресов, выход которого соединен с входом шифратора, пятый вход блока анализа соединен с входом логического нуля устройства, второй вход блока выработки приращения адреса преднакачки соединен с сигнальным входом устройства. При этом блок анализа содержит дешифратор, две схемы сравнения, четыре элемента НЕ, четыре элемента И и элемент ИЛИ, выход которого подключен к первому выходу блока, входа элемента ИЛИ соединены соответственно с выходами элементов И, первые входы Которых соединены с выходом первого элемента НЕ, вход которого соединен с выходом первой схемы сравнения, второй вход первого элемента И соединен с выходом второго элемента НЕ, вход которого соединен с первым входом блока. Блок выработки приращения адреса йреднакачки содержит два элемен,та НЕ, два элемента И, дешифраi, тор и счетчик преднахачки, выход которого является выходом блока и соединен с входом дешифратора, а входа - соответственно с выходами элементов И, первые входы которых являются соответственно входом микрокоманд и входом переноса устройства, а вторые входы соединены с выходами элементов НЕ, входы которых соединены с входами дешифратора. Блок замещения содержит узел уче-та хронологии, узел формирования кандидата на замещение и регистр хронологии, зыход которого подключен к первому выходу блока, первый вход регистра хронологии соединен с выходом узла учета хронологии, а второй вход - с вторым информационным входом блока и с входом узла формирования кандидата на замещение, выход которого соединен с вторым выходом длока, входы узла учета хронологии подключены соответственно к первому информациолчному и к управляющему входам блока. Узел учета хронологии содер ит элемент НЕ и группу элементов И, причем первый вход узла соединен с первыми входами элементов И группы, выходы которых соединены с выходом узла, вторые входы первого, второго и последнего элементов И группы соединены через элемент НЕ с вторым входом узла, вторые входы остальных элементов И группы соединены с вторым входом узла. Узел формирования кандидата на з 1мещение содержит четыре элемента НЕ, три элемента И и элемент ИЛИ, причем вход блока через первый и второй элементы НЕ соединен с первыми входами первого и второго элементов И, вторые входы которых соответственно, соединены с входом узла непосредственно и через третий элемент НЕ, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого через четвертый элемент НЕ соединен с первым входом третьего элемента И,второй вход которого соединен с входом узла, выход которого соединен с выходами элемента ИЛИ и третьих элементов И и НЕ. На фиг. 1а и 16 представлена структурная схема устройства буферизации команд; на фиг. 2 - структурная схема блока анализа; на фиг.З структурная схема блока выработки приращения адреса преднакачки; на фиг. 4 - структурная схема блока сравнения адресов; на фиг. 5 - структурная схема блока замещения; на фиг. 6 - пример построения шифратора; на фиг. 7 - структурная схема селектора; на фиг. 8 - построение узла учета хронологии; на фиг. 9 построение узла формирования кандидата на замещение. Устройство буфе ризации команд (фиг. 1) содержит блок 1 памяти комг1ндных слов, группу входов 2 схемы сравнения, блок 3 памяти адресов, блок 4 памяти признаков действительности, блок 5 памяти связности строк (каждый из указанных блоков может в общем случае состоять из несколь.ких подблоков - столбцов, чтение из которых осуществляется одновременно, а запись может вестись в каждый момент времени только в один из них, называемый столбцом - кандидатом на замещение ), блок 6 памяти замещения, коммутаторы 7-11 адресов, элемент И 12, сумматор 13 адреса строки, сум матор 14 связности, б 4ферный регистр 15, буферный регистр 16 адреса, коммутаторы 17 и 18 выходной информации сдвигатель 19, регистр 20 команды, блок 21 анализа, блок 22 сравнения адресов, шифратор 23, регистр 24 номера сравнения, блок 25 замещения, селектор 26, коммутатор 27 выходной информации, регистр 28 номера столбца продолжения, блок 29 выработки приращения адреса преднакачки, адре ный сумматор 30, вход 31 микрокоманд устройства, сигнальный вход 32 устройства, адресный вход 33 устройств информационный вход 34 устройства, вход 35 адресного сумматора, адресный выход 36 устройства, выход 37 команды устройства, вход 38 блока анализа, вход 39 блока анализа, вход 40 блока анализа, сигнальный и кодо вый выходы 41.1 и 41.2 устройства. Блок 21 анализа (фиг. 2 содержи две схемы 42 сравнения, дешифратор 43, элементы КЕ 44, элементы И 45,; элемент ИЛИ 46. Блок 29 выработки приращения адреса преднакачки (фиг. 31 содержит элементы НЕ 47, элементы И 48, счет чик 49, дешифратор 50. Блок 22 сравнения адресов (фиг.4 содержит схемы 51 сравнения и элеме ты И 52. Блок 25 замещения (фиг. 5 содер жит узел 53 учета хронологии, узел 54 формирования кандидата на замеще ние и регистр 55 хронологии. Шифтатор 23 (фиг.6) содержит эле менты ИЛИ 56. Селектор 26 (фиг. 7) содержит эл менты И 57 и элемент ИЛИ 58, ; Уа.ел 53 учета хронологии (фиг. 8 содержит элементы НЕ 59, элементы К 60. Узел 54 формирования кандидата н замещение (фиг. 9) содержит элемент НЕ 61, элементы И 62 и элемент -ИЛИ 6 Рассмотрим работу устройства на примере выполнения команд типа прин тых в ЕС ЭВМ. Будем считать, что вы полняются команды формата RR длиной в 2 байта, не требующие обращения в 1лавную память за операндами, коман ды формата RX длиной в 4 байта и команды формата SS длиной в 6 байтов. Команды расположены в ячейках главной памяти в командных словах, каждое длиной в 8 байт. Выборка из главной памяти производится 8-байтными словами по 24-разрядному адресу (разрядность адреса 8-31, причем разряды 8-28 адресуют каждое слово, а разряды 29-31 (номер байта| адресуют тот номер байта в каждом слове,. в котором расположен старший байт. -команды. Если 29 р адреса равен нулю, то начало команды (старший байт ) расположено в старших четырех байтах командного слова, если 29 р адреса ра,вен единице, то Нс1чало команды расположено в младших четырех байтах командного слова. Адрес текущей команды, по тупающий на вход 33, вырабатывается на счетчике команд процессора . Будем считать, что выборка команды проводится в такте выборки команды, а выработка адреса следующей команды - в следующем такте - такте модификации адреса. Примем также, что каждый столбец блоков 1, 3, 4, 5 и 6 содержит 64 строки (ячейки и в каждом столбце блока 1 памяти командных слов располагается 8-байтовое командное слово. Обращение к блокам ведется по младшим разрядам адреса команды. Устройство работает следующим образом. в такте выборки команды производится обращение к блокам 1, 3, 4, 5 памяти по адресу текущей команды (адресный вход 33 /. В блоке 3 памяти адресов записаны старшие разряды адреса командного слова, в блоке 4 памяти признаков действительности - признаки действительности, в блоке 5 памяти связности - номер столбца блока 1, в котором находится продолжение данной командной последовательности. Если в блоке 5 памяти связности записана информация, не равная нулю, это означает, что продолжение команды имеется в блоке 1. Каждый столбец блока 1 памяти ко-. мандных слов представлен в виде двух секций. Первая секция содержит старшие 4 байта командного слова, втораямладшие 4 байта. Обращение к второй секции ведется по адресу с выхода первого KOMiviyTaTopa 7 адресов, обращение к первой секции - по адресу с выхода сумматора 13, который при выборке команды суммирует значение адреса с выхода коммутатора 7 со значением 29 р адреса текущей команды. Если вся команда расположена в одной строке блока 1, то адреса обращения к обеим секциям одинаковы, если начало команды расположено во второй секции, то младшая часть команды будет сосчитана из следующей строки блока 1. При чтении команды из блока 1 восемь байтов командной информации поступают на входы коммутаторов 17 и 18. Одновременно из блока 3 памяти адресов, блока 4 памяти признаков действительности, блока 5 Пс1мяти связности считываются по тому же адресу через коммутаторы 8, 9 и 10 адресов соответственно старшие части адреса командного слова, признаки действительности и признак или номер столбца продолжения. На схемах 51 сравнения все сосчитанные из блока 3 памяти адресов адреса сравниваются со старшей частью адреса выбираемой команды с учетом признака действительности на элементах И 52. Искомая команда (начало ее )находится в том (же столбце, в котором обнаружено сравнение. Номер сравнения формирует ся на шифраторе 23. Значение номера сравнения, равно нулю, указывает на то, что в блоке 1 требуемой команды не обнаружено. Аналогично, значение номера продолжения, равное нулю,уна зывает на то, что продолжения данной командной последовательности в блоке 1 нет. По номеру сравнения пр изводится управление коммутатором 17 выходной информации младших четы рех байт командной информации,в которых находится либо конец команды,если 29 р адреса текущей команды равен нулю либо ее начало, если 29 р адреса равен единице. Управление коммутатором 18 старших четырех байт информации производится по номеру 39 сравнения, если 29 р адреса текущей команды равен нулю, или по номеру 40 продолжения, если 29 р адреса равен единице. Сфор мированное на выходах коммутаторов 17 и 18 командное слово поступает на сдвигатель 19, на котором осущест вляется сдвиг влево входного командного слова кодом младших разрядов адреса команды так, что на выходе сдвигателя 19 команда выравнивается по своему старшему разряду. Сформированная таким образом команда поступает на регистр 20 команды и далее с его выхода 37 в процессор на выполнение блока 1. Выходная информация блока 5 посту пает на вход коммутатора 27 выходной информации, управление которым производится по номеру 39 сравнения. Выходная информация коммутатора 27 запоминается на регистре 28 номера столбца продолжения. Номер 39 сравнения поступает на блок 21 анализа нахождения команды в блоке 1. На другие входы этого блока поступают старшие дна разряда команды, сформиоованной на выходе сдвигателя 19, формат команды 38, номер 40 продолжения, младшие разряды адреса команды. На выходе 41.1 формируется сигнал, указывающий, что вся команда находится в блоке 1. На выходе 41.2 формируется сигнал, если информация по данному адресу находится в блоке 1. Если блок 21 aHajfti3a указывает на отсутствие команды в блоке 1 памяти командных слов, то производится процедура накидки требуемого командного слова в блок 1 командных слов из оперативной памяти.. При этом осуществляются соответствующие записи адреса командного слова в блок 3 памяти адресов и признаков действительности и продолжения в блоки 4 и 5 памяти. Накачка блока 1 новым командным словом возможна как при отсутствии требуемой команды в блоке 1, так и заблаговременно. Заблаговременная накачка блока 1 носит название преднакачки и осуществляется в те моменты времени, когда адресный и информационный тракты и оборудование процессора свободны от обращения в главную память за операндами. Как правило, это те моменты времени, когда процессор выполняет команды RR-формата, или моменты, когда процессор из-за конфликтов, возникающих при совмещенном выполнении команд, не может начать выполнение следующей команды, пока не выполнится предыдущая команда. Адрес очередного командного слова, накачиваемого в блок 1 памяти командных слов при преднакачке, формируется на выходе адресного сумматора 30 сложением адреса текущей команды команд со значением счетчика 49 преднакачки и единицы. Значение счетчика 49 всегда показывает разницу в двойных словах между адресом командного слова текущей команды и адресом последнего слова, накаченного в блок 1 памяти командных слов. Если начала требуемой коман.цы нет в блоке 1, то значение счетчика 49 равно нулю и прибавление единицы не производится. Счетчик 49 увеличивает свое содержимое на единицу всякий раз, когда произведена запись очередного командного слова в блок 1 п&мяти командных слов. Из счетчика 49 преднакачки вычитается единица всякий раз, когда при формировании адреса следующей команды возникает перенос. По достижении счетчиком 49 преднакачки максимального значения преднакачки, которое выбирается меньше максимального количества командных слов, помещаемых в блок 1, дальнейшие попытки преднакачки приостанавливаются до тех пор, пока значение рчетчика 49 яе уменьшится, Это предотвращает порчу информации в блоке 1 в случае такого количества преднакачек, когда блок 1 может переполниться при преднакачках и последнее принятое командное слово может затереть в бло ке 1 ячейку, в которой находится очередная для выполнения команда, С другой стороны, значение счетчика 49 преднакачки может уменьшаться только до нуля. Для обеспечения этих условий служат дешифратор 50 состояний счетчика 49, равных нулю, и состояний, равных v (где V величина максимальной предварительной накачки) и элементы НЕ 47. Сигналы прибавления +1 и вычитания -1 к значению счетчика 49 вырабатываются С выходов соответствующих элементов И 48. При предварительной накачке очередного командного слова в блок 1 производится проверка наличия этого командного слова в блоке 1 Для этого по адресу, поступающему на адресные входы блока 3 памяти адресов , блока 4 признаков действитель ности через коммутаторы 8 и 9 производится считывание из блоков 3 и 4 памяти и анализ на схемах 51 сравне ния наличия командного слова в блоке 1. Если командное слово находится в блоке 1, то делается только отметка о продолжении в предыдущей строке блока памяти 5 связности, Есл. исе командного слова не обнаружено f то старшие разряды его адреса записываются в блок памяти адресов по линии 36 по адресу через коммутатор 8 в столбец, номер которого на основании информации хронологии опре деляется блоком 25 замещения, на вход которого поступает информация, считанная из блока 5 памяти замещения по адресу, поступающему через коммутатор 11. Кандидатом на замещение выбирается тот столбец, информация которого наиболее долго не требо валась до текущего момента. При каждой выборке коман,цы из блока 1 в так те. выборки команды, если она указы™ Всхется в блоке памяти командных слов в соответствующую ячейку блока б памкти замещения записывается информация .хронологии обращения, определяемая на основании номера 39 сравнения и предыдущего, содержания этой: ячейки блока 6 памяти замещения. При очередном обращении к бпоку командных слов из блока б памяти замещения считывается информация в регистр 55 хронологии. Затем, если обнаружено сравнение в одном из столбцов, то узел 53 вырабатывает сигналы изменяющие состояние определенных бит регистра 55 хронологии. Биты регистра 55 хронологии изменяются под непосредственным управлением битов номера 39 сравнения. После модификации регистра 55 хронологии его содержимое запоминается в блоке 6 памяти замещения по адресу той же ячейки. В случае, если сравнение не обнаружено ни в одном из столбцов, номер кандидата на замещение определяется узлом 54. Узел 54 формирует биты номера столбца канддидата на замещение таким образом, что этот номер с наибольшей вероятностью не равен ближайшим по времени использования, в которых было обнаружено сравнение. , В процедуре предварительной накач- ки значение, считанное по адресу оуередного командного слова из блока 6 памяти замещения, определяет номер столбца блоков 3, 5, 4, 1 памяти для записи в них соответственно старших разрядов адреса командного слова, признаков действительности и связности и командного слова. Прием нового командного слова ведется в выбранный столбец блока по адресу командного слова, поступающему через коммутатор 7 адресов с выхода буферного регистра 16. Одновременно по этому же адресу через коммутатор 9 адресов в блоке 4 записывается признак действительности, равный единице, а в предыдущей строке 5лока 5 памяти связности по адресу, поступающему на вход блока 5 памяти связности строк через сумматор 14 связности и коммутатор 10 адресов строк, в столбце, номер которого указан буферным регистром 15 связности, делается отметка о продолжении, т.е. записывается номер столбца блока 1, в который б1Л1Ю принято это новое командное слово. Этот же номер заносится затем на буферный регистр 15. 3 буферный регистр 15 может быть записан также номер 39 сравнения, если команды находятся в блоке 1, а возможности преднакачки нет, нЪмер 39 сравнения, определенный в процедуре преднакачки, или состояние буферного регистра 24, который хранит номер сравнения команды передачи .управления до момента возврата к старой ветви в случае неуспешного перехода. При выполнении команды передачи управления модифицированный адрес команды новой ветви выступает в качестве адреса очередной команды, по которому неме,цленно ведется обращение к блокам 1, 3, 4, 5. Если команда новой ветви находится в блоке, то потери времени на выборку команды минимальны. Если команды новой ветви нет в блоке 1, ведется накачка требуемого командного слова этой новой ветви в блок 1 по адресу команды новой ветви. При этом во всех столбцах блока 5 памяти связности по адресу предыдущей строки сбрасываются признаки (номера) продолжения, т.е.- связность командных слов расположенных смежно в блоке 1, но имеющих разные части адресов, разру шается. Связность командных слов вновь устанавливается только после приема первого командного слова из новой ветви. Повышение эффективности использования предлагаемого устройства бу феризации команд достигается тем, J/ 32 33 yt4,«//

(рив. la что при каждом переходе в буфере разрушается не вся информация, а лишь некоторая ее часть,заполняемая новым программным циклом. Это повышает вероятность обнаружения команды новой ветви в буфере команд. Кроме того, обеспечивается выборка команды за один машинный такт независимо от расположения ее в командном слове. Применение изобретения позволяет повысить быстродействие устройства.

фи. 10

;

Iff

Вп

б/

0/

м

ра

oz

ff26

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПАШИНО-ТЕХНН'-'Р'^Н.АЯБИБЛИОТЕКА | 0 |

|

SU301703A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ПРИБОР ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ И ДЛЯ НАХОЖДЕНИЯ КОРНЕЙ ЧИСЛЕННЫХ УРАВНЕНИЙ | 1924 |

|

SU1045A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1984-05-15—Публикация

1983-01-12—Подача