формационных входов первого селектора входной- информации устройства, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит два регистра выходной информации, второй селектор входной информации устройства, сумматор, формирователь маркера второго операнда, два селектора входной информации памяти и селектор микрокоманд, причем второй, третий и четвертый входы микрокоманд уровней соЬмещения операций устройства соединены соответственно с первым, вторым и третьим информационными входами селектора микрокоманд, первый выход которого соединен с управляющими входами первого селектора адреса памяти и первого селектора входной информации памяти и с входами записи-чтения первого блока памяти и первого регистра выходной информации, второй выход селектора микрокоманд соединен с управляющими входами второго селектора входной информации памяти, второго селектора адреса памяти, с вторым управляющим входом блока обнаружения конфликтов и с входами записичтения второго блока памяти второго регистра выходной информации, информационный вход которого соединен с выходом селектора выходной информации памяти, первый и второй информационные входы первой группы устройства соединены соответ ственно с первыми информационными входами первого и второго селекторов входной информации памяти, вторые информационные входы которых соединены с выходом входного регистра, третьи информационные входы первого и второго селекторов входной информации памяти соединены с вторым входом блока коррекции второго операнда и с выходом второго селектора входной информации устройства, информационный вход которого соединен с выходом первого селектора входной информации устройства, выходы первого и второго селекторов входной информации памяти соединены соответственно с информационными входами первого и второго блоков памяти, третий выход се- лектора микрокоманд соединен с управляющим входом первого селектора входной информации устройства, с первыми входами сумматора и формирователя маркера второго операнда, с входом чтения-записи регистра первого операнда, первый информационный вход первой группы устройства соединен с вторыми входами сумматора и формирователя маркера второго операнда, выходы которых соединены соответственно с управляющим входом второго селектора входной информации устройства и с входом чтения-записи регистра второго операнда, выходы первого регистра выходной информации соединены с информационными входами третьей группы первого селектора входной информации устройства и являются информационными выходами группы

устройства, выход второго регистра выходной информации соединен с вторым входом блока коррекции первого операнда и является информационным выходом группы устройства.

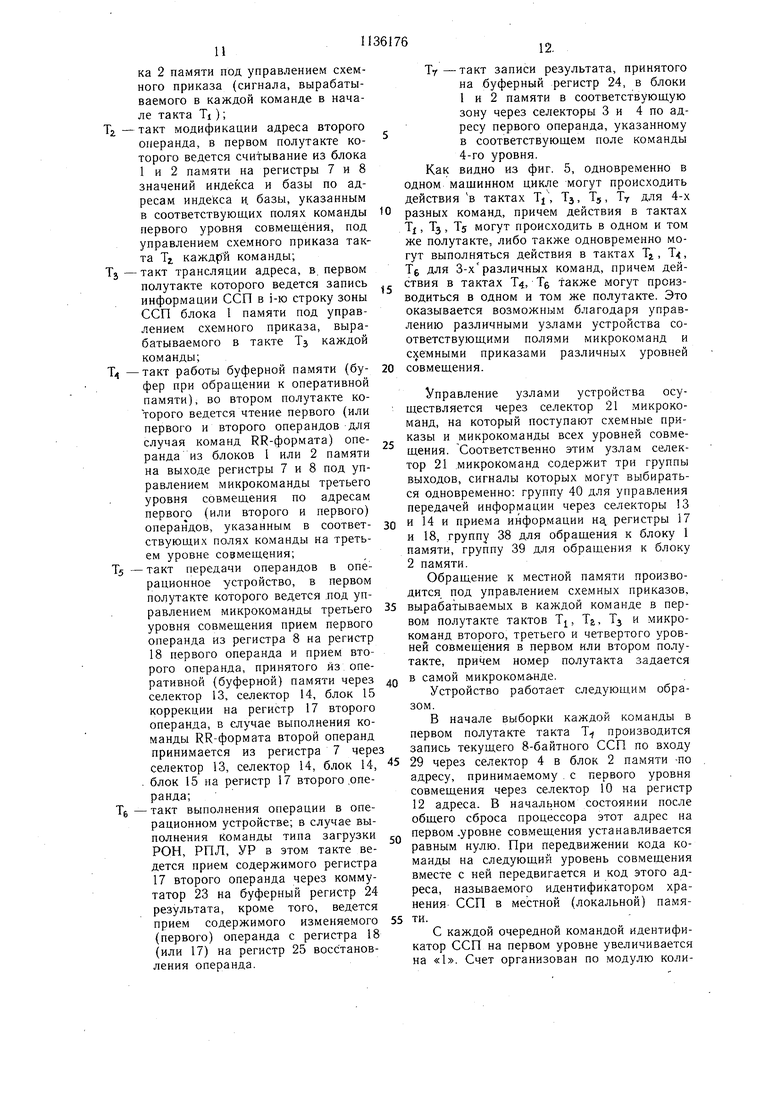

2. Устройство по п. 1, отличающееся тем, что блок обнаружения конфликтов содержит два регистра адресов чтения операнда, две схемы сравнения адресов, две схемы сравнения младщего разряда адресов, восемь элементов И и четыре элемента ИЛИ, причем третий и второй информационные входы блока соединены соответственно с информационными входами первого и второго регистров адресов чтения операнда, выходы старших разрядов адресов операнда KOTopbix соединены соответственно с первыми входами первой и второй схем сравнения адресов, выходы младщего разряда адресов операнда первого и второго регистров адресов чтения операнда соединены соответственно с первыми входами первой и второй схем сравнения младщего разряда адресов, вторые входы которых соединены с первыми входами первого и второго элементов И, с вторыми входами первой и второй схем сравнения младщего разряда адресов и являются первым информационным входом блока, управляюпхий вход блока соединен с первыми входами третьего, четвертого, пятого и шестого элементов И, вторые входы первого, третьего и четвертого элементов И соединены с первым входом седьмого элемента И и с выходом первой схемы сравнения адресов, вторые входы второго, пятого и щестого элементов И соединены с первым входом восьмого элемента И и с выходом второй схемы сравнения адресов, выходы первой и второй схем сравнения младщего разряда адресов соединены соответственно с вторыми входами седьмого и восьмого элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы четвертого и седьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ и выход первой схемы сравнения младщего разряда адресов образуют первую группу выходов блока, выходы второго и пятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы щестого и восьмого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ и выход второй схемы управления младшего разряда адресов образуют вторую группу выходов блока.

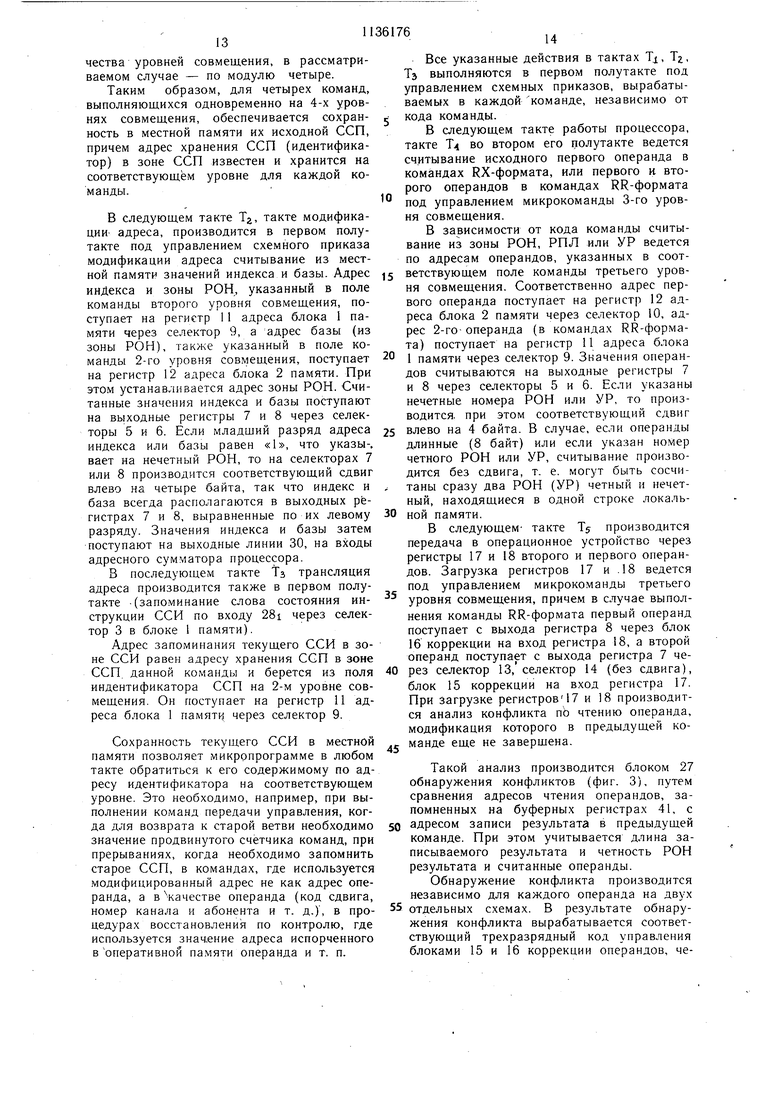

3. Устройство по п. 1, отличающееся тем, что каждый из блоков коррекции первого

операнда и коррекции второго операнда содержит три элемента НЕ, восемь элементов И и четыре элемента ИЛИ, причем первый вход блока соединен с первыми входами первого, второго, третьего и четвертого элементов И, управляющий вход блока соединен с входами первого, второго и третьего элементов НЕ и с вторыми входами первого и третьего элементов И и с первыми входами пятого и шестого элементов И, выход первого элемента НЕ соединен с вторыми входами второго и четвертого элементов И, выход второго элемента НЕ соединен с первым входом седьмого элемента И, выход третьего элемента НЕ соединен с первым входом восьмого элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами Btoporo элемента ИЛИ, выход которого соединен с вторым входом

шестого элемента И, второй вход блока соединен с вторыми входами седьмого и восьмого элементов И, выходы пятого и седьмого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы шестого и восьмого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход блока образован выходами третьего и четвертого элементов ИЛИ.

4. Устройство по п. 1, отличающееся тем, что формирователь маркера второго операнда содержит память констант маркера и селектор выходной )ормации, причем управляюш,ий вход селектора выходной информации соединен с входом чтения памяти констант маркера и является первым входом формирователя, выход памяти констант маркера соединен с информационным входом селектора выходной информации, выход которого является выходом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Процессор с реконфигурацией | 1979 |

|

SU798853A1 |

| Микропрограммное устройство управления | 1980 |

|

SU940158A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство микропрограммного управления | 1980 |

|

SU942020A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПАМЯТИ С ПРОЦЕССОРОМ, содержащее входной коммутатор, два блока памяти, два селектора выходной информации памяти, входной регистр., два селектора адреса памяти, два регистра адреса памяти, блок коррекции первого операнда, блок ррекции второго операнда, блок обнаружения конфликтов, регистр первого операнда, регистр второго операнда, регистр восстановления операнда и первый селектор входной информации устройства, причем первый информационный вход входного коммутатора является первым информационным входом устройства, второй информационный вход входного коммутатора соединен с первым информационным входом регистра восстановления операнда, с выходом регистра второго операнда и явл-яется информационным выходом второго операнда устройства, первый вход микрокоманд уровней совмещения операций устройства соединен с управляющим входом входного коммутатора и с входом записи-чтения входного регистра, информационный вход которого соединен с выходом входного коммутатора, выход входного регистра соединен с первыми входами блока коррекции первого операнда и блока коррекции второго операнда, первый, второй и третий адресные входы уровней совмещения устройства соединены соответственно с первыми, вторыми и третьими информационными входами первого и второго селекторов адреса памяти, четвертые информационные входы которых соединены с первым информационным входом блока обнаружения конфликтов и с четвертым адресным входом уровней совмещения устройства, выходы первого и второго селекторов адреса памяти соединены соответственно с информационными входами первого и второго регистров адреса памяти, выход первого регистра памяти соединен с управляющим в.ходом первого селектора выходной информации памяти, адресным входом первого блока памяти и с вторым информационным входом блока обнаружения конфликтов, третий информационный вход которого соединен с i выходом второго регистра адреса памяти, с адресным входом второго блока памяти и с (О управляющим входом второго селектора выходной информации памяти, выходы первого и второго блоков памяти соединены соответственно с информационными входами первого и второго селекторов выходной информации памяти, группы управляющих входов блока коррекции первого операнда и блока коррекции второго операнда соединены соответственно с первой и второй групсо пами выходов блока обнаружения конфликО5 тов, выходы блока коррекции второго операнда и блока коррекции первого операйда соединены соответственно с информацион ными входами регистра второго операнда О) и регистра первого операнда, выход которого соединен с вторым информационным входом регистра восстановления операнда и является информационным выходом первого операнда устройства, первый, второй и третий информационные входы второй группы устройства соединены соответственно с первым, вторым и третьим информационными входами первой группы первого селектора входной информации устройства, группа выходов регистра восстановления операнда соединена с второй группой ин

1

Изобр етение относится к вычислительной технике и предназначено для работы в центральном процессоре быстродействуюш,их ЭВМ с п уровнями совмещения выполнения команд (п - конечное число уровней совмещения выполнения команд).

Известно устройство сопряжения местной (локальной) памяти с процессором для хранения данных процессора и блока восстановления и диагностики, которое содержит схемы информационного тракта, схемы раздельной адресации для режимов чтения и записи, схемы управления и накопитель 1.

Недостатком устройства является его относительно низкое быстродействие, так как в одном машинном такте оно позволяет либо считать одно слово, либо записать одно слово, хотя операции чтения и записи могут быть заданы одновременно.

В процессорах большой производительности 2 местная память применяется. только для хранения регистров общего назначения (РОН) и регистров плавающей точки. (РПЛ), причем построена она на оперативных регистрах с целью быстрого считывания сразу двух исходных операндов, что требует двух независимых схем обращения к этой памяти и занимает большое количество оборудования.

Информация промежуточных результатов, информация для восстановления по

сбою хранится также на оперативных регистрах, причем требуются свои, собственные пути доступа этой информации к устройству оперативной памяти и арифметическому устройству. Это также усложняет и увеличивает аппаратуру процессора.

Наиболее близким к предлагае.мому по технической сущности является устройство,

содержащее входной коммутатор, два блока памяти, два селектора выходной информации памяти, входной регистр, два селектора адреса памяти, два регистра адреса памяти, блок коррекции первого операнда, блок коррекции второго операнда, блок обнаружения конфликтов, регистр первого операнда, регистр второго операнда, регистр восстановления операнда и первый селектор входной информации, устройства, причем первый информационный вход входного коммутатора является первым информационным входом устройства, второй информационный вход входного коммутатора соединен с первым информационным входом регистра восстановления операнда, с выходом регистра второго операнда и является

информационным выходом второго операнда устройства, первый вход микрокоманд уровней совмещения операций устройства соединен с управляющим в.ходом входного коммутатора и с входом записи-чтения входного регистра, информационный вход которого соединен с выходом входного коммутатора, выход входного регистра соединен с первыми входами блока коррекции первого операнда и блока коррекции второго операнда, первый, второй и третий адресные входы уровней совмещения устройства соединены соответственно с первыми, вторыми и третьими информационными входами первого и второго селекторов адреса памяти, четвертые информационные входы которых соединены с первым информационным входом блока обнаружения конфликтов и с четвертым адресным входом уровней совмещения устройства, выходы первого и второго селекторов адреса памяти соединены соответственно с информационными входами первого и второго регистров адреса памяти, выход первого регистра адреса памяти соединен о управляющим входом первого селектора выходной информации памяти, адресным входом первого блока памяти и с вторым информационным входом блока обнаружения конфликтов, третий информационный вход которого соединен с выходом второго регистра адреса памяти, с адресным входом второго блока памяти и с управляющим входом второго селектора выходной информации памяти, выходы первого и второго блоков памяти соединены соответственно с информационными входами первого и второго селектороэ выходной информации памяти, группы управляющих входов блока коррекции первого операнда и блока коррекции второго операнда соединены соответственно с первой и второй группами выходов блока обнаружения конфликтов, выходы блока коррекции второго операнда и блока коррекции первого операнда соединены соответственно с информационными входами регистров второго операнда и регистра первого операнда, выход которого соединен с вторым информационным входом регистра восстановления операнда и является информационным выходом первого операнда устройства , первый, второй и третий информационные входы второй группы устройства соединены соответственно с первым, вторым и третьим информационными входами первой группы первого селектора входной информации устройства, группа выходов регистра восстановления операнда соединена с второй группой информационных входов первого селектора входной информации устройства 3.

Устройство позволяет в одном машинном цикле считать два различных слова, однако запись результата ведется всегда по одинаковому адресу в обе памяти одновременно.

Недостатком известного устройства является то, что в обе памяти возможна запись только одинакового содержания, не предусмотрена возможность сохранения в этой памяти информации восстановления

для нескольких команд, выполняющихся с совмещением, управление памяти возможно только от одной микрокоманды, отсутствует возможность формирования операнда в случае нецелочисленной границы его

расположения в оперативной памяти, нет возможности считывания и модификации операнда в местной памяти путем сдвига в одном и том же машинном цикле, что в итоге снижает быстродействие процессора

и приводит к недоиспользованию имеющегося объема местной памяти.

Целью изобретения является увеличение быстродействия устройства по записичтению данных в местной памяти процессора с несколькими уровнями совмещения.

Поставленная цель достигается тем, что в устройство для сопряжения памяти с процессором, содержащее входной коммутатор, два блока памяти, два селектора выQ ходной информации памяти, входной регистр, два селектора адреса памяти, два регистра адреса памяти, блок коррекции первого операнда, блок коррекции второго операнда, блок обнаружения конфликтов, регистр первого операнда, регистр второго

операнда, регистр восстановления операнда и первый селектор входной информации устройства, причем первый информационный вход входного коммутатора является первым информационным входом устройства, второй информационный вход входного коммутатора соединен с первым информационным входом регистра восстановления операнда, с выходом регистра второго операнда и является информационным выходом второго операнда устройства, первый

г вход микрокоманд уровней совмещения операций устройства соединен с управляющим входом входного коммутатора и с входом записи-чтения входного регистра, информационный вход которого соединен с выходом входного коммутатора, выход входного регистра соединен с первыми входами блока коррекции первого операнда и блока коррекции второго операнда, первый, второй и третий адресные входы уровней совмещения устройства соединены соответственно с первыми, вторыми и третьими информационными входами первого и второго селекторов адреса памяти, четвертые информационные входы которых соединены с первым информационным входом блока обнаружения конфликтов и с четвертым

0 адресным входом уровней совмещения устройства, выходы первого и второго селекторов адреса памяти соединены соответственно с информационными входами первого и второго регистров адреса памяти, выход первого регистра адреса памяти соединен с

5 управляющим входом первого селектора выходной информации памяти, адресным входом первого блока памяти и с вторым информационным входом блока обнаружения конфликтов, третий информационный вход которого соединен с выходом второго регистра адреса памяти, с адресным входом блока памяти и с управляющим входом второго селектора выходной информации памяти, выходы первого и второго блоков памяти соединены соответственно с информационными входами первого и второго селекторов выходной информации памяти, группы управляющих входов блока коррекции первог.о операнда и блока коррекции второго операнда соединены соответственно с первой и второй группами выходов блока обнаружения конфликтов, выходы блока коррекции второго операнда и блока коррекции первого операнда соединены соответственно с информационными входами регистра второго операнда и регистра первого операнда, выход которого соединен с вторым информационным входом регистра восстановления операнда и является информационным выходом первого операнда устройства, первый, второй и третий информационные входы второй группы устройства соединены соответственно с первым, вторым и третьим информационными входами первой группы первого селектора входной информации устройства, группа выходов регистра восстановления операнда соединена с второй группой информационных входов первого селектора входной информации устройства, введены дополнительно два регистра выходной информации, второй селектор входной информации устройства, сумматор, формирователь, маркера второго операнда, два селектора входной информации памяти и селектор, микрокоманд, причем второй, третий и четвертый входы микрокоманд уровней совмещения операций устройства соединены соответственно . с первым, вторым и третьим информационными входами селектора микрокоманд, первый выход которого соединен с управляющими входами первого селектора адреса памяти и первого селектора входной информации памяти и с входами записи-чтения первого блока памяти и первого регистра выходной информации, второй выход селектора микрокоманд соединен с управляющими входами второго селектора входной информации памяти, второго селектора адреса памяти, с вторым управляющим входом блока обнаружения конфликтов и с входами записи-чтения второго блока памяти и. второго регистра выходной

информации, информационный вход которого соединен с выходом второго селектора выходной информации памяти, первый и второй информационные входы первой группы устройства соединены соответственно с первыми информационными входами первого и второго селекторов входной информации памяти, вторые информационные входы которых соединены с выходом входного регистра, третьи информационные

входы первого и второго селекторов входной информации памяти соединены с вторым входом блока коррекции второго операнда и с выходом второго селектора входной информации устройства, информационный вход которого соединен с выходом первого селектора входной информации устройства, выходы первого и второго селекторов входной информации памяти соединены соответственно с информационными входами первого и второго блоков памяти, третий выход селектора микрокоманд соединен с управляющим входом первого селектора входной информации устройства, с первыми входами сумматора и формирователя маркера второго операнда, с входом чтения-записи регистра первого операнда, первый информационный вход первой группы устройства соединен с вторыми входами сумматора и формирователя маркера второго операнда, выходы которых соединены соответственно с управляющим входом второго селектора входной информации устройства и с входом чтения-записи регистра второго операнда, выходы первого регистра выходной информации соединены с информационными входами третьей группы первого селектора входной информации устройства и являются информационными вь1ходами группы устройства, выход второго регистра выходной информации соединен с вторым входом блока коррекции первого операнда и является информационным выходом группы устройства.

Блок обнаружения конфликтов содержит два регистра адресов чтения операнда, две схемы сравнения адресов, две схемы сравнения младшего разряда адресов, восемь элементов И и четыре элемента ИЛИ, причем третий и второй информационные входы блока соединены соответственно с информационными входами первого и второго регистров адресов чтения операнда, выходы старщих разрядов адресов операнда которых соединены соответственно с первыми входами первой и в1-орой схем сравнения адресов, выходы младщего разряда . адресов операнда первого и второго регистров адресов чтения операнда соединены соответственно с первыми входами первой и второй схем сравнения младщего разряда адресов, вторые входы которьгх соединены с первыми входами первого и второго элементов И, с вторыми входами первой и второй схем сравнения младщего разряда адресов и является первым информационным входом блока, управляющий вход блока соединен с первыми входами третьего, четвертого, пятого и щестого элементов И, вторые входы первого, третьего и четвертого элементов И соединены с первым входом седьмого элемента И и с выходом первой схемы сравнения адресов, вторые входы второго, пятого и щестого элементов И coeдиJ eны с первым входом восьмого элемента И и с выходом

второй схемы сравнения адресов, выходы первой и второй схем сравнения младшего разряда адресов соединены соответственно с вторыми входами седьмого и восьмого элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы четвертого и седьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ и выход первой схемы сравнения младшего разряда адресов рбразуют первую группу выходов блока, выходы второго и пятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы шестого и восьмого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ и выход второй схемы управления младшего разряда адресов образуют вторую группу выходов блока.

Каждый из блоков коррекции первого операнда и коррекции второго операнда содержит три элемента НЕ, восемь элементов И и четыре элемента ИЛИ, причем первый вход блока соединен с первыми входами первого, второго, третьего и четвертого элементов И, управляющий вход блока соединен с входами первого, второго и третьего элементов НЕ и с вторыми входами первого и третьего элементов И и с первыми входами пятого и шестого элементов И, выход первого элемента НЕ соединен с вторыми входами второго и четвертого элементов И, выход второго элемента НЕ соединен с первым входом седьмого элемента И, выход третьего элемента НЕ соединен с первым входом восьмого элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с вторым входом шестого элемента И, второй вход блока соединен с вторыми входами седьмого и восьмого элементов И, выходы пятого и седьмого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы шестого и восьмого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход блока образован выходами третьего и четвертого элементов ИЛИ.

Формирователь маркера второго операнда содержит память констант маркера и селектор выходной информации, причем , уирачляющий вход селектора выходной инфор 1;пьии соединен с входом чтения памяти

констант маркера и является первым входом формирователя, выход памяти констант маркера соединен с информационным входом селектора выходной информации,

выход которого является выходом формирователя.

Устройство предназначено для приема, хранения, модификации и выдачи (в процессе выполнения команд с совмещением one раций) значений РОН, РПЛ, копий управляющих регистров (УР), копий префикса, копий исходных ССП (слово состояния программы) и ССИ (слово состояния инструкции) для .каждой из одновременно выполняющихся команд, исходных операндов в

командах плавающей точки с повышенной точностью, исходных операндов в командах десятичной арифметики, начальных, текущих и конечных адресов операндов в командах SS-формата, различных констант, начальных адресов таблиц сегментов для

15 задач, идентификатора процессора. Устройство воспринимает для буферного хранения состояние всех основных регистров процессора и информацию оперативной памяти и выдает исходные данные, операнды

в операционные устройства через регистры первого и второго операндов длиной 8 байт. Выходы регистра второго операнда являются основной внутренней загрузочной информационной магистралью процессора, через которую осуществляется выдача информации

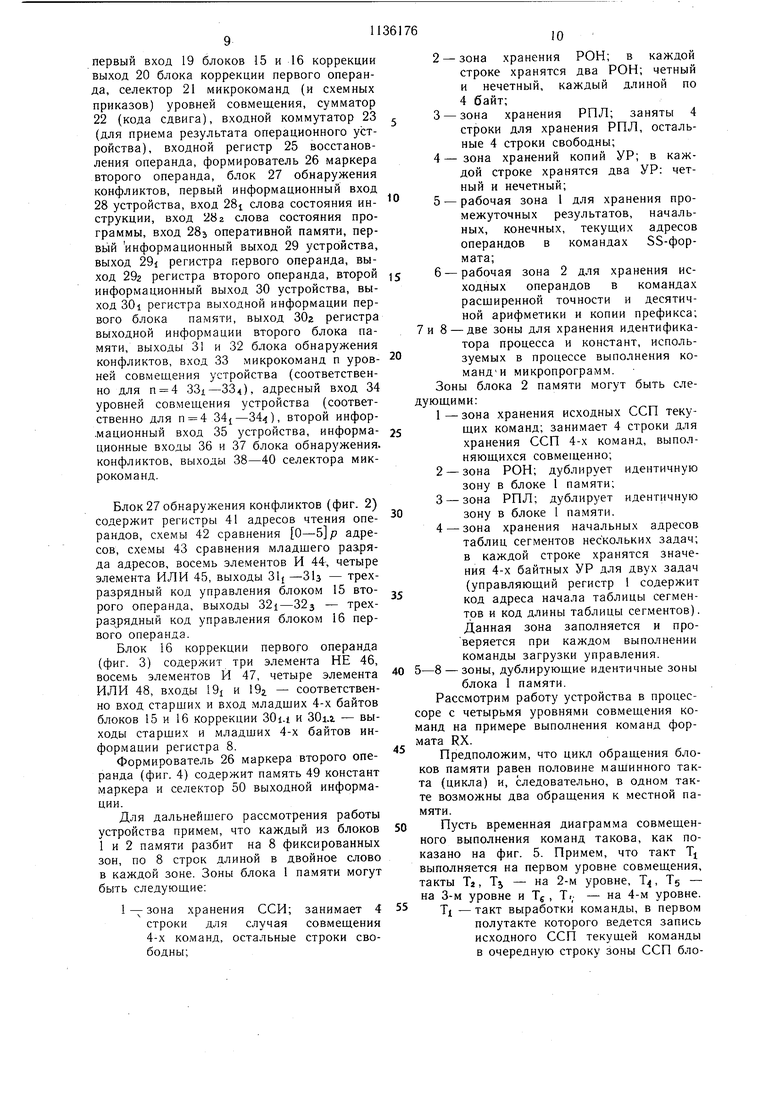

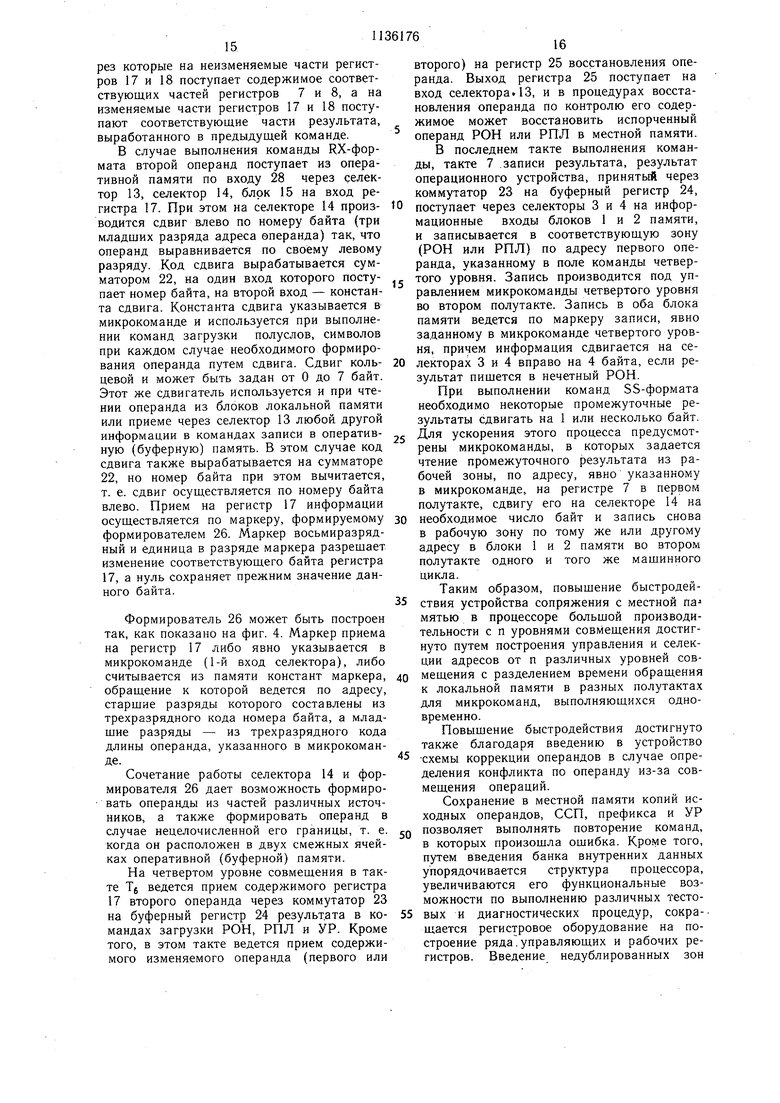

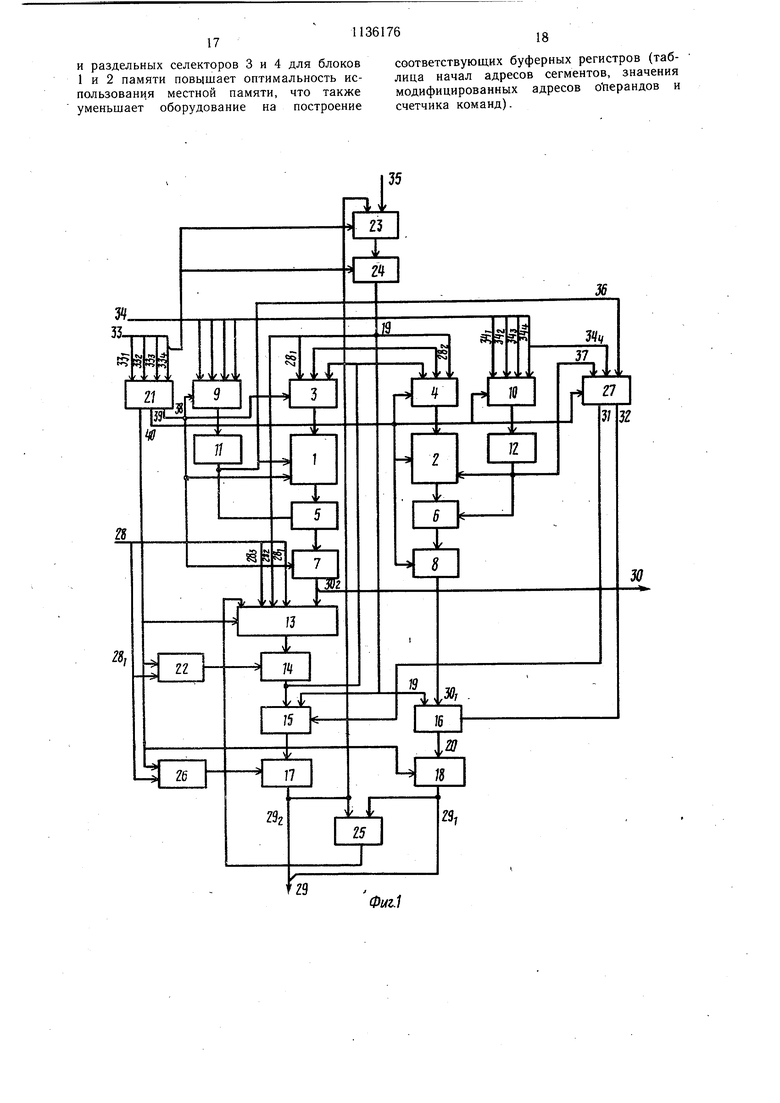

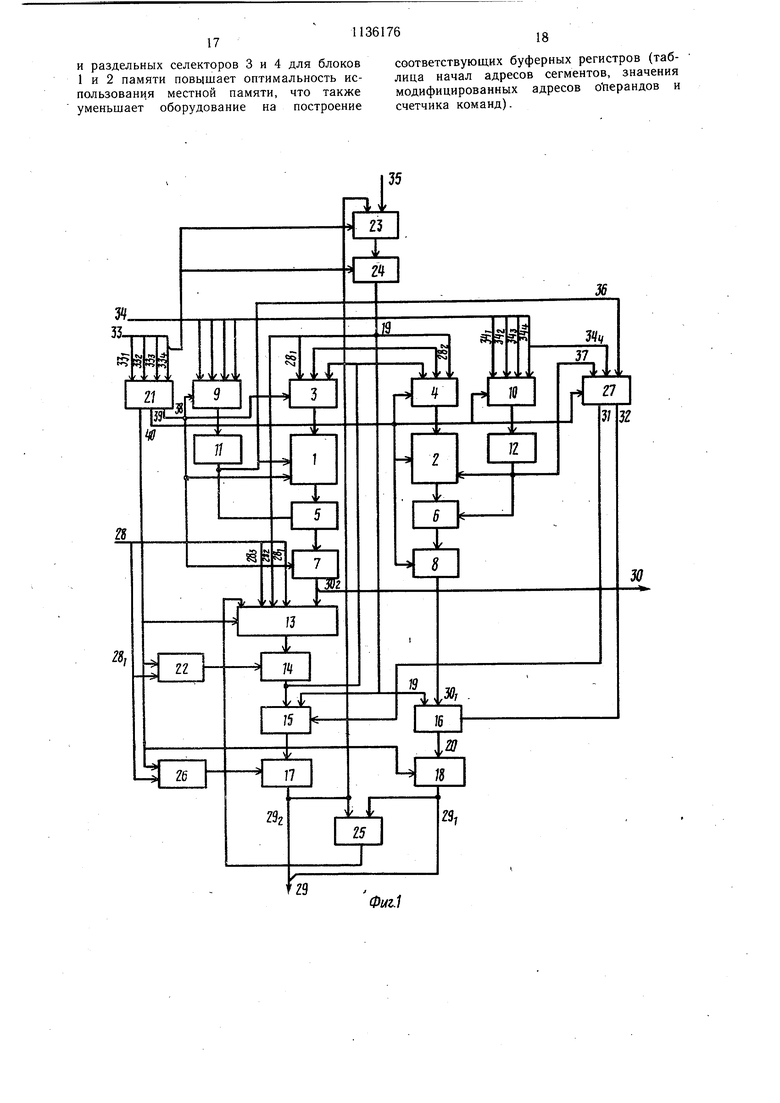

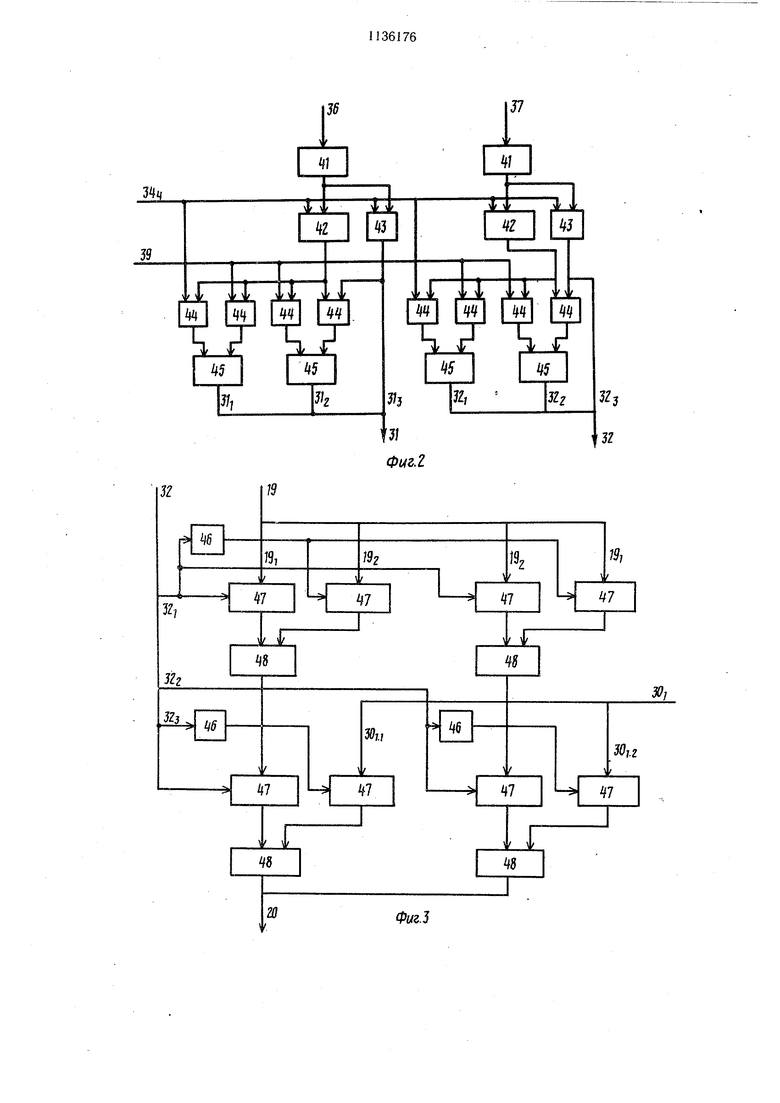

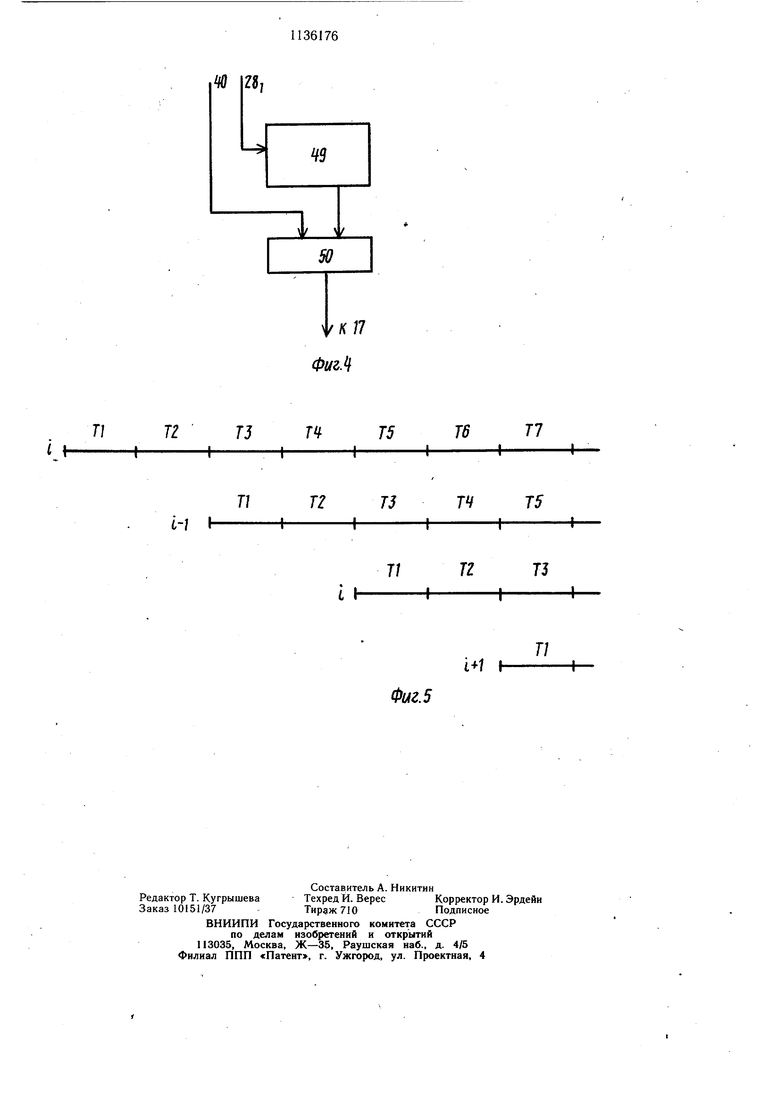

в оперативную память, а также загрузка всех оперативных регистров процессора (регистра ССП, регистра префикса, регистров управления, блока таймеров и т. п.). На фиг. 1 представлена структурная схема устройства сопряжения местной памяти с процессором; на фиг. 2 - структурная схема блока обнаружения конфликтов устройства; на фиг. 3 - структурная схема блока корреции первого операнда (структурная схема блока коррекции второго операнда

идентична); на фиг. 4 - структурная схема формирователя маркера второго операнда устройства; на фиг. 5 - временная диаграмма сов.мещенного выполнения команд.

Устройство сопряжения местной па.мяти с процессором содержит блоки 1 и 2 памяти (собственно местная память, каждый блок которой в частном случае имеет 64 строки

по 8 байт), селекторы 3 и 4 входной информации памяти, два селектора 5 и 6 выходной информации памяти, регистры 7 и 8 выходной информации памяти, селекторы 9 и 10 адресов памяти, регистры 11 и 12 адресов памяти, селектор 13 входной информации устройства, второй селектор 14 входной информации, блоки 15 и 16 коррекции второго и первого операндов, регистры- 17 и 18 второго и первого операндов.

первый вход 19 блоков 15 и 16 коррекции выход 20 блока коррекции первого операнда, селектор 21 микрокоманд (и схемных приказов) уровней совмещения, сумматор 22 (кода сдвига), входной коммутатор 23 (для приема результата операционного устройства), входной регистр 25 восстановления операнда, формирователь 26 маркера второго операнда, блок 27 обнаружения конфликтов, первый информационный вход 28 устройства, вход 28i слова состояния инструкции, вход 282 слова состояния программы, вход 28j оперативной памяти, первый информационный выход 29 устройства, выход 29i регистра первого операнда, выход 292 регистра второго операнда, второй информационный выход 30 устройства, выход 30i регистра выходной информации первого блока памяти, выход ЗОг регистра выходной информации второго блока памяти, выходы 31 и 32 блока обнаружения конфликтов, вход 33 микрокоманд п уровней совмещения устройства (соответственно для п 4 33i-334), адресный вход 34 уровней совмещения устройства (соответственно для п 4 ), второй инфор.мационный вход 35 устройства, информационные входы 36 и 37 блока обнаружения, конфликтов, выходы 38-40 селектора микрокоманд.

Блок 27 обнаружения конфликтов (фиг. 2) содержит регистры 41 адресов чтения операндов, схемы 42 сравнения адресов, схемы 43 сравнения младщего рааряда адресов, восемь элементов И 44, четыре элемента ИЛИ 45, выходы 31( -31з - трехразрядный код управления блоком 15 второго операнда, выходы 32i-32з - трехраз ядный код управления блоком 16 первого операнда.

Блок 16 коррекции первого операнда (фиг. 3) содержит три элемента НЕ 46, восемь элементов И 47, четыре элемента ИЛИ 48, входы 19j и 19 - соответственно вход старших и вход младщих 4-х байтов блоков 15 и 16 Коррекции 30j.t и 30i.i - выходы старщих и младщих 4-х байтов информации регистра 8.

Формирователь 26 маркера второго операнда (фиг. 4) содержит память 49 констант маркера и селектор 50 выходной информации.

Для дальнейщего рассмотрения работы устройства примем, что каждый из блоков 1 и 2 памяти разбит на 8 фиксированных зон, по 8 строк длиной в двойное слово в каждой зоне. Зоны блока 1 памяти могут быть следующие;

1 - зона хранения ССИ;занимает 4

строки для случаясовмещения

4-х команд, остальныестроки свободны;

2- зона хранения РОН; в каждой

строке хранятся два РОН; четный и нечетный, каждый длиной по 4 байт;

3- зона хранения РПЛ; заняты 4

строки для хранения РПЛ, остальные 4 строки свободны; 4- зона хранений копий УР; в каждой строке хранятся два УР: четный и нечетный;

5 - рабочая зона 1 для хранения промежуточных результатов, начальных, конечных, текущих адресов операндов в командах SS-формата;

5 6 - рабочая зона 2 для хранения исходных операндов в командах расщиренной точности и десятичной арифметики и копии префикса; 7 и 8 - две зоны для хранения идентификатора процесса и констант, исполь0зуемых в процессе выполнения команди микропрограмм. Зоны блока 2 памяти могут быть следующими:

1- зона хранения исходных ССП теку5щих команд; занимает 4 строки для

хранения ССП 4-х команд, выполняющихся совмещенно;

2- зона РОН; дублирует идентичную

зону в блоке 1 памяти;

3- зона РПЛ; дублирует идентичную 0зону в блоке 1 памяти.

4- зона хранения начальных адресов

таблиц сегментов нескольких задач; в каждой строке хранятся значения 4-х байтных УР для двух задач (управляющий регистр 1 содержит код адреса начала таблицы сегментов и код длины таблицы сегментов). Данная зона заполняется и проверяется при каждом выпо«1нении команды загрузки управления. 5-8 - зоны, дублирующие идентичные зоны

блока 1 памяти.

Рассмотрим работу устройства в процессоре с четырьмя уровнями совмещения команд на примере выполнения команд формата RX.

Предположим, что цикл обращения блоков памяти равен половине мащинного такта (цикла) и, следовательно, в одном такте возможны два обращения к местной памяти.

0 Пусть временная диаграмма совмещенного выполнения команд такова, как показано на фиг. 5. Примем, что такт Т выполняется на первом уровне совмещения, такты Тг, Tj - на 2-м уровне, Т, Тд - на 3-м уровне и Tj , Т.; - на 4-м уровне. Tt - такт выработки команды, в первом полутакте которого ведется запись исходного ССП текущей команды в очередную строку зоны ССП блока 2 памяти под управлением схемного приказа (сигнала, вырабатываемого в каждой команде в начале такта TI); Т -такт модификации адреса второго операнда, в первом полутакте которого ведется считывание из блока 1 и 2 памяти на регистры 7 и 8 значений индекса и базы по адресам индекса и. базы, указанным в соответствующих полях команды первого уровня совмещения, под управлением схемного приказа такта TJ каждрй команды; Тз -такт трансляции адреса, в. первом полутакте которого ведется запись информации ССП в i-ю строку зоны ССП блока 1 памяти под управлением схемного приказа, вырабатываемого в такте Tj каждой команды; Т -такт работы буферной памяти {буфер при обращении к оперативной памяти), во втором полутакте которого ведется чтение первого (или первого и второго операндов для случая команд RR-формата) oneранда из блоков 1 или 2 памяти на выходе регистры 7 и 8 под управлением микрокоманды третьего уровня совмещения по адресам первого (или второго и первого) операндов, указанным в соответствующих полях команды на третьем уровне совмещения; TJ - такт передачи операндов в операционное устройство, в первом полутакте которого ведется .под управлением микрокоманды третьего уровня совмещения прием первого операнда из регистра 8 на регистр 18 первого операнда и прием второго операнда, принятого из.oneративной (буферной) памяти через селектор 13, селектор 14, блок 15 коррекции на регистр 17 второго операнда, в случае выполнения команды RR-формата второй операнд принимается из регистра 7 через селектор 13, селектор 14, блок 14, . блок 15 на регистр 17 второго,oneTJ -такт выполнения операции в операционном устройстве; в случае выполнения команды типа загрузки РОН, РПЛ, УР в этом такте ведется прием содержимого регистра 17 второго операнда через коммутатор 23 на буферный регистр 24 результата, кроме того, ведется прием содержимого изменяемого (первого) операнда с регистра 18 (или 17) на регистр 25 восстановления операнда. Ту-такт записи результата, принятого на буферный регистр 24, в блоки 1 и 2 памяти в соответствующую зону через селекторы 3 и 4 по адресу первого операнда, указанному в соответствующем поле команды 4-го уровня. Как видно из фиг. 5, одновременно в одном машинном цикле могут происходить действия в тактах Tj, Тэ, Tj, Ту для 4-х разных команд, причем действия в тактах Tj, Tj , TS могут происходить в одном и том же полутакте, либо также одновременно могут выполняться действия в тактах Tj , Т4, Tg для 3-хразличных команд, причем действия в тактах Т, Tg также могут производиться в одном и том же полутакте. Это оказывается возможным благодаря управлению различными узлами устройства соответствующими полями микрокоманд и схемными приказами различных уровней совмещения, Управление узлами устройства осуществляется через селектор 21 микрокоманд, на который поступают схемные приказы и микрокоманды всех уровней совмещения. Соответственно этим узлам селектор 21 .микрокоманд содержит три группы выходов, сигналы которых могут выбираться одновременно: группу 40 для управления передачей информации через селекторы 3 и 14 и приема информации на. регистры 17 и 18, группу 38 для обращения к блоку 1 памяти, группу 39 для обращения к блоку 2 памяти. Обращение к местной памяти производится под управлением схемных приказов, вырабатываемых в каждой команде в первом полутакте тактов Tj, Tg,, Т и микрокоманд второго, третьего и четвертого уров ей совмещения в первом или втором полутакте, причем номер полутакта задается самой микрокоманде. Устройство работает следующим образом. В начале выборки каждой команды в первом полутакте такта 1 производится запись текущего 8-байтного ССП по входу 29 через селектор 4 в блок 2 памяти -по адресу, принимаемому . с первого уровня совмещения через селектор 10 на регистр 12 адреса. В начальном состоянии после общего сброса процессора этот адрес на Рв .уровне совмещения устанавливается равным нулю. При передвижении кода команды на следующий уровень совмещения вместе с ней передвигается и код этого адреса, называемого идентификатором хранения- ССП в местной (локальной) памяти. С каждой очередной командой идентификатор ССП на первом уровне увеличивается на «1. Счет организован по модулю количества уровней совмещения, в рассматриваемом случае - по модулю четыре. Таким образом, для четырех команд, выполняющихся одновременно на 4-х уровнях совмещения, обеспечивается сохранность в местной памяти их исходной ССП, причем адрес хранения ССП (идентификатор) в зоне ССП известен и хранится на соответствующем уровне для каждой команды. В следующем такте Т, такте модификации адреса, производится в первом полутакте под управлением схемного приказа модификации адреса считывание из местной памяти значений индекса и базы. Адрес индекса и зоны РОН, указанный в поле команды второго уровня совмещения, поступает на регистр 11 адреса блока 1 памяти через селектор 9, а адрес базы (из зоны РОН), также указанный в поле команды 2-го уровня совмещения, поступает на регистр 12 адреса блока 2 памяти. При этом устанавливается адрес зоны РОН. Считанные значения индекса и базы поступают на выходные регистры 7 и 8 через селекторы 5 и 6. Если младший разряд адреса индекса или базы равен «1, что указы-, вает на нечетный РОН, то на селекторах 7 или 8 производится соответствующий сдвиг влево на четыре байта, так что индекс и база всегда располагаются в выходных регистрах 7 и 8, выравненные по их левому разряду. Значения индекса и базы затем поступают на выходные линии 30, на входы адресного сумматора процессора. В последующем такте Тз трансляция адреса производится также в первом полутакте -(запоминание слова состояния инструкции ССИ по входу 28i через селектор 3 в блоке 1 памяти). Адрес запоминания текущего ССИ в зоне ССИ равен адресу хранения ССП в зоне ССП данной команды и берется из поля индентификатора ССП на 2-м уровне совмещения. Он поступает на регистр 11 адреса блока 1 памяти через селектор 9. Сохранность текущего ССИ в местной памяти позволяет микропрограмме в любом такте обратиться к его содержимому по адресу идентификатора на соответствующем уровне. Это необходимо, например, при выполнении ко.манд передачи управления, когда для возврата к старой ветви необходимо значение продвинутого счетчика команд, при прерываниях, когда необходимо запомнить старое ССП, в командах, где используется .модифицированный адрес не как адрес операнда, а в качестве операнда (код сдвига, номер канала и абонента и т. д.), в процедурах восстановления по контролю, где используется значение адреса испорченного в оперативной памяти операнда и т. п. Все указанные действия в тактах TI, Тг, Тэ выполняются в первом полутакте под управлением схемных приказов, вырабатываемых в каждойкоманде, независимо от кода команды. Б следующем такте работы процессора, такте Тч во втором его полутакте ведется считывание исходного первого операнда в командах RX-формата, или первого н второго операндов в командах RR-формата под управлением микрокоманды 3-го уровня совмещения. В зависимости от кода команды считывание из зоны РОН, РПЛ или УР ведется по адресам операндов, указанных в соответствующем поле команды третьего уровня совмещения. Соответственно адрес первого операнда поступает на регистр 12 адреса блока 2 памяти через селектор 10, адрес 2-го- операнда (в командах RR-формата) поступает на регистр 11 адреса блока 1 памяти через селектор 9. Значения операндов считываются на выходные регистры 7 и 8 через селекторы 5 и 6. Если указаны нечетные номера РОИ или УР, то производится, при этом соответствующий сдвиг влево на 4 байта. В случае, если операнды длинные (8 байт) или если указан номер четного РОН или УР, считывание производится без сдвига, т. е. могут быть сосчитаны сразу два РОН (УР) четный и нечетный, находящиеся в одной строке локальной памяти. В следующем- такте Т производится передача в операционное устройство через регистры 17 и 18 второго и первого операндов. Загрузка регистров 17 и .18 ведется под управлением микрокоманды третьего уровня совмещения, причем в случае выполнения команды RR-формата первый операнд поступает с выхода регистра 8 через блок 16 коррекции на вход регистра 18, а второй операнд поступает с выхода регистра 7 через селектор 13, селектор 14 (без сдвига), блок 15 коррекции на вход регистра 17. При загрузке регистров17 и 18 производится анализ конфликта по чтению операнда, модификация которого в предыдущей команде еще не заверщена. Такой анализ производится блоком 27 обнаружения конфликтов (фиг. 3), путем сравнения адресов чтения операндов, запомненных на буферных регистрах 41, с адресом записи результата в предыдущей команде. При этом учитывается длина записываемого результата и четность РОН результата и считанные операнды. Обнаружение конфликта производится независимо для каждого операнда на двух отдельных схемах. В результате обнаружения конфликта вырабатывается соответствующий трехразрядный код управления блоками 15 и 16 коррекции операндов, через которые на неизменяемые части регистров 17 и 18 поступает содержимое соответствующих частей регистров 7 и 8, а на изменяемые части регистров 17 и 18 поступают соответствующие части результата, выработанного в предыдущей команде. В случае выполнения команды RX-формата второй операнд поступает из оперативной памяти по входу 28 через селектор 13, селектор 14, блок 15 на вход регистра 17. При этом на селекторе 14 производится сдвиг влево по номеру байта (три младщих разряда адреса операнда) так, что операнд выравнивается по своему левому разряду. Код сдвига вырабатывается сумматором 22, на один вход которого поступает номер байта, на второй вход - константа сдвига. Константа сдвига указывается в микрокоманде и используется при выполнении команд загрузки полуслов, символов при каждом случае необходимого формирования операнда путем сдвига. Сдвиг кольцевой и может быть задан от О до 7 байт. Этот же сдвигатель используется и при чтении операнда из блоков локальной памяти или приеме через селектор 13 любой другой информации в командах записи в оперативную (буферную) память. В этом случае код сдвига также вырабатывается на сумматоре 22, но номер байта при этом вычитается, т. е. сдвиг осуществляется по номеру байта влево. Прием на регистр 17 информации осуществляется по маркеру, формируемому формирователем 26. Маркер восьмиразрядный и единица в разряде маркера разрещает изменение соответствующего байта регистра 17, а нуль сохраняет прежним значение данного байта. Формирователь 26 может быть построен так, как показано на фиг. 4. Маркер приема на регистр 17 либо явно указывается в микрокоманде (1-й вход селектора), либо считывается из памяти констант маркера, обращение к которой ведется по адресу, старшие разряды которого составлены из трехразрядного кода номера байта, а младшие разряды - из трехразрядного кода длины операнда, указанного в микрокоманде. Сочетание работы селектора 14 и формирователя 26 дает возможность формировать операнды из частей различных источников, а также формировать операнд в случае нецелочисленной его границы, т. е. когда он расположен в двух смежных ячейках оперативной (буферной) памяти. На четвертом уровне совмещения в такте Tg ведется прием содержимого регистра 17 второго операнда через коммутатор 23 на буферный регистр 24 результата в командах загрузки РОН, РПЛ и УР. Кроме того, в этом такте ведется прием содержимого изменяемого операнда (первого или второго) на регистр 25 восстановления операнда. Выход регистра 25 поступает на вход селектора. 13, и в процедурах восстановления операнда по контролю его содержимое может восстановить испорченный операнд РОН или РПЛ в местной памяти. В последнем такте выполнения команды, такте 7 .записи результата, результат операционного устройства, принятый через коммутатор 23 на буферный регистр 24, поступает через селекторы 3 и 4 на информационные входы блоков 1 и 2 памяти, и записывается в соответствующую зону (РОН или РПЛ) по адресу первого операнда, указанному в поле команды четвертого уровня. Запись производится под управлением микрокоманды четвертого уровня во втором полутакте. Запись в оба блока памяти ведется по маркеру записи, явно заданному в микрокоманде четвертого уровня, причем информация сдвигается на селекторах 3 и 4 вправо на 4 байта, если результат пишется в нечетный РОН. При выполнении команд SS-формата необходимо некоторые промежуточные результаты сдвигать на 1 или несколько байт. Для ускорения этого процесса предусмотрены микрокоманды, в которых задается чтение промежуточного результата из рабочей зоны, по адресу, явно указанному в микрокоманде, на регистре 7 в первом полутакте, сдвигу его на селекторе 14 на необходимое число байт и запись снова в рабочую зону по тому же или другому адресу в блоки 1 и 2 памяти во втором полутакте одного и того же машинного цикла. Таким образом, повышение быстродействия устройства сопряжения с местной па мятью в процессоре большой производительности с п уровнями совмещения достигнуто путем построения управления и селекции адресов от п различных уровней совмещения с разделением времени обращения к локальной памяти в разных полутактах для микрокоманд, выполняющихся одновременно. Повышение быстродействия достигнуто также благодаря введению в устройство схемы коррекции операндов в случае определения конфликта по операнду из-за совмещения операций. Сохранение в местной памяти копий исходных операндов, ССП, префикса и УР позволяет выполнять повторение команд, в которых произошла ошибка. Кроме того, путем введения банка внутренних данных упорядочивается структура процессора, увеличиваются его функциональные возможности по выполнению различных тестовых и диагностических процедур, сокра-щается регистровое оборудование на построение ряда.управляющих и рабочих регистров. Введение недублированных зон и раздельных селекторов 3 и 4 для блоков 1 и 2 памяти повышает оптимальность использования местной памяти, что также уменьшает оборудование на построение соответствующих буферных регистров (таблица начал адресов сегментов, значения модифицированных адресов оТ1ерандов и счетчика команд).

ад

29,

/Kl7 ФиъЛ П л и П I Г/ Л 1- I11 11

7/

ь

Фиг.5 75 Т6 77 1-н1ТЗ ТЧ 75 11Н 7/и7J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ И ДЛЯ НАХОЖДЕНИЯ КОРНЕЙ ЧИСЛЕННЫХ УРАВНЕНИЙ | 1924 |

|

SU1045A1 |

| М., «Финансы и статистика 1981, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1985-01-23—Публикация

1982-11-10—Подача