версный выход седьмого разряда регистра соединен с вторыми входами третьего и пятого элементов И, прямой выход восьмого разряда регистра соединен с первыми входами второго и DiecToro элементов И, инверсный выход восьмого разряда регистра соединен с первым входом седьмого элемета И, второй вход которого соединен с вторым входом второго элемента И прямым выходом девятого разряда регистра, инверсный выход которого соединен с вторым входом шестого элемента Н, выход десятого разряда .регистра соединен с вторым входом второго элемента ИЛИ, выходы шифратора промежуточньрс сумм соединены соответственно с вторым входом переноса, с первым и вторым входами промежуточных сумм и с первьш входом суммы следующего разряда конвейерного сумматора, выходы шестого и седьмого элементов И соединены соответственно с вторьпч и третьим входами сумм следующего разряда конвейерного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

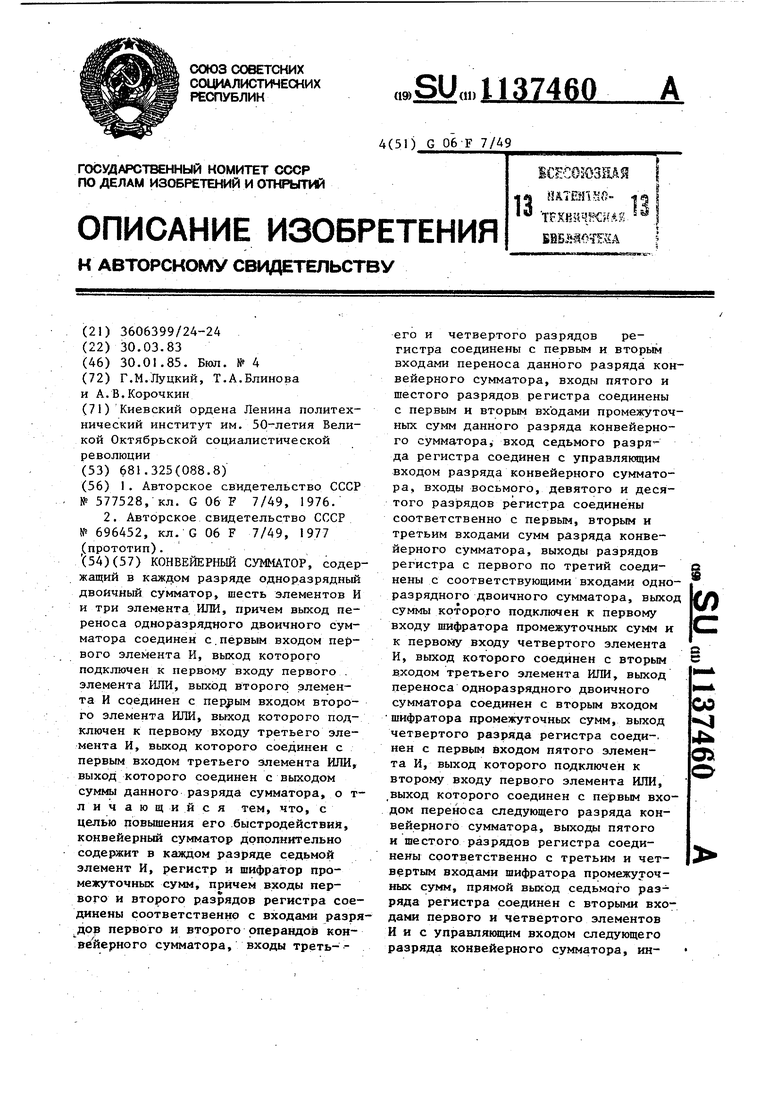

КОНВЕЙЕРНЫЙ СУММАТОР, содержащий в каждом разряде одноразрядный двоичный сумматор, шесть элементов И и три элемента ИЛИ, причем выход переноса одноразрядного двоичного сумматора соединен с.первым входом первого элемента И, выход которого подключен к первому входу первого . элемента ИЛИ, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с выходом суммы данного разряда сумматора, о тлнчающийся тем, что, с целью повышения его быстродействий, конвейерный сумматор дополнительно содержит в каждом разряде седьмой элемент И, регистр и шифратор промежуточных сумм, причем входы первого и второго разрядов регистра соединены соответственно с входами разрядов первого и второго операндов конвейерного сумматора, входы треть-его и четвертого разрядов регистра соединены с первым и вторым входами переноса данного разряда конвейерного сумматора, входы пятого и шестого разрядов регистра соединены с первым и вторым входами промежуточных сумм данного разряда конвейерного сумматора, вход седьмого разряда регистра соединен с управлякяцим входом разряда конвейерного сумматора, входы восьмого, девятого и десятого разрядов регистра соединены соответственно с первым, вторым и третьим входами сумм разряда конвейерного сумматора, выходы разрядов регистра с первого по третий соедиi нены с соответствующими входами одноразрядного двоичного сумматора, выход суммы которого подключен к первому входу шифратора промежуточных сумм и к первому входу четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход переноса одноразрядного двоичного со сумматора соединен с вторым входом шифратора промежуточных сумм, выход 4 четвертого разряда регистра соеди-. нен с nepBtiM входом пятого элемено: та И, выход которого подключен к второму входу первого элемента ИЛИ, ,выход которого соединен с первым входом переноса следующего разряда конвейерного сумматора, выходы пятого и шестого разрядов регистра соединены соответственно с третьим и четвертым входами шифратора промежуточных сумм, прямой выход седьмого разряда регистра соединен с вторыми входами первого и четвертого элементов И и с управляющим входом следующего разряда конвейерного сумматора, ин

Изобретение относится к вычислительной технике и может быть использовано в вьгаислительньк устройствах высокой производительности.

Известно накапливающее устройст- во для суммирования чисел, представленных как в классической двоичной системе счисления., так и в 1-коде Фибоначчи или золотом 1-коде, каждый разряд которого содержит триггер со счетным входом, элементы И, ИЛИ,, элемент сложения по модулю 2 и элемент задержки tl3.

Недостатком известного устройства является невысокое быстродействие.

Наиболее близким к данного техническому решению является сумматор, содержащий в каждом разряде одноразрядный двоичный сумматор, шесть элементов И и три элемента ИЛИ, причем выход переноса одноразрядного двоичнго сумматора соединен с первым входо первого элемента И, выход которого подключен к первому входу первого i элемента ИЛИ, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого,подключен к первому входу третьего элемента И, выход -которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с выходом суммы данного разряда сумматора, сумматор содержит также блок инвертирования, блок формирования дополнительны .сигналов суммы переноса и элемент .эадержки С21.

Недостатком известного сумматора является невысокое быстродействие, обусловленное тем, что он осуществлет суммирование h-разрядных чисел за п-тактов.

Целью изобретения является повышение быстродействия сумматора

1 - . .

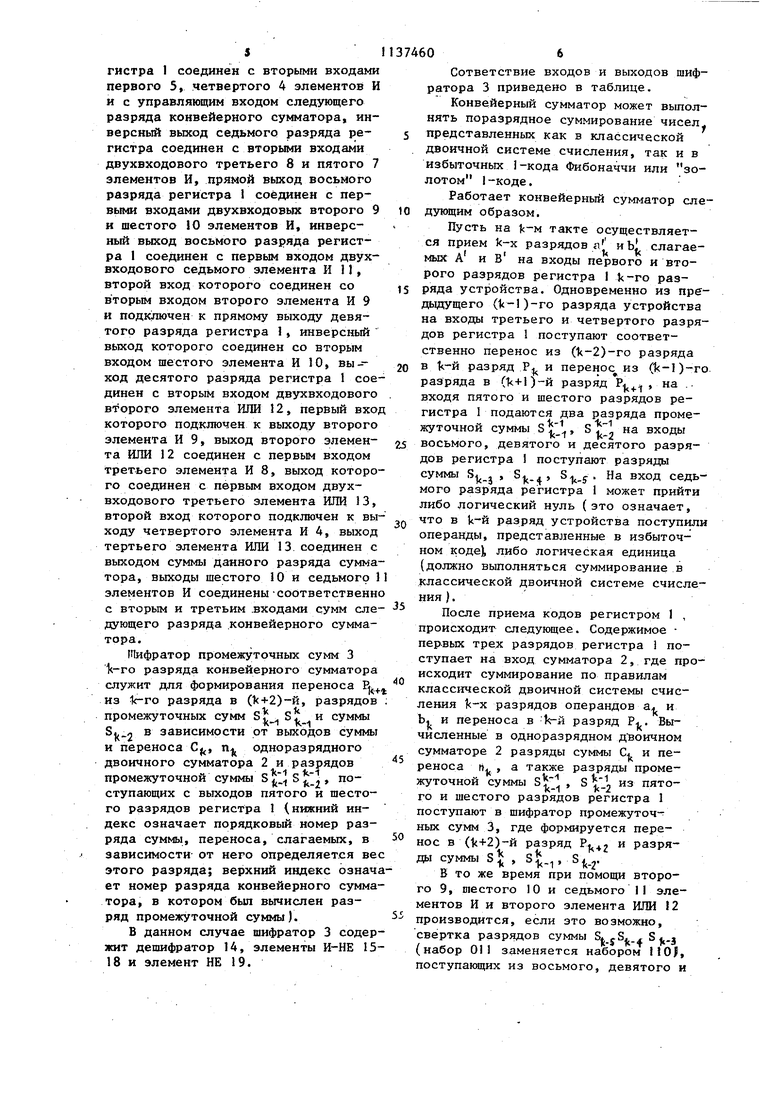

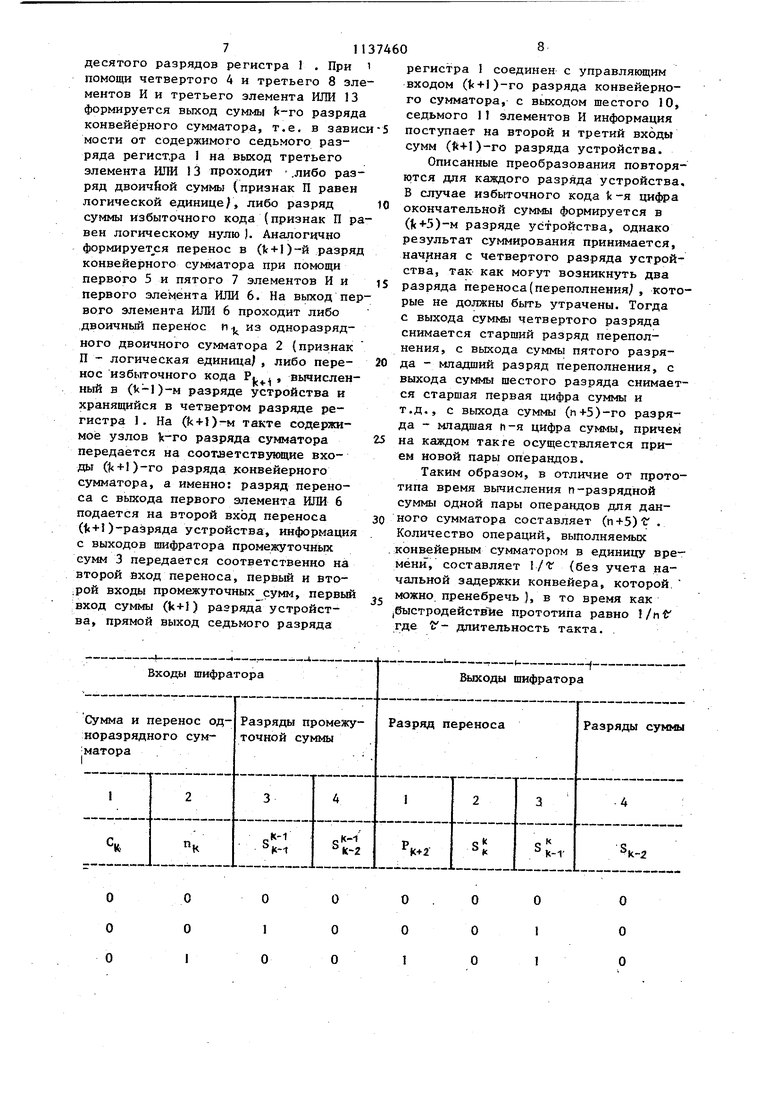

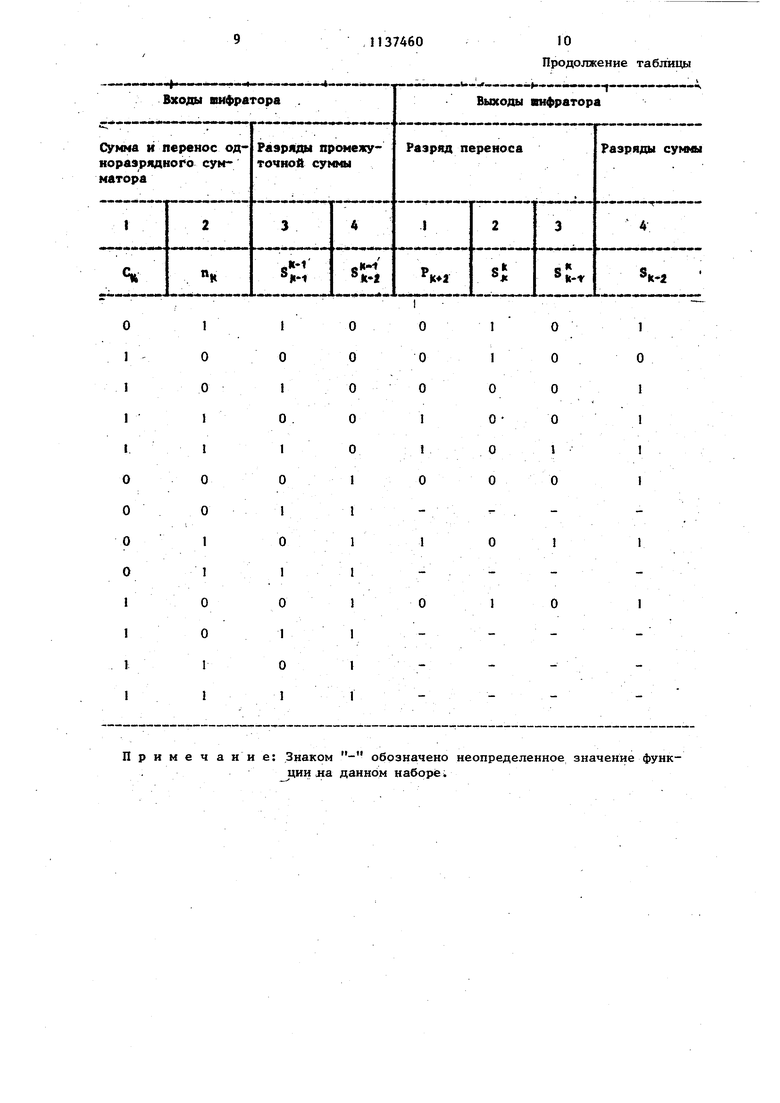

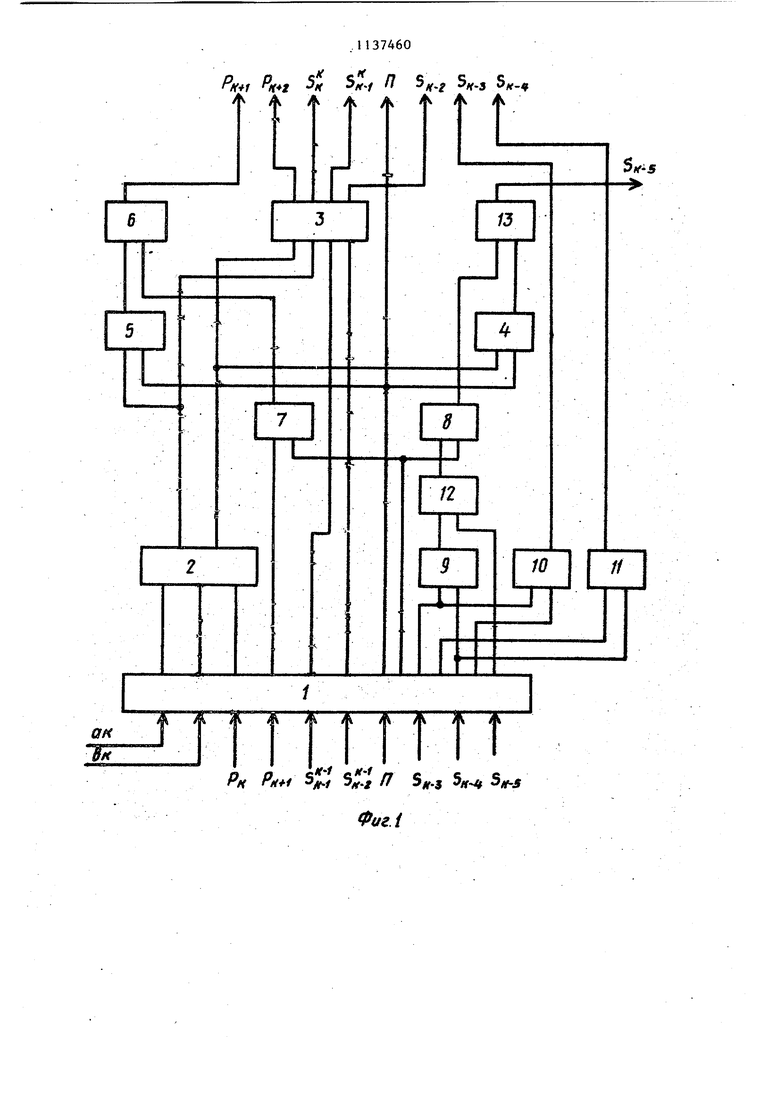

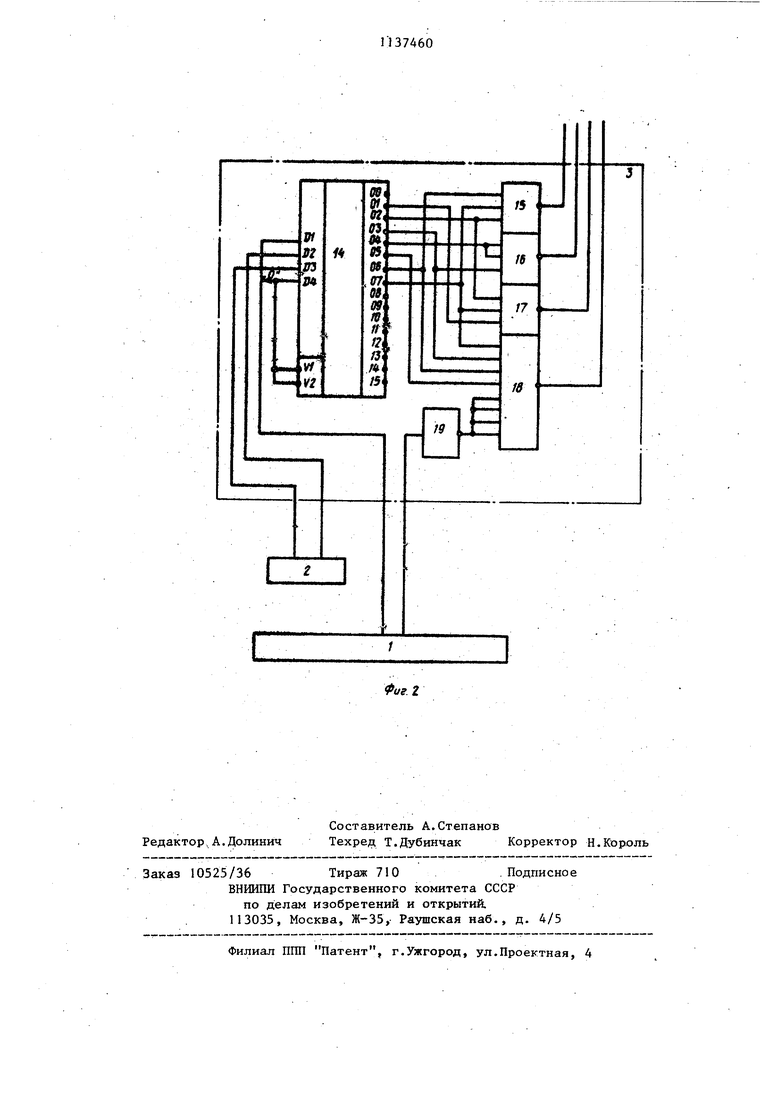

Поставленная цель достигается тем, что в конвейерный сумматор, содержащий в каждом разряде одноразрядный двоичный сумматор, шесть элементов И и три элемента ИЛИ, причем выход переноса одноразрядного двоичного сумматора соединен с первым входом первого элемента И, выход которого подключен к первому вхо-ду первого элемента ИЛИ, выход второго элемента И соединен с первым входом второго элемента ИШ, выход которого подключен к первому входу третьго элемента И, выход которого соединен С первым входом третьего элемента ИЛИ, выход которого соединен с выходом суммы данного разряда сумматора, в каждый разряд введены дополнительно седьмой элемент И, регистр и шифратор промежуточных сумм, причем входы первого и второго разрядов регистра соединены соответственно со входами разрядов первого и второго операндов конвейерного сумматора, входы третьего и четвертого разрядов регистра соединены с первым и вторым входами переноса данного разряда конвейерного сумматора, входы пятого и шестого разрядов регистра соединены с первым и BTOpbiM входами промежуточных сумм данного разряда конвейерного сумматора, вход седьмого разряда регистра соединен с управляющим входом раз ряда конвейерного сумматора, входы восьмого,девятого н десятого разрядов регистра соединены соответственно с первым, вторым и третьим вхо дами сумм разряда конвейерного сумматора, выходы разрядов регистра с первого по третий соединены с соответствующими входами одноразрядного двоичного сумматора, выход суммы которого подключен к первому входу шифратора промежуточных сумм и к первому входу четвертого элемента И, выход которого соединен со вторым вх дом третьего элемента ИЛИ, выход переноса одноразрядного двоичного сумматора Соединен с вторым входом шифратора промежуточных сумм, выход чет вертого разряда регистра соединен с первым входом пятого элемента И, выход которого подключен к второму вхо первого элемента ИЛИ, выход которого соединен с первым входом переноса следукяцего разряда конвейерного сумматора, выходы пятого и шестого разрядов регистра соединены соответственно с третьим и четвертым входами шифратора промежуточных сумм, прямой выход седьмого разряда регистра соединен с вторыми входами первого и четвертого элементов И и с управлякяцим входом следующего разряда, конвейерного, сумматора, инверсньй выход седьмого разряда регистра соединен с вторыми входами третьего и пятого элементов И, прямой выход восьмого разряда регистра соединен с первыми входами второго и шестого элементов И, инверсный выход восьмого разряда регистра соединен с первым входом седьмого элемента И, второй вход которого соединен с вторым входом второго элемента И и с прямым выходом девятого разряда регистра, инверсный выход которого соедииен с вторым входом шестого элемента И, выход десятого разряда регистра соединен со вторым входом второго элемента ИЛИ, вьисоды шифратора промежуточных сумм соединены соответ ственно с вторым .входом переноса, с первым и вторым входами промежуточных сумм и с первы} входом суммы следующего разряда конвейерного сумма тора, выходы шестого и седьмого, элементов И соединены соответственно со вторым и третьим входами сумм следую щего разряда конвейерного сумматора. На фиг.1 представлена структурная схема разряда конвейерного сумматора; на фиг.2 - принципиальная схема шифратора пройежуточных сумм. Конвейерный сумматор содержит (п+5) разрядов. Каждый разряд конвейерного сумматора состоит из 10-разрядного регистра 1, входы первого и второго разрядов которого соединены соответственно с входами разрядов первого и второго операндов конвейерного сумматора, входы третьего и четвертого разрядов регистра 1 соединены с первым и вторым, входами переноса данного разряда конвейер.ного сумматора, входы пятого и шестого разрядов регистра 1 соединены с первым и вторым входами промежуточных сумм данного разряда . конвейерного сумматора, вход седьмого разряда регистра 1 соединен с управляющим входом разряда конвейерного сумматора, входы восьмого, девятого и десятого разрядов регистра 1 соединены соответственно с первым, вторым и третьим входами сумм разряда конвейерного сумматора, выходы разрядов регистра 1 с первого по третий соединены с соответствующими входами одноразрядного двоичного сумматора 2, выход суммы которого подключен к первому входу шифратора промежуточной сумм 3 и к первому входу двухвходового четвертого элемента НА, вы1ХОД переноса одноразрядного двоичного сумматора 2 соединен с вторым входом шифратора промежуточных сумм 3 и с первым входом двухвходового первого элемента И 5, выход которого подключен к первому входу двухвходового первого элемента ИЛИ 6, выход которого соединен, с первым входом переноса следующего разряда конвейерного сумматора, второй вход первого элемента ИЛИ 6 подключен к выходу пятого двухвходового элемента И 7, первый вход которого соединен с выходом четвертого разряда регистра 1, пятый и шестой разряды которого соединены соответственно с третьим и четвертым входами шифратора промежуточных сумм 3, выходы которого соединены соответственно с вторым входом переноса, с первым и вторым входами промежуточных сумм и с первым входом суммы следующего разряда конвейерного сумматора, прямой выход седьмого разряда регнстра 1 соединен с вторыми входами первого 5, четвертого 4 элементов И и с управляющим входом следующего разряда конвейерного сумматора, инверсный выход седьмого разряда регистра соединен с вторыми входами двухвходового третьего 8 и пятого 7 элементов И, прямой выход восьмого разряда регистра I соединен с первыми входами двухвходовых второго 9 и шестого 10 элементов И, инверсный выход восьмого разряда регистра 1 соединен с первым входом двухвходового седьмого элемента И J, второй вход которого соединен со вторым входом второго элемента И 9 и подкгаочен к прямому выходу девятого разряда регистра 1, инверсный вькод которого соединен со вторым входом шестого элемента И 10, вы-ход десятого разряда регистра 1 соединен с вторым входом двухвходового второго элемента ИЛИ 12, первый вход которого подключен к выходу второго элемента И 9, выход второго элемента ИЛИ 12 соединен с первым входом третьего элемента И 8, выход которого соединен с первым входом двухвходового третьего элемента ИЛИ 13, второй вход которого подключен к выходу четвертого элемента И 4, выход тертьего элемента ИЛИ 13. соединен с выходом суммы данного разряда сумматора, выходы шестого 10 и седьмого П элементов И соединены-соответственно с вторым и третьим .входами сумм еледующего разряда конвейерного сумматора. Шифратор промежуточных сумм 3 разряда конвейерного сумматора служит для формирования переноса Р| из 1с-го разряда в (+2)-й, разрядов промежуточных сумм sl S и суммы S..2 в зависимости от выходов суммы и переноса Cjj, п одноразрядного двоичного сумматора 2 и разрядов промежуточной суммы , поступающих с выходов пятого и шестого разрядов регистра 1 (нижний индекс означает порядковый номер разряда суммы, переноса, слагаемых, в зависимости от него определяется вес этого разряда; верхний индекс означа ет номер разряда конвейерного сумматора, в котором был вычислен разряд промежуточной суммы). В данном случае шифратор 3 содержит дешифратор 14, элементы И-НЕ 1518 и элемент НЕ 19. Сответствие входов и выходов шифратора 3 приведено в таблице. Конвейерный сумматор может выполнять поразрядное суммирование чисел представленных как в классической двоичной системе счисления, так и в избыточных 1-кода Фибоначчи или золотом 1-коде. Работает конвейерный сумматор следующим образом. Пусть на такте осуществляется прием k-x разрядов а и bj слагаемых А и в на входы первого и второго разрядов регистра I разряда устройства. Одновременно из предыдущего ()-го разряда устройства на входы третьего и четвертого разрядов регистра I поступают соответственно перенос из (1(-2)-го разряда в 1f.fi разряд Р и перенос из ()-го. разряда в ()-й разрядp j , на .. входя пятого и шестого разрядов регистра I подаются два разряда промежуточной суммы S .Д , S 3 входы восьмого, девятого и десятого разрядов регистра I поступают разряды суммы , S,, . На вход седьмого разряда регистра 1 может прийти либо логический нуль (это означает, что в k-й разряд устройства поступили операнды, представленные в избыточном коде), либо логическая единица (должно выполняться суммирование в классической двоичной системе счисления ). Лосле приема кодов регистром 1 , происходит следующее. Содержимое пер.вых трех разрядов регистра 1 поступает на вход сумматора 2, где происходит суммирование по правилам классической двоичной системы счисления разрядов операндов a.j и Ь, и переноса в k-й разряд Р|. Вычисленные в одноразрядном двоичном сумматоре 2 разряды суммы C.i и переноса П , а также разряды промежуточной суммы , S 2 пятого и шестого разрядов регистра 1 поступают в шифратор промежуточных сумм 3, где формируется перенос в()-й разряд Pf + 2 разряды суммы s , s..,, S. Б то же время при помощи второго 9, DiecToro 10 и седьмого 1 I элементов И и второго элемента ИЛИ 12 производится, если это возможно, свертка разрядов суммы .., Sj.j (набор Oil заменяется набором И0|, поступакмцих из восьмого, девятого и

десятого разрядов регистра 1 . При помощи четвертого 4 и третьего 8 элементов И и третьего элемента ИЛИ 13 формируется выход суммы разряда конвейерного сумматора, т.е. в зависи мости от содержимого седьмого разряда регистра 1 на выход третьего элемента ШШ 13 проходит .либо разряд двоич&ой суммы {признак П равен логической единице, либо разряд суммы избыточного кода (признак П равен логическому нулю ). Аналогично фopмиpyeтJCЯ перенос в (1( + ))-й разряд конвейерного сумматора при помощи

первого 5 и пятого 7 элементов И и первого элемента ШШ 6. На выход первого элемента ИЛИ 6 проходит либо .двоичный перенос и из одноразрядного двоичного сумматора 2 (признак П - логическая единица) , либо перенос избыточного кода вьяисленный в ()-м разряде устройства и хранящийся в четвертом разряде регистра 1. На ()M такте содержимое узлов разряда сумматора передается на соотлетствзяощие входы (1 + 1)-го разряда конвейерного сумматора, а именно: разряд переноса с выхода первого элемента ИЛИ 6 подается на второй вход переноса (|« + 1)-рааряда устройства, информация с выходов шифратора промежуточных сукш 3 передается соответственно на второй вход переноса, первый и вто,рой входы промежуточных сумм, первый вход суммы (k+) разряда устройства, прямой выход седьмого разряда

о о о

о 1 о

о о I

регистра 1 соединен с управляющим входом (f + l)-ro разряда конвейерного сумматора, с выходом шестого 10, седьмого 11 элементов И информация поступает на второй и третий входы сумм (+1)-го разряда устройства.

Описанные преобразования повторяются для каждого разряда устройства. В случае избыточного кода t-я цифра окончательной суммы формируется в (jt+5)-M разряде устройства, однако результат суммирования принимается, начиная с четвертого разряда устройства, так как могут возникнуть два

разряда переноса(переполнения , которые не должны быть утрачены. Тогда с выхода сумма четвертого разряда снимается старший разряд переполнения, с выхода суммы пятого разряда - младший разряд переполнения, с выхода суммы шестого разряда снимается старшая первая цифра суммы и т.д., с выхода суммы (п+5)-го разряда - младшая п-я цифра суммы, причем

на каждом такте осуществляется прием новой пары операндов.

Таким образом, в отличие от прототипа время вычисления п-разрядной суммы одной пары операгщов для данного сумматора составляет (n+5)V .

Количество операций, выполняемых .конвейерным сумматором в единицу времени, составляет 1/f (без учета начальной задержки конвейера, которой можно пренебречь ), в то время как

|6ыстродейств ие прототипа равно l/nf

1 длительность такта.

где

о о о

о

о о о

1 1 Примечание: Знаком - обозначено ции ла данном наборе. неопределенное значение функРН Рт-1 V/ V/ S..j Ък S/f-s Фиг I

т tz

f4

P ЛФ

VI 42

Г

g S

/5

«

/7

ffi /

/tf

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-30—Публикация

1983-03-30—Подача