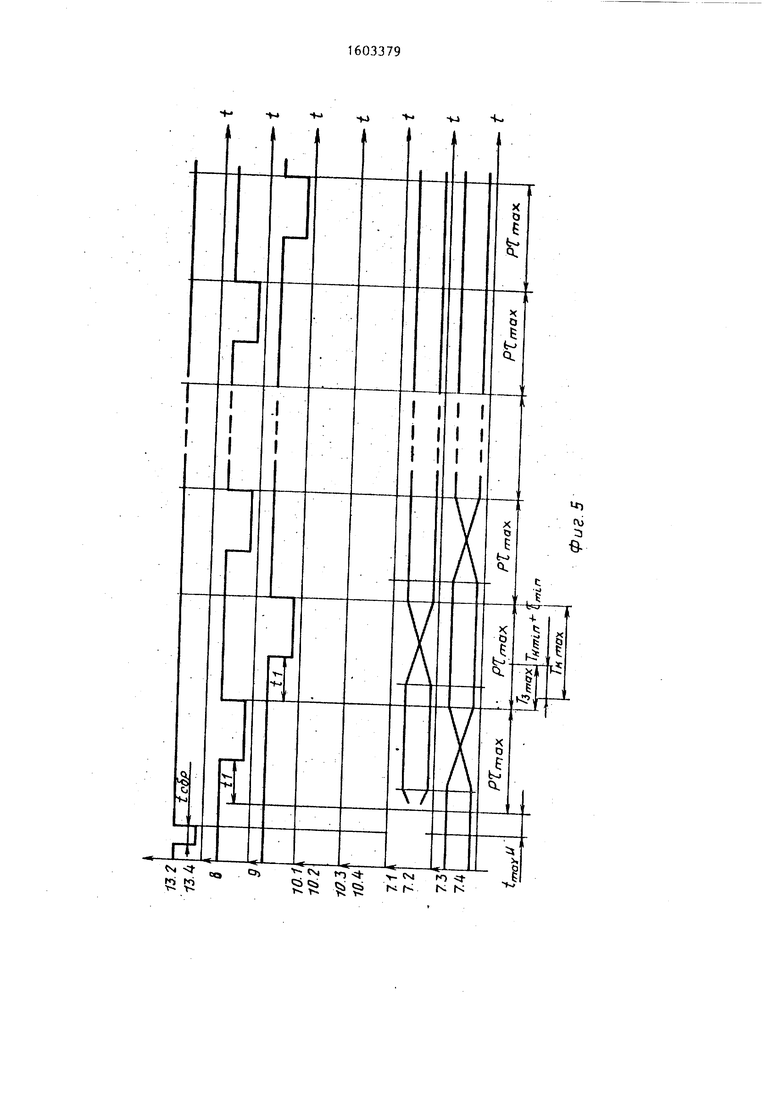

TjMdKf « меньше, чем (Т.мм f м.м ) ;

MSKC {Т,и,„{ (Т,„„„- Т,,,,), при Т,.„,5.ЛЧРО

T|«eio « « ™ (т, );

л tio.tHt - t, (Р- )МС1,С- (Л tt.,,,ME),

где t„,ц ,д - минимальное время пере ходного процесса в ло- гическом элементе И;

максимальное время, необходимое для считывания результата с выходов 10.1-10.4 устройства для умножения;

Т к макс

К мик максимальное и минималь ное время коммутации разрядов множителя В на входах 7.1-7.4 с уче том времени прохождения сигналов через логические элементы И;

макс . 3 величина равная боль- .тему из элементов,записанных в квадратных скобках.

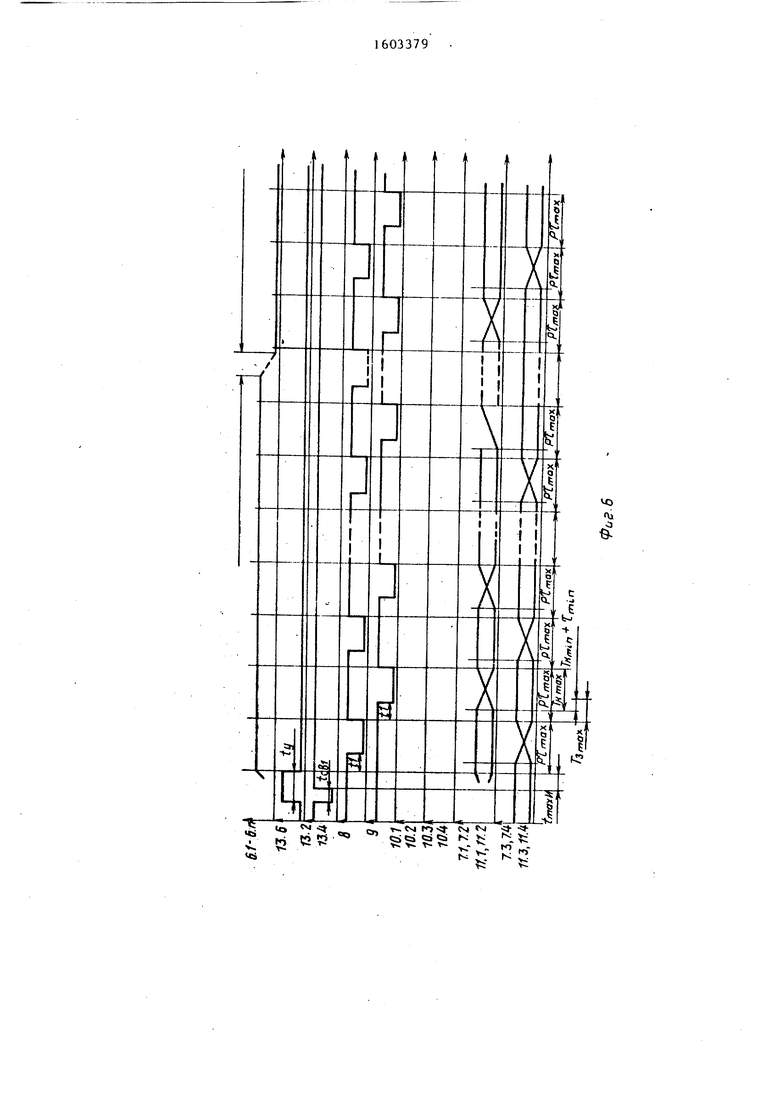

Работа устройства для умножения в режиме тестирования (фиг о6) отличается от работы в режиме вычисления ем, что в исходном состоянии на уста овочный вход 13.6 одновременно с им- ульсом сброса подается положительный мпульс длительностью t .

Этот импульс устанавливает на всех выходах переноса одноразрядных сумматоров 4.г (г 1, 3, 5,...) сигнал 1. Затем осуществляется подача тестовых значений первого операнда А (множимого) и второго операнда в (множителя) аналогично тому,как это осуществлялось в режиме вычислений Кроме того, синхронно с разряда- мц первого операнда В° осуществляется подача разрядов тестового операнда С ° на дополнительные входы 11.1- 11.4 матрицы однораз рядных сумматоров.

Так как устройство для умножения выполнено в виде замкнутого конвейера, его тестирование осуществляется за счет начальной установки и подачи таких значений входных операндов А , В и С°, что на каждый одноразрядный су 1матор и элемент И в процессе вы- числения поступают все тестовые на- боры. При этом результат вычисления представляет собой не только А х X В С, но и сигнатуру всех тестовых откликов. Если сигнатура не совпадает с эталонньм значением, значит устройство для умножения содержит неисправность. Тестирование осуществляется за N тактов работы конвейера, где

N 23р + 4р + 3(р-1) ЗОр - 3.

При этом одному такту работы кон- JO вейера соответствует время переход- ного процесса в одном ряду ячеек матрицы умножения.

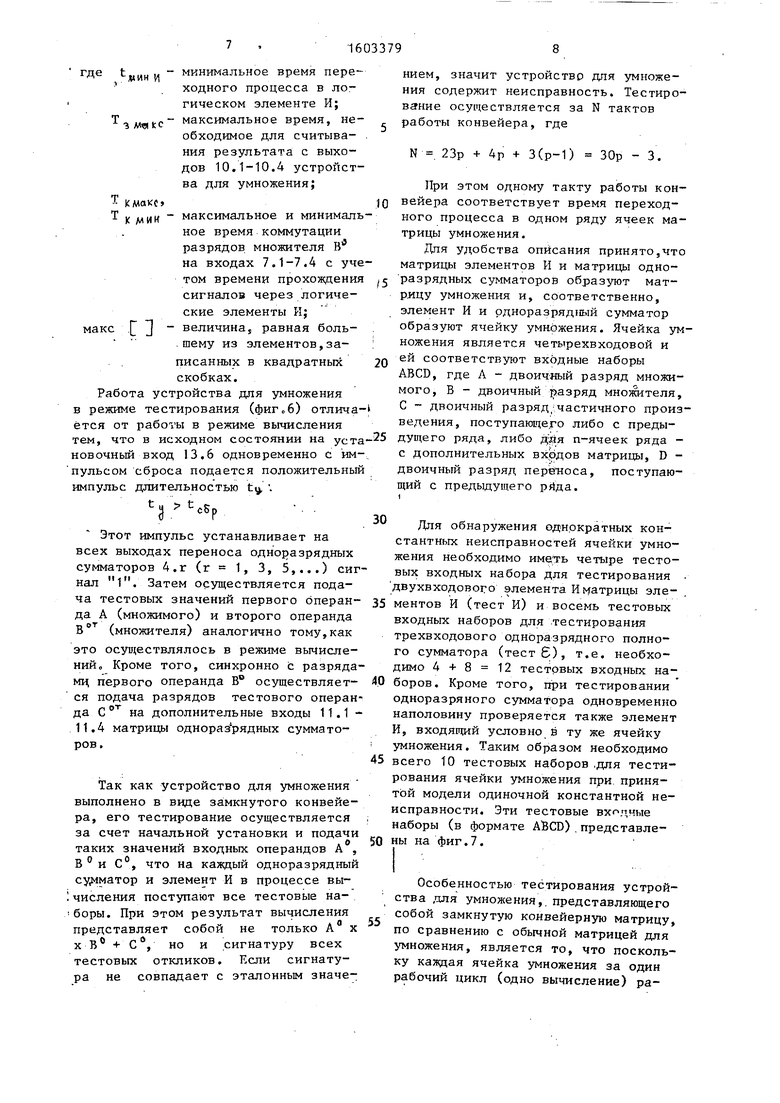

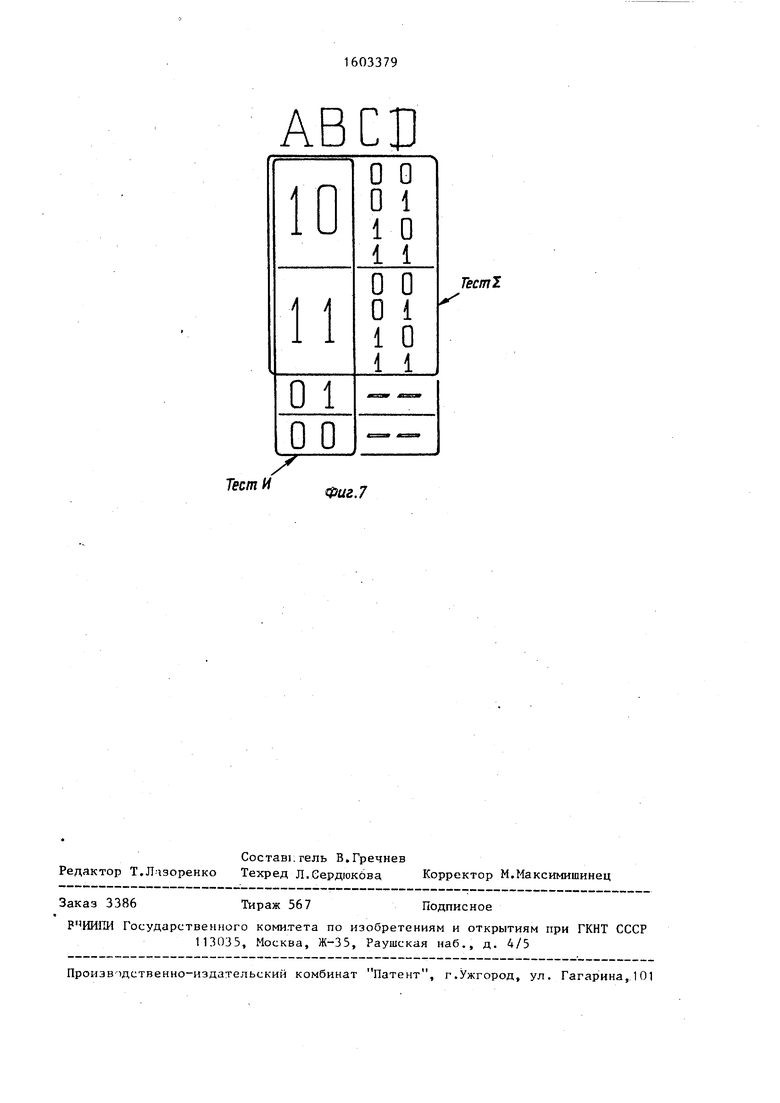

Для удобства описания принято,что матрицы элементов И и матрицы одно- /5 разрядных сумматоров образуют матрицу умножения и, соответственно, элемент И и одноразрядный сумматор образуют ячейку умножения. Ячейка ум- ножения является четырехвходовой и 2Q ей соответствуют входные наборы

ABCD, где А - двоичный разряд множимого, В - двоичный разряд множителя, С - двоичный разряд,-:частичного произведения, поступающего либо с преды- 25 дущего ряда, либо дйя п-ячеек ряда - с дополнительных входов матрицы, D - двоичный разряд переноса, поступающий с предьщущего рйда.

30

Для обнаружения однократных константных неисправностей ячейки умножения необходимо иметь четыре тестовых входных набора для тестирования двухвходового элемента И матрицы эле35 ментов И (тест И) и восемь тестовых входных наборов для тестирования трехвходового одноразрядного полного сумматора (тест 6), т.е. необходимо 4 + 8 12 тестовых входных наЛ.О боров. Кроме того, при тестировании одноразряного сумматора одновременно наполовину проверяется также элемент И, входящий условно в ту же ячейку

умножения. Таким образом необходимо

45 всего 10 тестовых наборов ,для тестирования ячейки умножения при принятой модели одиночной константной неисправности. Эти тестовые входные наборы (в формате ABCD),представле50 ны на фиг.7.

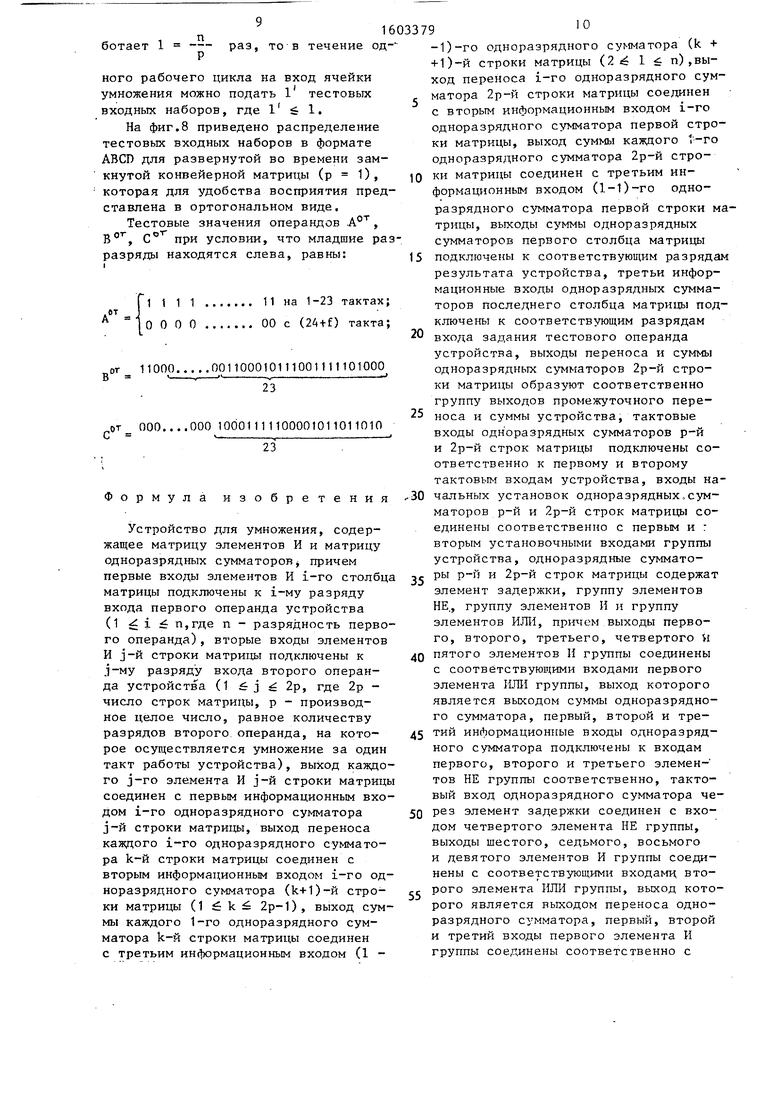

Особенностью тестирования устрой- ства ,аля умножения,, представляющего собой замкнутую конвейерную матрицу, по сравнению с обычной матрицей для умножения, является то, что поскольку каядая ячейка умножения за один рабочий цикл (одно вычисление) работает 1

Р

раз, то в течение од-

ного рабочего цикла на вход ячейки умножения можно подать 1 тестовых входных наборов, где 1 1.

На фиг.8 приведено распределение тестовых входных наборов в формате ABCD для развернутой во времени замкнутой конвейерной матрицы (р 1), которая для удобства восприятия представлена в ортогональном виде.

Тестовые значения операндов А° ,

В

ОТ

, оТ

при условии, что младшие разслева, равны:

11 на 1-23 тактах; 00 с (24tf) такта;

,01

11000091100010111001111101000

23

С°

000....000 10001111100001011011010

V-

Формула изобретения

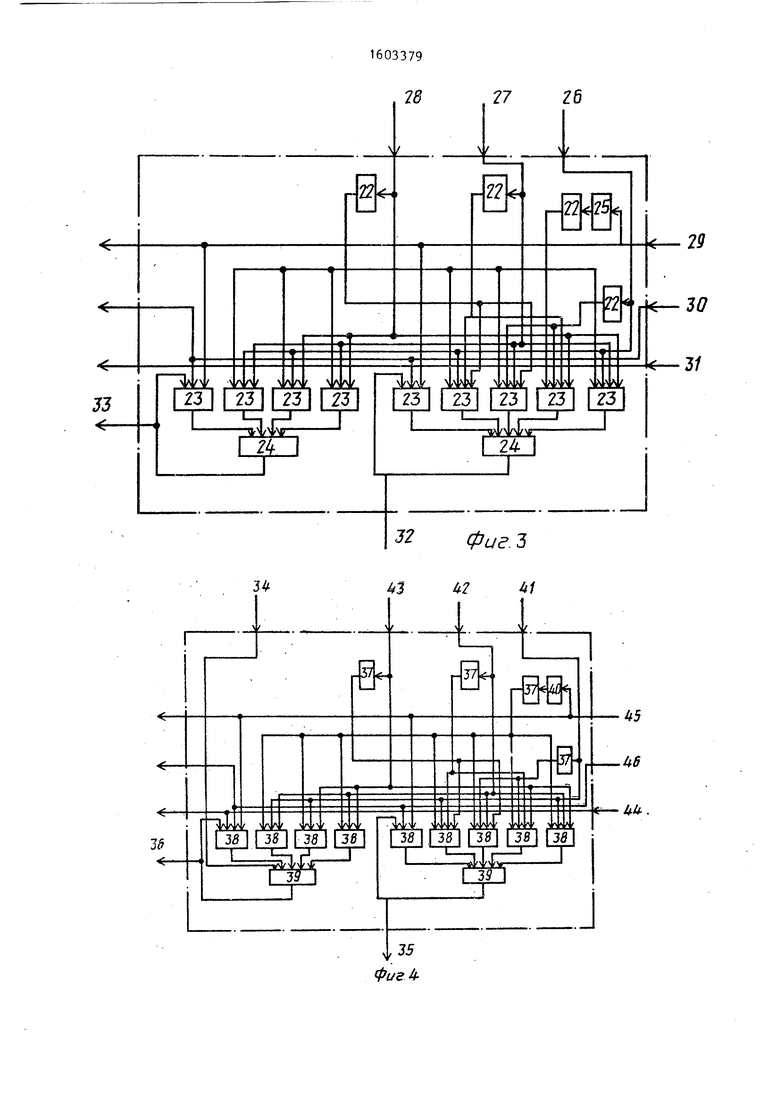

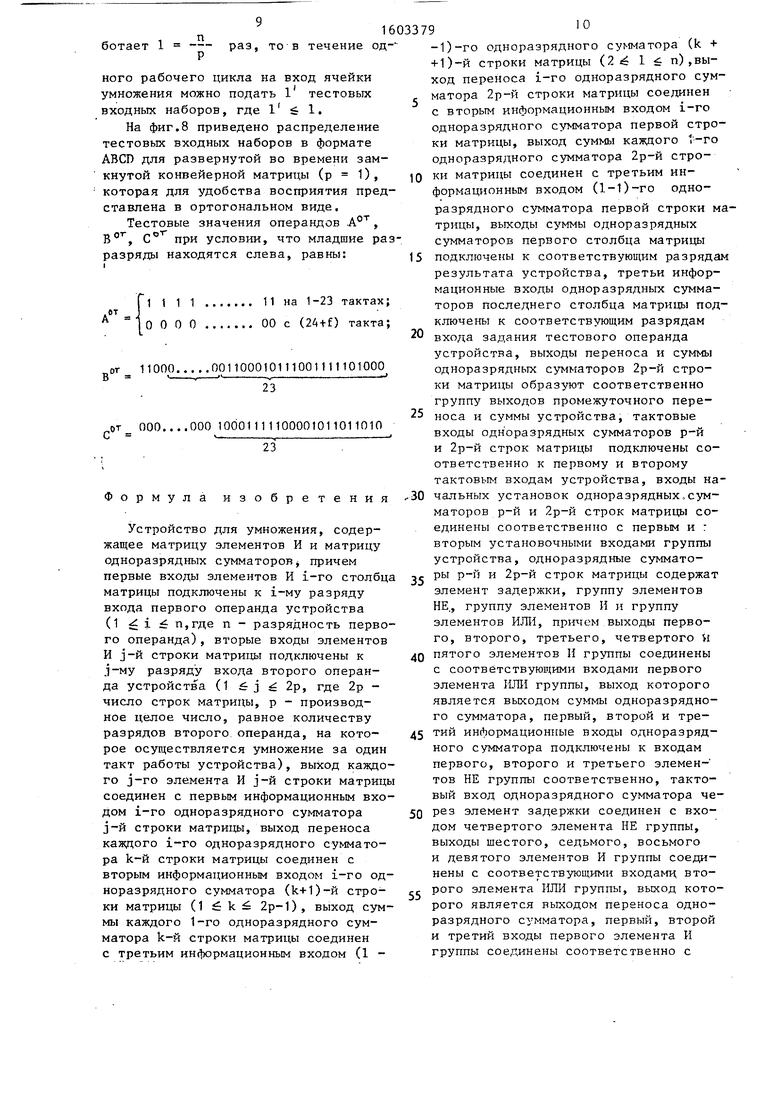

Устройство для умножения, содержащее матрицу элементов И и матрицу одноразрядных сз мматоров причем первые входы элементов И i-ro столбца матрицы подключены к i-му разряду входа первого операнда устройства ( п,где п - разрядность первого операнда), вторые входы элементов И j-й строки матрицы подключены к j-му разряду входа второго операнда устройства (1 j 2р, где 2р - число строк матрицы, р - производное целое число, равное количеству разрядов второго операнда, на которое осуществляется умножение за один такт работы устройства), выход каждого j-ro элемента И j-й строки матрицы соединен с первым информационным входом i-ro одноразрядного сумматора j-й строки матрицы, выход переноса каждого 1-го одноразрядного сумматора k-й строки матрицы соединен с вторым информационным входом i-ro одноразрядного сумматора (и+1)-й строки матрицы (1 ё k 2р-1), выход суммы каждого 1-го одноразрядного сумматора k-й строки матрицы соединен с третьим информационным входом (1 0

-1)-го одноразрядного сумматора (k + +1)-й строки матрицы (2 1 п),выход переноса i-ro одноразрядного сумматора 2р-й строки матрицы соединен с вторым информационным входом i-ro одноразрядного сумматора первой строки матрицы, выход суммы каждого 1--го одноразрядного сумматора 2р-й строки матрицы соединен с третьим информационным входом (1-1)-го одноразрядного сумматора первой строки матрицы, выходы суммы одноразрядных сумматоров первого столбца матрицы подключены к соответствующим разрядам результата устройства, третьи информационные входы одноразрядных сумматоров последнего столбца матрицы подключены к соответствующим разрядам входа задания тестового операнда устройства, выходы переноса и суммы одноразрядных сумматоров 2р-й строки матрицы образуют соответственно группу выходов промежуточного переноса и суммы устройства, тактовые входы одн оразрядных сумматоров р-й и 2р-й строк матрицы подключены соответственно к первому и второму тактовым входам устройства, входы на- 30 чальных установок одноразрядных.сумматоров р-й и 2р-й строк матрицы соединены соответственно с первым и : вторым установочными входами группы устройства, одноразрядные сумматоры р-й и 2р-й строк матрицы содержат элемент задержки, группу элементов НЕ,, группу элементов li и группу элементов ИЛИ, npiTOем выходы перво5

20

25

35

0

5

0

5

го, второго, третьего, четвертого Я пятого элементов И группы соединены с соответствующими входами первого элемента ИЛИ группы, выход которого является выходом суммы одноразрядного сумматора, первый, второй и третий информационные входы одноразрядного сумматора подключены к входам первого, второго и третьего элемен- тов НЕ группы соответственно, тактовый вход одноразрядного сумматора через элемент задержки соединен с входом четвертого элемента НЕ группы, выходы шестого, седьмого, восьмого и девятого элементов И группы соединены с соответствующими входам второго элемента ИЛИ группы, выход которого является выходом переноса одноразрядного сумматора, первый, второй и третий входы первого элемента И группы соединены соответственно с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических узлах. Цель изобретения - сокращение времени тестирования. Устройство содержит матрицу одноразрядных сумматоров 1.1 - 1.N, 2.1 - 2.N, 3.1 - 3.N, 4.1 - 4.N и матрицу элементов И 5. Сокращение времени тестирования достигается за счет того, что в течение одного рабочего цикла на вход ячейки умножения, включающей в себя соответствующие элементы И матрицы и сумматоры матрицы, можно подавать несколько тестовых входных наборов. 7 ил.

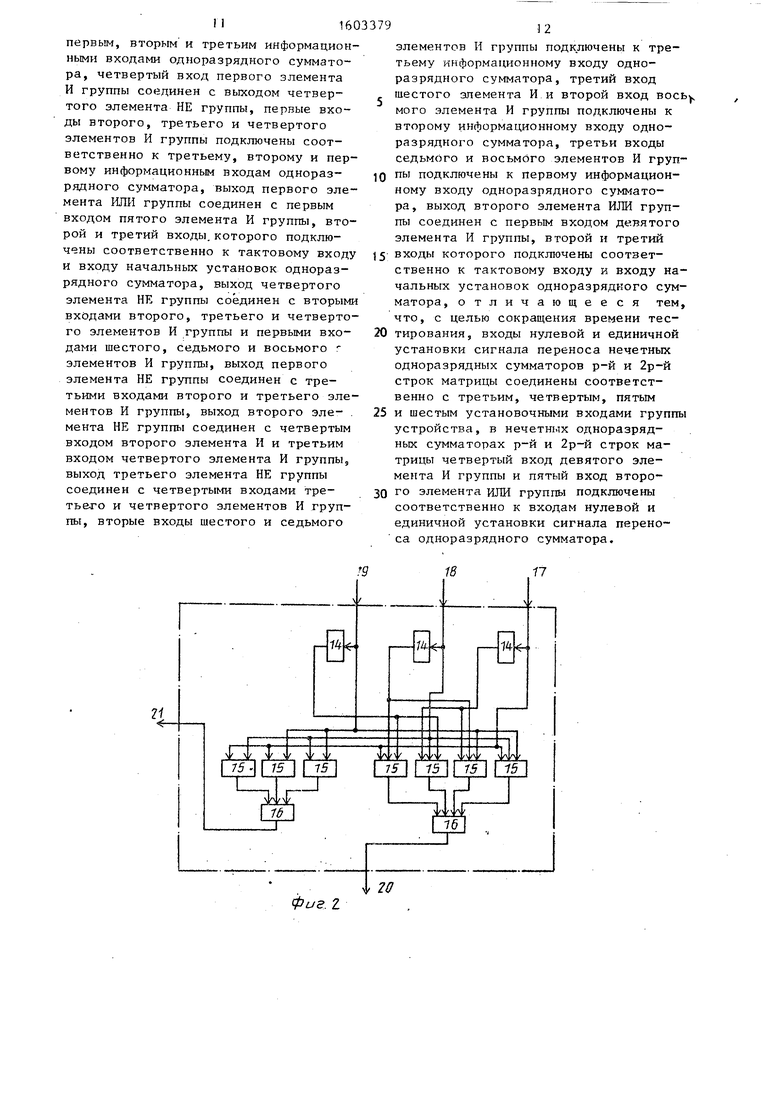

фиг. 2.

28

27

Z6

N

tfi hrj i i

7

Us «м

ь с

«

ss

- SАВСБ

Тест И

X

Фиг.7

| Множительное устройство | 1979 |

|

SU817705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1988-03-21—Подача