Изобретение относится к вычислительной технике, в частности к выполнению арифметических операций в высокопроизводительных многорегистровы вычислительных устройствах.

Целью изобретения является расширение функциональных возможностей за счет выполнения операции умножения в золотых 1-кодах.

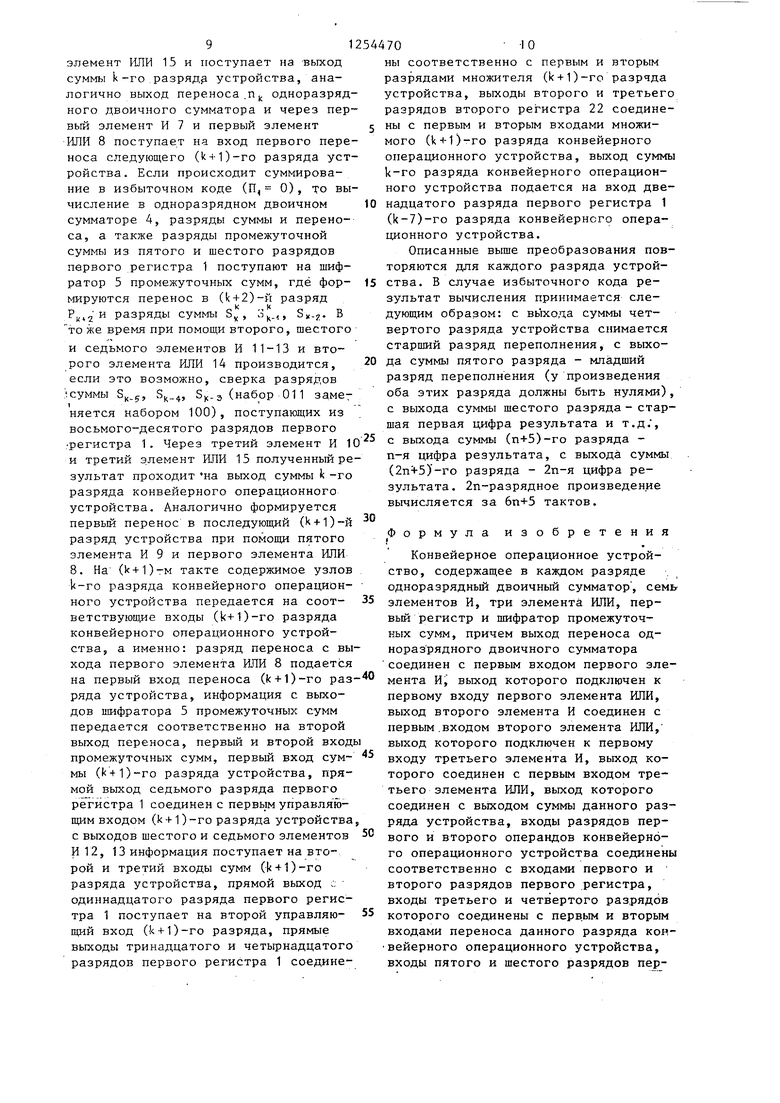

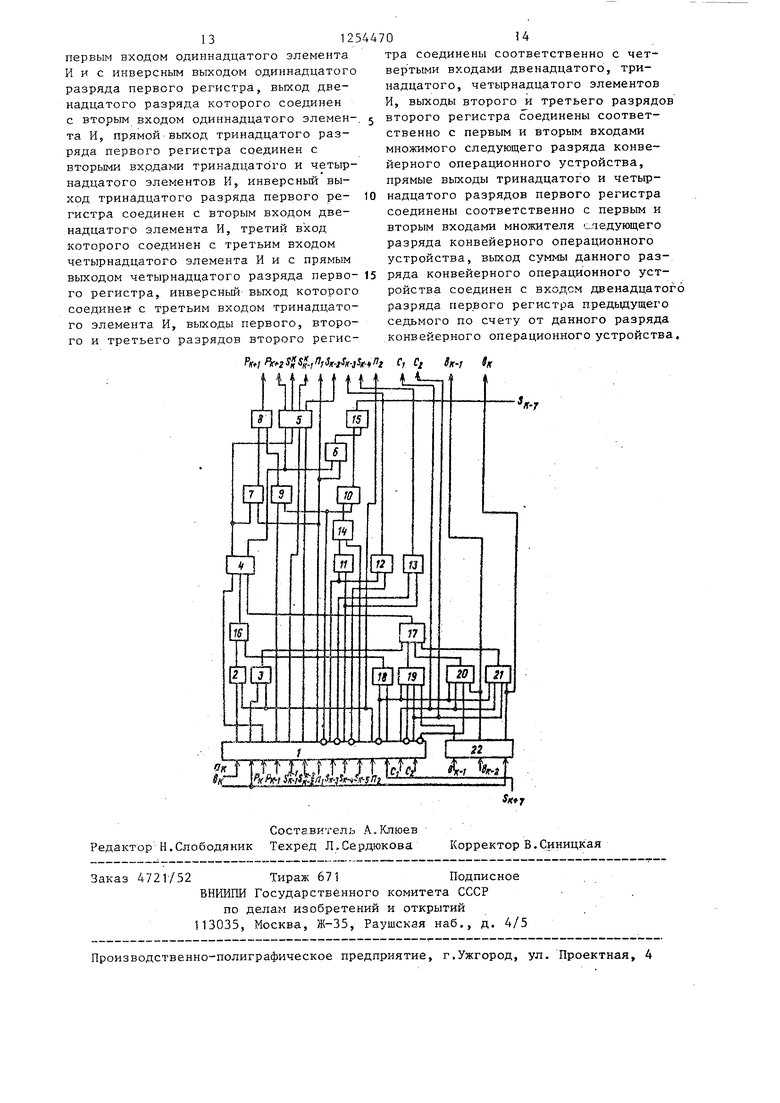

На чертеже представлена функциональная схема разряда конвейера, операционного устройства.

Конвейерное операционное устройство содержит 2п + 5 разрядов. Каждый разряд конвейерного операционного ycTpoiicTBa состоит из первого регистра 1, входы первого и бторого разрядов которого соединены соответственно с входами разрядов первого и второго операндов конвейера операционного устройства, входы третьего и четвертого разрядов первого регистра 1 соединены с первым и вторым входами переноса данного разряда конвейерного операционного устройства, входы пятого и шестого разрядов первого регистра 1 соединены с первым и вторым входами промежуточных сумм данного разряда конвейерного операционного устройства, вход седьмого разряда первого регистра 1 соединен с первым управляющим входом разряда конвейерного операционного устройства, входы восьмого - десятого разрядов первого регистра 1 соединены соответственно с первым - третьим входами сумм разряда конвейерного операционного устройства, вход одиннадцатого разряда первого регистра 1 соединен с вторым управляющим входом разряда конвейерного операционного устройства, вход двенадцатого разряда первого регистра 1 соединен с выходом суммы последующего седьмого по счету от данного разряда конвейерног операционного устройства, входы тринадцатого, четьфнадцатого разрядов первого регистра 1 соединены соответственно с первым и вторым входами множителя разряда конвейерного операционного устройства, выходы первого и второго разрядов регистра 1 соединены соответственно с первыми входами девятого и десятого элементов И 2,3, выход третьего разряда первого регистра 1 соединен с первым входом одноразрядного двоичного сумматора 4, выход суммы которого подключен к

5

0

первому входу шифратора 5 промежуточных сумм и к первому входу четвертого элемента И 6, выход переноса одноразрядного двоичного сумматора

4соединен с вторым входом шифратора

5промежуточных сумм и с первым входом первого элемента И 7, выход которого подключен к первому входу первого элемента {ЩИ 8, выход которого соединен с первым входом переноса следующего разряда конвейерного опе-г рационного устройства, второй вход первого элемента ИЛИ 8 подключен к выходу пятого элемента И 9, первый вход которого соединен с выходом четвертого разряда первого регистра

1, пятый и шестой разряды которого соединены соответственно с третьим и четвертым входами шифратора 5 промежуточных сумм, выходы которого соединены соответственное вторым входом переноса, с первым и вторым входами промежуточных сумм и с первым входом суммы следующего разряда конвейерного 5 операционного устройства, прямой выход седьмого разряда первого регистра 1 соединен с вторыми входами первого, четвертого элементов И 7,6, с первым управляющим входом следующего разряда конвейерного операционного устройства, инверсный выход седьмого разряда первого регистра 1 сое- ,динен с вторыми входами третьего и пятого элементов И 10,9, прямой выход восьмого разряда первого регистра 1 соединен с первыми входами второго и шестого элементов И 11, 12, инверсньй выход восьмого разряда первого регистра 1 соединен с первым входом седьмого элемента И 13, второй вход которого соединен с вторым входом второго элемента И 11 и подключен к прямому выходу девятого разряда первого регистра 1, инверсный выход которого соединен с вторым входом шестого элемента И 12, выход десятого разряда;первого регистра 1 соединен с вторым входом второго элемента ИЛИ 14, первый вход которого подключен к выходу второго элемента И 11, выход второго элемента ИЛИ 14. соединен с первым входом третьего элемента И 10, выход которого соединен с первым входом третьего элемента ИЛИ 15, второй вход которого подключен к выходу четвертого элемента И 6, выход третьего элемента ИЛИ 15 соединен с выходом суммы данного разряда конвейерного операционного уст0

5

0

5

0

5

ройства,. выходы шестого и седьмого элементов И 12, 13 соединены соответственно с вторым и третьим входами сумм следующего разряда конвейерного

операционного устройства, прямой вы- s мента И 21 и с прямым выходом четырход одиннадцатого разряда первого регистра 1 .соединен с вторым управляющим входом следующего разряда конвейерного операционного устройства, с вторыми входами девятого и десятого элементов И 2,3, вькоды . которых соединены соответственно с первыми входами четвертого и пятого элементов ИЛИ 16,17, выходы которых соединены соответственно с вторым и третьим входами одноразрядного двоичного сумматора 4, второй вход чет- .вертого элемента ИЛИ 16 соединен с выходом одиннадцатого элемента И 18,

надцатого разряда первого регистра 1, (инве рсный выход которого соединен с третьим входом тринадцатого элемента И 20, выходы первого - третьего раз-

10 рядов .второго регистра 22 соединены соответственно с четвертыми входами двенадцатого - четырнадцатого элементов И 19-21, вькоды второго и третьего разрядов второго регистра 22 соеJ5 динены соответственно с первым и вторым входами множимого следующего разряда конвейерного операционного устройства, прямые выходы тринадцатого и четырнадцатого разрядов первого

мента ИЛИ 17 соединены соответственно с выходами двенадцатого - четырнадцатого элементов И 19 - 21, первые входы которых связаны с первым входом

второй - четвертый входы пятого эле- 20 Регистра 1 соединены соответственно

с первым и аторым входами множителя следующего разряда конвейерного операционного устройства, выход суммы данного разряда конвейерного операодийнадцатого элемента И 18 и с ин- -25 ционного устройства соединен с вхо- версным выходом одиннадцатого разря- двенадцатого разряда первого ре- да первого регистра 1, выход двенад- гистра предыдущегр седьмого по счету цатого разряда первого регистра 1 соединен с вторым входом одиннадцатого элемента И 18, прямой выход три-30 надцатого разряда первого регистра 1 соединен с вторыми входами тринадцатого и четырнадцатого элементов И 20, ,21, инверсный выход тринадцатого разот данного разряда конвейерного операционного устройства.

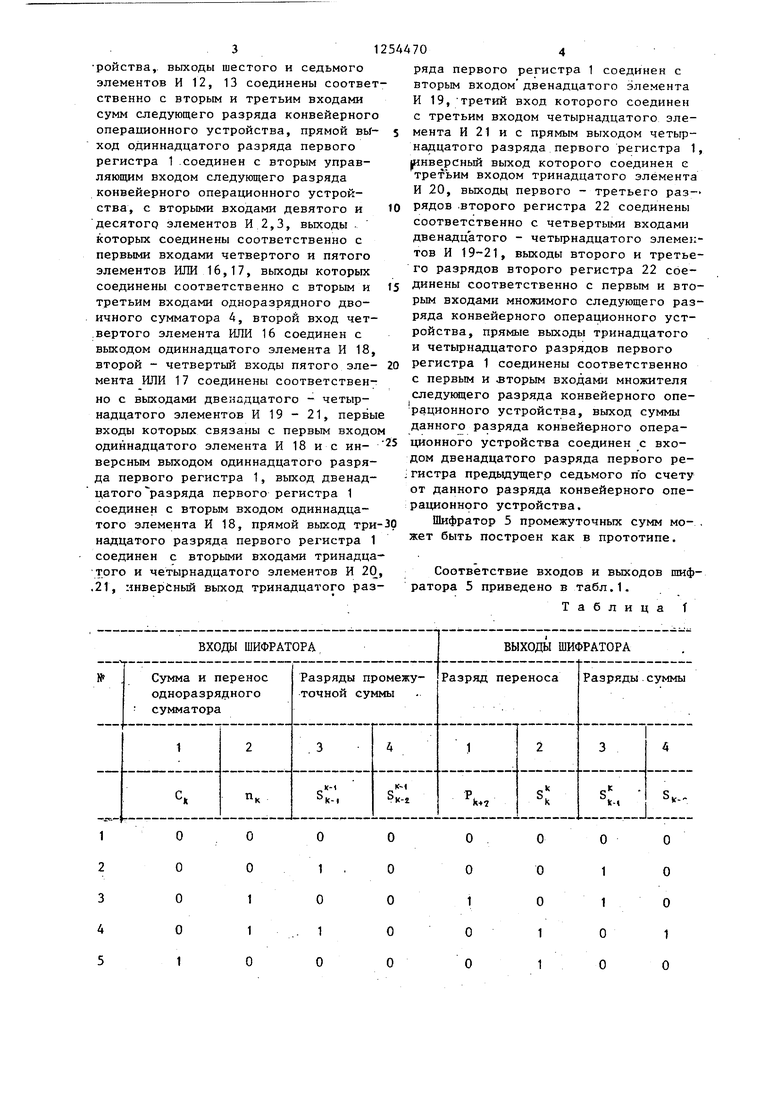

Шифратор 5 промежуточных сумм может быть построен как в прототипе.

Соответствие входов и выходов шифратора 5 приведено в табл.1.

О О О О 1

О О

1 1

о

о 1

о 1 о

125АА704

ряда первого регистра 1 соединен с вторым входом двенадцатого элемента И 19, Третий вход которого соединен с третьим входом четырнадцатого эленадцатого разряда первого регистра 1, (инве рсный выход которого соединен с третьим входом тринадцатого элемента И 20, выходы первого - третьего раз-

рядов .второго регистра 22 соединены соответственно с четвертыми входами двенадцатого - четырнадцатого элементов И 19-21, вькоды второго и третьего разрядов второго регистра 22 соединены соответственно с первым и вторым входами множимого следующего разряда конвейерного операционного устройства, прямые выходы тринадцатого и четырнадцатого разрядов первого

ционного устройства соединен с вхо- двенадцатого разряда первого ре- гистра предыдущегр седьмого по счету

от данного разряда конвейерного операционного устройства.

Шифратор 5 промежуточных сумм может быть построен как в прототипе.

ционного устройства соединен с вхо- двенадцатого разряда первого ре- гистра предыдущегр седьмого по счету

Соответствие входов и выходов шифратора 5 приведено в табл.1.

Таблица Т

о о 1 о о

о о о 1

1

о

1 1 о о

о о о 1 о

Примечание. Знаком - обозначено неопределенное значение функ- ,ции на данном наборе.

При выполнении операций в избыточных кодах операнды представлены в минимизированной форме, содержащей не более двух единиц подряд. Вычисле ния выполняются, начиная со старших разрядов, разряды результата можно использовать по мере их получения, : не дожидаясь окончания операции. В отличие от 1-кодов Фибоначчи веса разрядов золотых 1-кодов представляют собой степени основания системы с, .

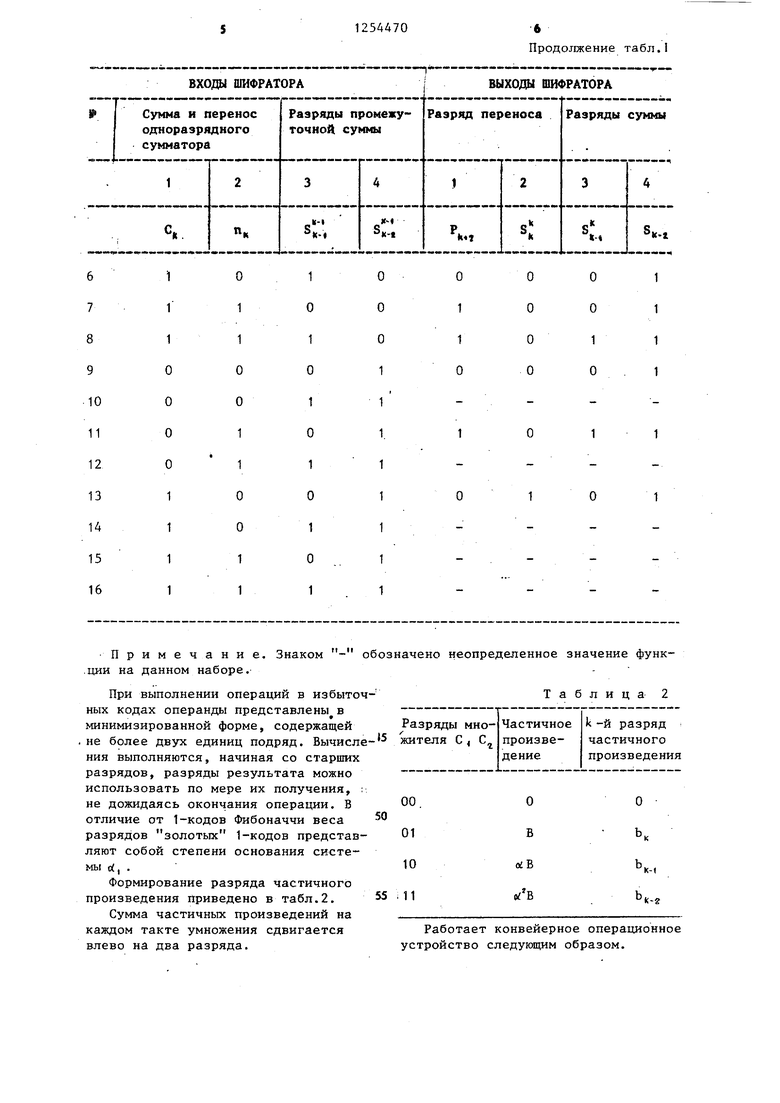

Формирование разряда частичного произведения Приведено в табл.2.

Сумма частичных произведений на каждом такте умножения сдвигается влево на два разряда.

Продолжение табл.

Таблица 2

Работает конвейерное операционное устройство следукицим образом.

7

На входы П, и П первого разряда устройства подаются управляющие сиг |налы, задающие режим работы устройства при обработке данной пары one- рандов. Если П,П2 00, то Выполняется умножение золотых 1-кодов

(В,( Cj); если П)П2 01, то выполняется: суммирование золотых 1-кодов или 1-кодов Фибоначчи (А« + S,);

если П,П- 11, выполняется суммирова- ю ройства на входы тринадцатого и чение двоичных кодов (А „ + Вл).

На тактовые входы первого регистра 1 синхронизирующие сигналы подаются постоянно, на тактовые входы второго регистра 22 - только тогда, 15 когда начинается выполнение новой операции умножения и на его информационные входы подаются цифры множимого. Если выполняется операция cyMMii- рования, на входы устройства OK и Ь 20 (k 1, 2, 3,...п)слагаемые подаются, начиная с первого разряда устройства; если операция умножения, то на входы Ьц ( k п - 1,...,, п н- 5) устройства множимое подается, начиная с. 25 (п - 1)-го разряда устройства, а цифг- ра множителя подается попарно каждый девятый такт на входы С, и С первого разряда устройства. В начале новой операции умножения на первом такте зо должна производиться установка в ноль первого 1 и второго 2 регистров всех разрядов устройства для формирования нулевой начальной суммы частичных произведений, а на девятом j такте должна начинаться подача операндов . При выполнении операции умно- - жения конвейерное операционное устройство занято только каждый девятьш такт, поэтому в промежутках между до этими тактами устройство мохсет также выполнять операции суммирования.

Для примера рассмотрим работу k-ro (k 1,2,3,..., n + 5) разряда конвейерного операционного устрой- 45 ства.

Пусть на В-м такте осуществляется прием k-X разрядов операндов А и 5 на входы Ох, и Ь первого и второго разрядов первого регистра 1 и разряда Ь на вход третьего разряда второго регистра 22 k-ro разряда устройства. Одновременно из предьщущего (k-l)-ro разряда устройства на выходе с третьего по одиннадцатьш первого 55 регистра 1 поступают соответственно перенос из (k-2)-ro разряда в 1с-й разряд Р|, перенос из (k-1)-ro раз50

ряда в ()-й разряд Р,,, два разряда промежуточной суммы , S.., первый управляющий сигнал П,, разряды суммы SK-,, Sx.4 3„.5, второй управляющий сигнал rij, из последующего

(k+7)-ro разряда устройства на вход двенадцатого разряда первого регистра 1 поступает разряд суммы S, из предыдущего (k-1)-ro разряда уст50 5 о о

5

5

0

.тырнадцатого разрядов первого регистра 1 поступают разряды множителя С, Cj, на входы первого и второго разрядов регистра 22 из предыдущего (k-l)-ro разряда устройства поступа- ю Г разряды множимого Ь,, и Ь.., (при условии, что второй регистр 22 тактируется, т.е. начинается новая операция умножения, иначе во втором регистре 22 уже хранятся соответствующие разряды множимого). В зависимости от

сигналов П, и П на входы одноразрядного двоичного сумматора 4 через четвертый и пятый элементы ИПП 16, 17 поступают либо t (П 1, т.е. производится операция суммирования), либо (разряд суммы частичных произведений) и разряд очередного частичного произведения (Ilg О, т.е. призводится операция умножения). Формирование разряда очередного частичного произведения происходит в зависимости от цифр множителя С С посредством выбора одного из разрядов множимого Ь| , Ъ , хранящихся во втором регистре 22, при помощи двенадцатого - четьфнадцатого элементов И 19-21. Тем самым осуществляется умножение очередной цифры множимого на два разряда множителя и относительный сдвиг очередного acтйчнo- го произведения по отношению к сумме на 0-2 разряда (см.табл.2). В свою очередь сумма частичных произведений каждый такт умножения сдвигает на два разряда влево по конвейерному операционному устройству при яомощи обратной связи, соединяющей выход суммы (V+7)-ro разряда устройства с входом S данногоk-го разряда устройства.

После выбора слагаемых осуществляется суммирование либо в золотом 1-коде или 1-коде Фибоначчи (П, 0) , либо в двоичном коде (П, 1). Если Е 1, то выход суммы С одноразрядного двоичного сумматора 4 проходит через четвертый элемент И 6 и третий

элемент ИЛИ 15 и поступает на -выход суммы k-ro,разряду устройства, аналогично выход переноса.п одноразрядного двоичного сумматора и через первый элемент И 7 и первый элемент ИЛИ 8 поступает на вход первого переноса следующего (k+1)-ro разряда устройства. Если происходит суммирование в избыточном коде (П, 0), то вычисление в одноразрядном двоичном сумматоре 4, разряды суммы и переноса, а также разряды промежуточной суммы из пятого и шестого разрядов первого регистра 1 поступают на шифратор 5 промежуточных сумм, где фор- мируются перенос в (k+2)-й разряд

К К

Р|д2 и разряды суммы S , ц.,, Зх-г- В то же время при помощи второго, шестого

и седьмого элементов И 11-13 и второго элемента ИЛИ 14 производится, если это возможно, сверка разрядов .суммы , З.э (набор 011 заменяется набором 100), поступающих из восьмого-десятого разрядов первого /регистра 1. Через третий элемент И 1 и третий элемент ИЛИ 15 полученный результат проходит на выход суммы k-го разряда конвейерного операционного устройства. Аналогично формируется первый перенос в последующий (1 + 1)-й разряд устройства при помощи пятого элемента И 9 и первого элемента ИЛИ 8. На (k+1)-M такте содержимое узлов k-ro разряда конвейерного операцион- него устройства передается на соот- ветствующие входы (k+1)-ro разряда конвейерного операционного устройства, а именно: разряд переноса с выхода первого элемента ИЛИ 8 подается на первый вход переноса (k + 1)-ro раз ряда устройства, информация с выходов шифратора 5 промежуточных сумм передается соответственно на второй выход переноса, первый и второй вход промежуточных сумм, первый вход сум- мы ()-ro разряда устройства, прямой выход седьмого разряда первого регистра 1 соединен с первым управляЪ- щим входом (k +1) -го разряда устройства с выходов шестого и седьмого элементов И 12, 13 информация поступает на второй и третий входы cyMi-i Ck + O-ro разряда устройства, прямой выход с одиннадцатого разряда первого регистра 1 поступает на второй управляю- щий вход (k+1)-ro разряда, прямые выходы тринадцатого и четырнадцатого разрядов первого регистра 1 соедине

ны соответственно с первым и вторым разрядами множителя (k+1)-ro разряда устройства, выходы второго и третьего разрядов второго регистра 22 соединены с первым и вторым входами множимого (k+1)-ro разряда конвейерного операционного устройства, выход k-ro разряда конвейерного операционного устройства подается на вход двенадцатого разряда первого регистра 1 (k-7)-ro разряда конвейерного операционного устройства.

Описанные выще преобразования повторяются для каждого разряда устройства. В случае избыточного кода результат вычисления принимается следующим образом: с вьЬсода суммы четвертого разряда устройства снимается старший разряд переполнения, с выхода суммы пятого разряда - младший разряд переполнения (у произведения оба этих разряда должны быть нулями), с выхода суммы шестого разряда - старшая первая цифра результата и т.д., с выхода суммы (п+5)-го разряда - п-я цифра результата, с выхода суммы ()-го разряда - 2п-я цифра результата. 2п-разрядное произведение вычисляется за 6п+5 тактов.

Формула изобретения

Конвейерное операционное устройство, содержащее в каждом разряде одноразрядный двоичный сумматор , семь элементов И, три элемента ИЛИ, первый регистр и шифратор промежуточных сумм, причем выход переноса од- нораз рядного двоичного сумматора

соединен с первым входом первого элемента И выход которого подключен к первому входу первого элемента ИЛИ, выход второго элемента И соединен с первым.входом второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с выходом суммы данного разряда устройства, входы разрядов первого и второго операндов конвейерного операционного устройства соединены соответственно с входами первого и второго разрядов первого регистра, входы третьего и четвертого раз.рядОв которого соединены с перв.ым и вторым входами переноса данного разряда конвейерного операционного устройства, входы пятого и шестого разрядов перп

-вого регистра соединены с первым и вторым входами промежуточных сумм данного разряда конвейерного операционного устройства, вход седьмого разряда первого регистра соединен с первым управляющим входом разряда конвейерного операционного устройству, входы восьмого, девятого и десятого разрядов первого регистра соединены соответственно с первым,

вторым и третьим входами сумм разряда конвейерного операционного устройства, выход третьего разряда первого регистра соединен с первым входом одноразрядного двоичного сумматора, выход суммы которого подключен к первому входу шифратора промежуточных сумм и к первому входу четвертого элемента И, вых.од которого, соединен с вторым входом третьего элемента ИЛИ, выход переноса одноразряд ного двоичного сумматора соединен с вторым входом шифратора промежуточ- ных сумм, выход четвертого разряда первого регистра соединен с первым входом пятого элемента И, выход кото Фого подключен к второму входу первого элемента ИЛИ, выход которого со единен с первым входом переноса следующего разряда конвейерного операционного устройства, выходы пятого и шестого разрядов первого регистра соединены соответственно с третьим и четвертым входами шифратора промежуточных сумм, прямой выход седьмого разряда первого регистра соединен с вторыми входами первого и четвертого элементов И и с первыь- управляющим-входом следующего разряда конвейерного операционного устройства, ин .версный выход седьмого разряда первого регистра соединен.с вторыми входами третьего и пятого элементов И, прямой выход восьмого разряда первого регистра, соединен с первыми входами второго и шестого элементов И, инверсный выход восьмого разряда первого регистра соединен с первым входом седьмого элемента И, второй вход которого соединен с вторым входом второго элемента И и подключен к прямому выходу девятого разряда первого регистра, инверсный выход которого соединен с вторым входом шестого эле мента И, выход десятого разряда первого регистра соединен с вторым входом второго элемента ИЛИ, выходы шиф ратора промежуточных.сумм соединены

5447012

соответственно с вторым входом переноса, с первым и вторым вxoдa fи промежуточных сумм и с первым входом суммы следующего разряда конвейерно- 5 го операционного устройства, выходы шестого и седьмого элементов И соединены соответственно с вторым и третьим входами сумм следующех о разряда конвейерного операционного устрой10 ства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции умножения в золотых 1-кодах, оно дополнительно содержит в

15 каждом разряде второй регистр, семь элементов И, два элемента ИЛИ, причем входы первого и второго разрядов второго регистра соединены соответственно с первым и вторым входами

20 множимого данного разряда конвейерного операционного устройства, вход третьего разряда второго регистра соединен с входом второго операнда конвейерного операционного устрой25

30

35

40

45

50

55

ства, первые входы девятого к десятого элементов И соединены соответственно с выходами первого и второго разрядов первого регистра, вход одиннадцатого разряда которого соединен с вторым управляющ11м входом разряда конвейерного операционного устройства, вход двенадцатого разряда первого регистра соединен с выходом суммы последующего седьмого по счету от данного разряда конвейерного операционного устройства, входы тринад- цатого и четьфнадуатого разрядов первого регистра соединены соответственно с первым и вторым входами множителя данного разряда конвейерного операционного устройства, прямой выход одиннадцатого разряда первого регистра соедр1нен с вторым управляюпщм йхо- дом следующего разряда конвейерного операционного устройства и с вторыьш входами девятого и десятого элементов И, вьгходы которых соединены соответственно с первыми входами четвертого и пятого элементов ИЛИ, выходы

КОТОРЫХ соединены соответственно с вторым и третьим входами одноразряднего двоичного сумматора, второй вход четвертого элемента ИЛИ соединен с выходом одиннадцатого элемента И, второй, третий и четвертый входы пятого элемента ИЛИ соединены соответ- ственко с выходами двенадцатого, тринадцатого, .четьфиадцатого элементов И, первые входы которых соединены с

первым входом одиннадцатого элемента Икс инверсным выходом одиннадцатого разряда первого регистра, выход двенадцатого разряда которого соединен с вторым входом одиннадцатого элемента И, прямой вьтход тринадцатого разряда первого регистра соединен с вторыми вх.одами тринадцатого и четырнадцатого элементов И, инверсный выход тринадцатого разряда первого ре- гистра соединен с вторым входом двенадцатого элемента И, третий вход которого соединен с третьим входом четырнадцатого элемента И и с прямым выходом четырнадцатого разряда перво- го регистра, инверсный выход которого соедине с третьим входом тринадцатого элемента И, выходы первого, второго и третьего разрядов второго регисУК Г

Составитель А.Клюев Редактор Н.Слободяник Техред Л.Сердюкова Корректор В.Синицкая

Заказ 472Г/52 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

тра соединены соответственно с чет- вер тыми входами двенадцатого, тринадцатого, четырнадцатого элементов И, выходы второго и третьего разрядов второго регистра с оединены соответственно с первым и вторым входами множимого следующего разряда конвейерного операционного устройства, прямые выходы тринадцатого и четырнадцатого разрядов первого регистра соединены соответственно с первым и вторым входами множителя следующего разряда конвейерного операционного устройства, выход суммы данного разряда конвейерного операционного устройства соединен с входом двенадцатог разряда первого регистра предыдущего седьмого по счету от данного разряда конвейерного операционного устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Конвейерное устройство для умножения шестнадцатиразрядных чисел | 1984 |

|

SU1291970A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

Изобретение относится к облас ; . ти вычислительной техники и предназначено для вьтолнения арифметических операций в высокопроизводительных многорегистровых вычислительных устройствах. Целью изобретения является расширение функциональных возможностей за счет выполнения операции умножения в золотых 1-кодах. Поставленная цель достигается тем, что конвейерное операционное устройство, содержащее в каждом разряде регистр, одноразрядный двоичный сумматор, шифратор промежуточных сумм, элементы ИЛИ и элементы И, дополнительно содержит второй регистр, элементы ИЛИ и элементы И с соответствующими связями. Конвейерное операционное уст- .ройство осуществляет суммирование . двоичных кодов, 1-кодов Фибоначчи, золотых 1-кодов, а также умножение золотых 1-кодов. 1 ил., 2 табл. с S (Л

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-16—Подача