(54) ВЫЧИСЛИТЕЛЬ}ЮЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1988 |

|

SU1569824A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

1

Изобретение относится к вычиспительпой технике, в частности к выпопнению арифметических операций в многорегистровых арифметических устройствах, выпопненных на уз пах с большой степенью интеграции.

Известно матричное устройство Дпя ЦВМ, содержащее блоки сложений и вычитания с шунтирующим управлением. Каждый блок имеет два входа операндов, вход,о переносов, управпяющие входы Дпя сложения, вычитания или шунтирования, и выход переноса, а также выход суммы игш разности 1.

С помощью таких устройств возможно is перемножение Е пар чисел, однако перемножение последовательности из Р чисел осуществляется в несколько этапов, что и снижает нх производительность.

Наиболее близким по технической сущ-20 нести к предлагаемому является устройство Для одноврем ми1ого выполнения арифметических onepamift над множеством чи- сел, состоящее из п вычислительных блоков, кажлый из которых содержит первый регистр множимого, первый регистр мно- нтеля, первый рюгистр частичных произведений, первый сумматор-вычисли те гть, причем информационные входы регистра множителя первого вычислительного бпо ка подключены к соответствующим информационным входам устройства, управляющий вход объединен с управляющим входом регистра множимого и подкшочен к тактовой щине устройства, информационные входы регистра множимого подключены к соответствующим информационным входам устройс:тва.

С помощью этого устройства возможно перемножение пос ледова те гтьн ости из С чисел. При этом К п -разрядное произведение Е бп разрядных чисел может быть

получено за +К тактов, где К ° 1,

выражения, количество тактов, необходимое для перемножения поспедовательности Р чисел, мало зависит от требуемой ТОЧНОСТИ резугсьтата вычислений, а зависит в основном от количества опера1Щ.ов, входящих в арифметическое выражение, и р азр5Здности п этих операндов. Это объ-. ясняется тем, что независимо от того, сколько разрядов мы хотим получить на выходе арифметического устройства, в устройстве арифметического выражение будет вычисляться всегда с 2п разрядной точностью, так как арифметические операции над множеством чисеп в этом устройстве выполняется с мпадших разрядов. Вместе с тем попучение Еп -разрядного произведения En - разрядных чисеп требуется лишь в йекоторых специапизнрованных вычисгштепях, в основном же требуется попучение пишь п iimi 2 п старших разр5Щов произведения 2. Основным недостатком известного устройства является то, что с использованием его арифметическое выражение вычисляется с точнос1ъю до младшего разряда результата, хотя практически почти всегда необходимы только п старших разрядов результата. Это приводит к существенному увеличе}5ию времени вычислени.я сданого арифметического выражения я, таким образом, к значит-епьяо уменьшению производительности устройства в цел Цель изобретения .- пов1з1шение быст роДействия устройства. Поставленная цель достигается тем, что в каждый 1 -и вычисгштельньй блок введены второй, третий, четвертый регис ры множимого, второй, третий, четвертый пятый, шестой, седьмой и восз:..мой регист рымножителя, второй , третий и четверты регистры частичшлх произведет и, первый Второй, третий и четвертый регкстрь : переносов, первый, второй, третий, четвертый и пятый регистры поправок, первый, второй, третий, четвертый и нятый регис ры результата, первый, второй, третий и четвертый регистры переноса результата первый, второй, третий и четвертый регистры веса очередной цифры множимого, первый, второй и третий :)егистры промежуточного результата, первый и вт рюй триггеры Делителя, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой Tpiiprepbi формирования окончательного розу|Пзтата, второй сумматор-вычитатега, первый, второй, тре тий и четвертый сумматоры /узел dippMHрования поправок, коммутац| и, лиср ратор, сумматор по модулю два, роворсивный счет-п;к, у;ричем в кавддом гм.глис:лительном блоке рыходы nejiBnro и гчо-рого регистров м -о;к; тоия соолиггцы соответственно с первыми и вторыми входами узла фор жироваш5я поправок, третий вход которого соединен с выходом мпадшего разряда первого регистра кшожимого и первым входом блока комм тации, выходы узла формирования поправок соединены соответственно с информадионныьГИ входами первого и второго регистров поправок, выходы KOTopbiX соединены соответственно с информационными входами первого сумматора, выходы переноса и суммы которого соединены соответственно с информадионными входами третьего и четвертого регистров поправок, выходы третьего регистра поправок соединены соответственно с информап.иокнъ ми входами пятого регистра поправок, lybixoPii первого регистра УШО);,ЙМОГО соединелЪ соот- зетственно с входа MI; первой г-руппы бло- ка коммутации, входы гртппы ко- ....1 ,j торого соединены с.оо7Ветст7- -енно с выхо дами первого регистра веса очередной цифры множимого и информационными входами второго регистра веса очередной 1.ШФРЫ множимого, выходы бгЁОка к.омму та.ции соединены соответственно с ннфор- маппотшБПуп; вхсдамп х-ч-орого регистра множимого. BbiXQiJi.. которого лгюятхнены соответственно с информаиисчн.гми входами третьего регис-г-ра г-пюжг.ьКТо. выходы которого соединен.- соогветсттземмо с ин-формационными входгч-И го: вертогс регистра множимого, выходы КОГОрОГО СОЭ Дйнены соответстЕенно с информад -энными входами перво1х регистра мвот нмого ().ГО Bbiirac ли тельного блока, вьиоды второго регистра веса очередной цифры множимого соединены соответственно с информационными входа ли третьего ре гйстра веса очередной цифры множимого,, выходы которого соедине1 ы соответ- ственно с информационными входами четвертого регистра веса очередной цифры л-шожимого, выходы которого соединены соответственно с информационными входами первого регистра веса очередной цифры множимого ()-го вычислительного блока5 входы младших разрядов третьего и четвертого регистров множителя соединены соответственно с выходами стар шего и младшего разрядов первого регистра переноса результата (i+l)ro вычислительного блока, входы старших разрядов третьего и четвертого регистров множителя соединены соответственно с выходами первого и второго регистров множителя, выходы третьего и четвертого регистров множителя соединены соответственно с информационными входами

пятого и luecToro регистров мможитеня, выходы которых соединены соответственно с информацно1 ными входами седьмого и восьмого регистров множитепя, выходы которых соединены соответстве1 но с информационными входами первого и второго регистров множитепя (i+l)-ro вычислитепьного бпока, выходы первого регистра частичного произведения соединены соответственно с информационными входами первой группы нервого сумматора-вычитая-епя, информационные входы второй группы которого соединены соответственно с выходами первого регистра пе,р 2носа, выход суьдмы первого сумматора-вычитатепя соединен с информационным входом второго регистра частичного произведения, выхо/лы которого соединены соответственно с информационными вхо дг1ми первой группы второго сумматоравычитатепя, ин(}юрмационные входы второй группы которого соединены соответственно с выходами второго регистра множимого, а информашшнные входы третьей группы - соответственно с выходами второго регистра переноса, информационный вход которого соединен с выходом переноса первого сумматора-вычитатедя, выход младшего разряда четвертого регистра множитепя соединен с первым управляюшим входом второго сумматора-вычитателя, второй управляющий вход которого соединен с выходом младшего разряда третьего регистра множитепя, выход суммы второго сумматора-вычитателя соединен с информационным входом третьего регистра частичного произведения, выходы которого соединены соответственно с инс{юрмационными входами первой группы второго сумматора, информационныв входы второй группы которого соединены соответственно с выходами четвертого регистра поправок, а входы третьей группы - соответственно с выходами третьего регистра переноса, информационный вход которого соединен с выходом переноса Второго сумматора- вычнтатепя, выход перюноса второго сумматора соединен с информационным входом четвертого регистра переноса, а выход суммы - с ни- формационным входом четвертого регистра частичного произведения, выходы которого соединены соответственно с информационными входа я первой группы тре- тьего сумматора, ин4юрмационные входы второй группы которого соединены соот ветственно с (5/1.а1ли пятого регистра поправок, а ннфор слчонные входы третьей группы соот.к: гственно с выхода -

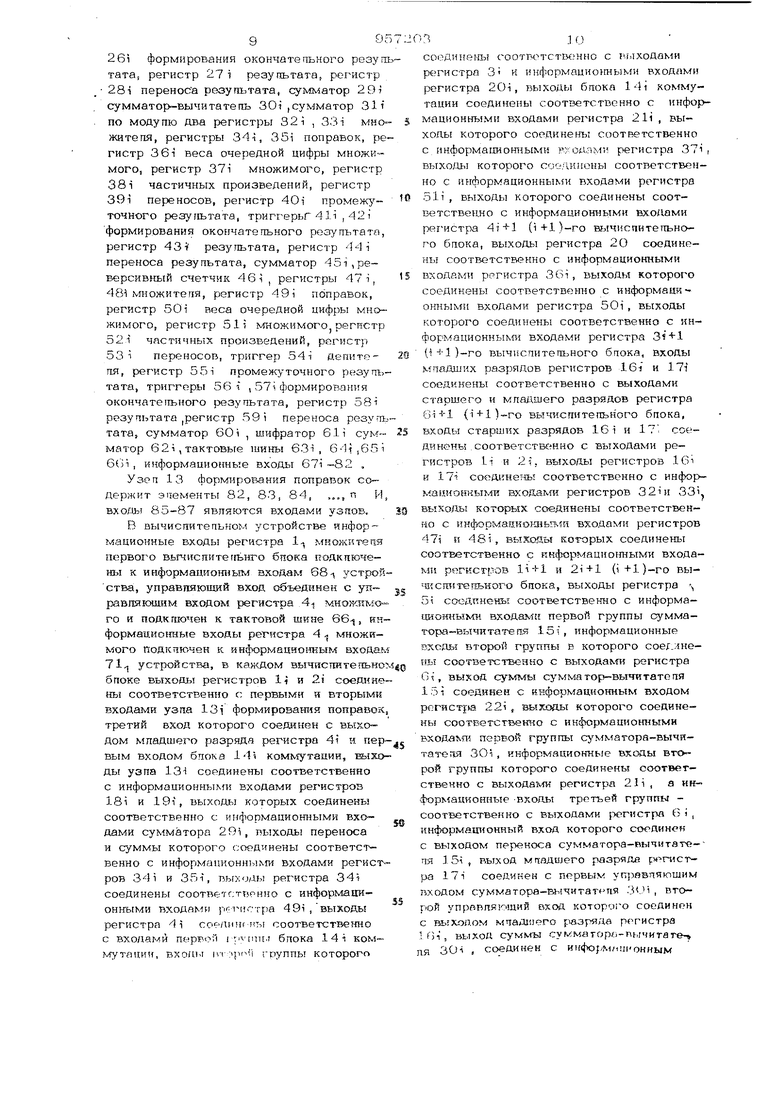

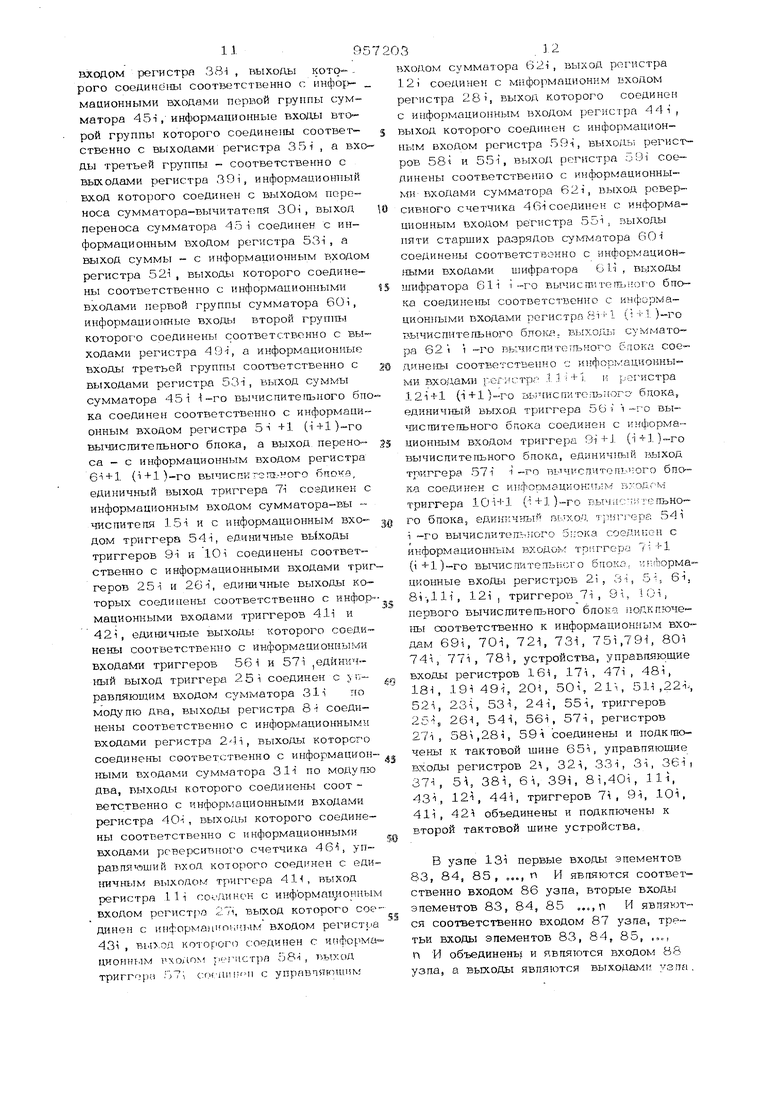

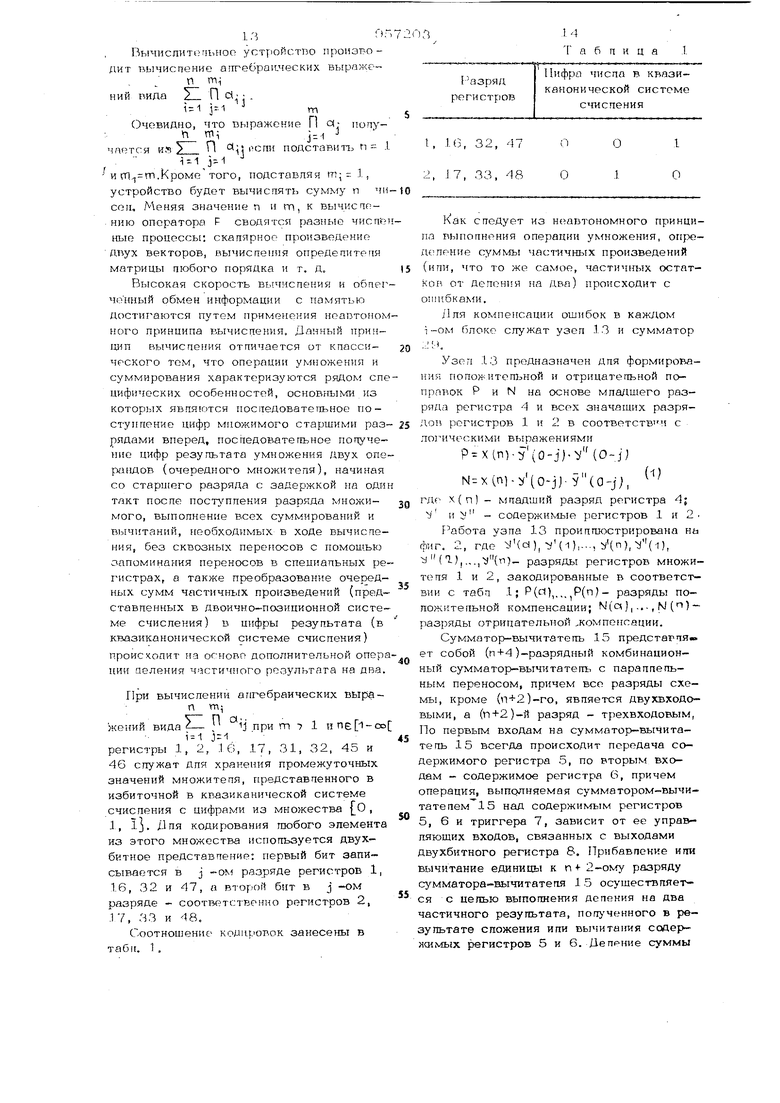

о:;ё

ми четвертого регистра переноса, выход суглмы третьего сумматора -го вычислительного блока соединен с информационным входом первого регистра частичного произведения (i +1)-го вычислитетзного бпока, а выход пер-:иоса - с инфорMauPiOHi№iM входом первого регистра переноса {i+l)-ro вычисли те пьного бпока, единичный выход первого триггера делителя соединен с информационным входом первого -Сумматора-вычислите пя и с информационным входом второго триггера делителя, единичные выходы первого н второго триггеров формирования окончательного резупьтата соединены соответственно с информационными входами третьего и четвертого триггеров формирования окончательного результата, единич сые вьгходы которых соединены соответCTJjeHKO с информационными входами пятго и шестого триггеров формирования окончатегп: ного результата, единичные выходы которых соединены соответственно с инг|юрмационными входами седьмого восьмого триггеров формирования оконча,тельного результата, единичный выход третьего триггера формирования окончатеш ного результата соединен с управляющим входом сумматора по модулю два, выходы первого регистра промежуточ гого результата соединены соответственно с и}гформацианными входамт: второго регистра нромел уточного результата, выходы которого соединены соответственно с инфopмaциoнны п{ входами сумматора по модупю два, выходы которого соединены соответственно с информационными входами третьего регистра промежуточiioro результата, выходы которого соединены соответственно с информационными входами реверсивного счетчика, управляющий вход которого соединен с единичным выходом пятого триггера формирования окончательного результата, выход первого р егистра результата соединен с информационным входом второго регистра рехзультата, вьЕход которого coenHHOirt: информационным входом третьего регистра результата, выход которого соединен с информационным входом четвертого регистра результата, выход восьл ого триггера формирования окончательного резупьтата соеданен с управляющим входом четвер)того сумматора, выходпервого регистра переноса результата соединен с информационным входсм второго регистра переноса резупьтата, выход которого соединен с информационным входом третьего регистра переноса резупьтата, выход 7 95 которого соединен с информационным входом, четвертого регистра переноса резупь- тата, выходы четвертого и пятого регист ров резуггьтата, выход четвертого регистра переноса резупьтата соединен соответственно с информационными ВХОДЕЦИИ четвертого сумматора, выход реверсивного счетчика соединен с информационным входом пятого регистра результата, вььХХ5ДЫ пяти старших разрядов третьего сумматора соединены соответственно с .информационными входами шифратора, выходдз шифратора -i --го вычисли те геьного бпока соединены соответствеьшо с информационными входами первого регистра Промеясуточного результата (i+1)-го вь чиспительногю бпока, выходы четвертого сумматора i -го вычиспктепьного блока соедине вы соответственно с информационнь ми пкодамк тюрвого регистра резуль тата и первого регистра переноса резупьтата (i+l)-го вышслитегтьного бпока, единичный выход седьмого триггера формирования окош-гатепъного резупьтата i -го вычислительного блока соединен с информационным входом первого триггера формирования oKOHHarcRLHcro тата ( 1 +1 )-го в1з1числит«ггЕ ного единичный выход восьмого триггера формирования окончательного резу:гьтага i-ro вычгюлительного бпока соеШнен с информационным входом второго тригге™ ра ()юрмировання окончатепьного резупьта та (i+1)-го вычист тельного блока, единичный выход второго триггера дегтитегш i -го вычислительного блока соединен с информационным входом первого триггера Депителя (i+l)-го вычиспетипьеного бпо- ка, информационные входы второго регист ра множителя, первого регистра веса оче редной цифры множимого, первого рчэгкст ра частичного произведения, первого регистра переноса, первого регистра проме жуточного резупьтата, первого регистра результата, первого регистра переноса результата, первого триггера делителя, первого и второго триггеров формирования окончательного резупьтата первого вычислитепьного блока подключены соответственно к информационным входам устройстЕЛ, управляющие входы третьего четверуого, седьмого и восьмого регистров множителя, первого второго и пя того регистров гюправки, второго и четвертого регистров веса очередной цифры множимого, второго и четвертого регистров множ1мо1 о, второго чвтвертого ре rwcTpot МПС ) произведения, второго и чети ттг.г-o :х игтрп , ВТОРОГО р/егистра промежуточного резута тата, третьего, четвертого, седьмого и восьмого триггеров формирования окончательного резупьтата, второго, четвертого и пятого регистров результата, второго и четвертого регистров переноса резут татов, второго триггера делителя объединены и подi nroseitt к первой тактовой шине устройства, управляющие вхоДЬ второго, пято- го и шестого р ггистров множителя, первого и третьего регистров веса очерюд-ной цифры множимого, третьего регистра мно шмого, первого и третьего регистров частичного произведения, первого и третьего регистров переноса, первого триггера дегштеля, первого и третьего регистров промежуточного резупьтата, первого, второго, пятого и шестого триггеров -форм-ирО 5а гая о; ;ончатепьного результата, первого и третьего регистров резу гиггата, первого к третьего регистров переноса результага объединены f подключены к второй тактовой итине устройства, В вычислительном устройстве узеп формирования поправок содержит л элементов И, причем первые входы эпсментов И являются соответ-стнеино перкым входом узла формироваь:ия попразп, вторые входь; эяемектов И явпялстсн соответ-ственно вторым входом узла оЬорлЯтрова гая поправок., третьи В7 ;;с;ь. эпементов И объединены и являются -- ретьим входом узла формирования поправок.; вылс-рд- элементов И являютсй вы.ходами |Ьсрглир)ова шя поправок,, На фит, 1а, б представлена функиг-чональная схема устройства; на фиг, 2 функциональная схема узла формирования поправок, В вычислительном устройстве каждый вычислительный блок содержит регистры ii, 2i множителя, регистр 3i веса очередной цифры множимого, регистр 4i мноидамого, регистр 51 частичных произведеНИИ, регистр 6i переносов, триггер 7i .целителя, регистр 8i промежуточного результата, триггер 9i формирования окончательного результата, триггер lO-i формирования окончательного результата, регистр 11-i результата, регистр 12i переноса результата, узел 13i формирова1ИЯ поправок, блок 14i коммутации, сум- матор-вычитатель 15i , регистры 16i, 17i множителя, регистры 18i, 19i по правок, регистр 201 веса очередной цифры множимого, регистр 21-i множимого, регистр 221 частичных произведений, регистр 231 переносов, регистр 24 i промежуточного результата, триггеры 25i. 99 26i формирования окончатепьного резуп тата, регистр 27 i результата, регистр 28i переноса резупътата, сумматор 29сумматор-Бычитатегаь 30i ,сумматор 311 по моду гас два регистры 32 i , 33 i MHO жителя, регистры 34л, 35i поправок, ре гистр 36i веса очередной цифры множимого, регистр 37i множимого, регистр 38i частичных произведений, регистр 39i переносов, регистр 40i npoмe c точного резуг1Ь7-ата, триггерьГ411 ,421 формирования окончатепьного результата, регистр результата, регистр 44 i переноса результата, сумматор 45i,peверсивгаый счетчик 46 i , регистры 47 i, 481 множитепя, регистр 49i поправок, регистр 50i веса очередной цифры множимого, регистр 5 1 i множимого регистр 52.1 частичнь1Х произведений, регистр 53-1 переносов, триггер 54 i депителя, регистр 55i промежуточного резупьтата, триггеры 56 т , 57 формирования окончательного результата, регистр 58i результата регистр 59 i переноса резупъ тата, сумматор 60 i , шифратор 61 i сумматор 62;, тактовые шины 63i , 6-1i,65i 6(Ji, информационные входы 67i -82 , Узел 13 формирования поправок ссидержит элементы 82, 83, 84, ,.., п И входы 85-87 являются входами узпов. В вычислительном устройстве информационные входы регистра 1 множителя первого вычислитеггьнго бпока подключены к информациот Ь Т 1 входам 68 зстрой стш, управляющий вход объединен с уп- равпяюшим входом регистра 4 MHOJKHMOго и подключен к тактовой шине 66-j, ин формацио1гаые входы регистра 4 множимого подключен к информационным входа л 71-, устройства, в каждом вычис1тте 1ьном бпоке выходь регистров li и 2i соедннень соответственно с; первыми н вторыми входами уапа 13i формирования поправок третий вход которого соединен с выходом младшего разр5Ш.а регистра 41 и пер- вым входом блока 14i коммутации, ЕЫХО ды узпа 13-i соединены соответственно с инфopмaциoнны.и входами регистров 18i и 19т, выходы которых соединены соответственно с информационными входами сумматора 29i, выходы переноса и суммы которого соединены соответственно с информационными входами регистров 34 i и 351, выхиды регистра 34i соединены соответстпрнно с информационными входами рг:гигтра 49i , выходы регистра 4i сое/тижны соответственно с входами первой i бпока 14 i ком jvryrauHH, входы ivr:ipf :i группы которого Зj О соединенъ гоотт тстЕ }Нно с выходами р ггистра 3 к информацио}шыми входами регистра 2Oi, выходы бпока 14i коммутации соединены соответственно с информационными входами регистра 21i , выходы которого соединенъ соответственно с информацион15ыми руоиами регистра 37i , выходы которого сое.чиионы соответственно с информационныкги входами регистра 511 , выходы которого соединены соответственно с информационными входами регистра 4i+l (i+1 )-го пи тельного бпока, выходы регистра 2О соединены соответственно с информационными входами регистра 36i, выходы которого соединены соответственно с информааконными входами регистра 50i, выходы которого соединены соответственно с кнформационны {и входами регистра З (i +1 )-го вычислительного блока, входы аЧпадзлих разрядов регистров i6i и 17i соединены соответственно с выходами старшего и младшего разрядов регистра (i-bl)-ro вычиспятельного блока, входь старших разрядов 16 i и 17 соединены .соответственно с выходами регистров li к 2i. выходы регистров 16i н 17i сосдкнетть; соответственно с информационными входами регистров 321И 33ij выхоль которых соединены соответственно с информацко1шьт.ш входами регистров 47i н 48i , выходы которых соединены соответственно с кнформацио1тыми входами регистров li+1 и 2i+l (i+l)-ro вышсготтегоьног-о бпока, выходы регистра 5i соединены соответственно с информаШ1онны ч«. входамЕЕ первой группы сумматора-вычи та те гая 15i, информационные входы второй группы в которого .лнены соответственно с выходакп5 регистра 0{, выход суммы сумма тор-вычи тате ля 15i соединен с информационным входом рс-гистуш 22i , выходы которого соединены соответственно с информационными входам первой гр}ппы с мматора-вычитатеая 3Oi , информационные входы второй группы которого соединены соответственно с выходаь-ш регистра 21 i , а ииформационные -входы третьей группы соответственно с выходами х гистра 6 i , инфор7лаш онный вход которого соединен с выходом переноса сумматора-вычитате-пя 15л, выход мгиядшего разряде см гистра 17i соедиЕ-ieH с первым упрявпяюшим ходом сумматора-ы читаг пя З.Я , второй упровпяющий вход KOTOpoi-o соединон с вьгходом млаДиего разряда регистра lf)i, выход суммы суг,матор«-П,1чигагв- я ЗОН , соединен с ниформлшонным входом регистра 38i , выходы кото- рого соединены соотызтственно с инфор)- мационными входами первой группы сумматора 45-i, информационные входы второй группы которого соедине 1Ы соответственно с выходами регистра 35 i , а вх ды третьей группы - соответственно с выходами регистра 39i, информационный вход которого соединен с выходом переноса сумматора-вычитатепя 30i , выход переноса сумматора 45 i соединен с информационным входом регистра 53i, а выход суммы - с информац1 онным входом регистра 52i , выходы которого соединены соответственно с информационными входами первой группы сумматора 6Oi, информацио1тые вхощ второй группы которого соединены соответственно с вы ходами регистра 49-1, а информационмыс входы третьей группы соответственно с выходами регистра 53i, выход суммы сумматора 45 i i -го вычиспитепьного бп ка соединен соответственно с информационным входом регистра 5л +1 (i+l)-ro вычислитегтьного блока, а выход переноса - с информационным входом регистра 6 + 1 {i+l)-ro вычиспк гелз.-ного ппокгЭ, единичный выход триггера 7i соединен с информационным входом сумматора вы чиспитепя 15-i и с информационным входом триггера 54i, едшшчные выходы триггеров 9i и 10 i соединены соответственно с информационными входами три геров 25-i и 261, единичные выходы которых соединены соответственно с инфор мационными входами триггеров 41i и 42i, единичные выходы которого соединены соответственно с информационными Бходак-ш триггеров 56 i и 57 i ,единичный выход триггера 25 i соединен с j г;-равняющим входом сумматора 31-i по два, выхолы регистра 8i соединены соответственно с информационными входами регистра 2И, выходы которого соединены соответственно с информацион ными входами сумматора 311 но модупю два, выходы которого соединены соот ветственно с информационными входами регистра 4O-i , выходы которого соединены соответственно с информационными входами реверсивного счетчика 4в, уп равняющий тжод которого соединен с еди 1шчным выходом триггера 41-, выход регистра lli соединен с информап ионным входом регист 1а 27% выход которого сое динен с информаиио,1л,1М входом регистра 43i , вьа.од которого сюединен с ипформа ЦИОНН1-.1М входом регистря 58-i , .ы.хоД триггер); r)7i сгмлипич с управпяютиик; 9 3 2 входом сумматора 62i, выход регистра 12i соед|.инен с м 1формационнм входом регистра 28 i, выход которого соединен с информационным входом регистра 4 4 i , выход которого соединен с информационным входом регистра 59i, выходь регистров 58 и 55-1, выход регистра 59i соединены соответственно с информационными-входами сумматора 62i, выход реверсивного счетчика 4 6-i соединен с информационным входом регистра 55i , выходы пяти старших разрядов сумматора 60 i соединены соответст-вонно с информационными входами шифратора G 1-i , выходы шифратора 61i i-го вь -чист;тегЕлгого бпока соединены соответственно с ин(:гормационными входами регистра Bi -1 ( -1 )-го вычислительного бпокк в лходы сумматора 62 i 1 го вычиспитеггы-гого Спока соединены соответственно с инфорь ационными входами регистр;- 11 t+l и регистра 12i+l (i+l)-ro вьлчиспитешзиогс бдока, единичный выход триггера 56-; 1-го вы шсш1тег1ьного бцока соединен с информационным входом триггера 9i+J- (-i-s-l-l-ro вычиспитепьного блока, единич Гь1й выход триггера 57i -i -го вычислитепьного блока соединен с и}пформэцион;дь:м ;;.;-одг-м триггера 10-i+l (5+1)-го вычасгти -епьно го бпока, единичный вьхол. TjiHi i-epa 54 i i -го вычислитеш;.;1ого 5;;ока соединен с информационным входоь Tpiirropa (i+l)ro вычиспитепььсго бпоко, HfiibopMaционные входы регистров 2i , 3--i, 5, 8-)-,111, 12i I триггеров 7i , 9i, IQ, первого вычиспитешэного бпока подкпюче-нь соответственно к информационным входам 69i, 70-1, 72i, 73i, 75i,79i, 80i 74л, 77i , 78i, устройства, управгшюшие входы регистров 16i, 17i , 47i , 48i, I8i, 19i 49i, 201, 50i, 2ii, 51i ,22-, 52i, 23л, 53-1, 241, 55i, триггеров 25% 26-1, 54-t, 56-i, 57-i, регистров 27i , 58i,28i, 59i соединены и подкшочены к тактовой шине 65i, управпяющие входы регистров 2, 32-, 33-i, 3i, 361 , 37i, 51, 38i, 6i, 39i, 8i,40i, Hi, 43i, 12i, 44i, триггеров 7 , 9i, lOi, 41i , 42i объединены и подключены к второй тактовой шине устройства. В узпе 13i первые входы элементов 83, 84, 85, ,„, п И являются соответственно входом 86 узла, вторые входы элементов 83, 84, 85 ,..,п И являются соответственно входом 87 узпа, третьи входы элементов 83, 84, 85, ..,, vt И объединены и являются входом 88 узла, а выходы являются выходами, узла , 1. Вычнслитопьноо устройство производит вычиспение апгебрааческих выражс- п mi НИИ вида У П m Очевидно, что выражение П с(; тюпу:.П ffiij-,, J чартся ив ) П с оспи подстави1ъ п i--1J.1 и m m.kpoMe того, подставляя т;-., устройство будет вычислять cyNfMy п чи COIU Меняя значение п и m, к вычиспению оператора F сводятся разные чиспе iibie процессы: скапярноо произведение двух векторов, вычиспення опредепитегш матрицы пюбого порядка и т. д. Высокая скорость вьтчиспения и обпег ченный обмен информации с памятьк достигаются путем применения неавтоном ного принципа вычиспення. Данный принцип вычиспения отпичается от кпассического тем, что операции умножения и суммирования характеризуются рядом спе цифических особенностей, основггыми из которых явпяются поспедоватепьное поступпение цифр множимого старшими раз рядами вперед, поспедоватепьное попучение цифр резу пь та та умножения двух опе (очередного множителя), начиная со старшего разряда с задержкой на оди такт поспе постлппения разряда множимого, выполнение всех суммирований и вычитаний, еобходимых в ходе вычиспения, без сквознь х nepeFiocoB с помош.ью запоминарсия переносов в специапьных ре гистрах, а также преобразование очередных сумм частичных произведений (представпенных в двоично-поаиционной системе счисления) в цифры резупьтата (в квазиканонической системе счисления) ПРОИСХ.ОПИТ на ocFroBo дополнительной опер ции аеления ч-асгичного результата на два. При вычислении алгебраических вырап гп жеиий вида - J ij при m 7 1 J-1 регистры 1, 2, ;16, 17, 31, 32, 45 и 46 служат Для хранения промежуточных значений множителя, представленного в избиточной в квазиканической системе счисления с цифрами из множества {О , 1, Ij. Для кодирования шобого элемента из этого множества используется двухбитное представление; первый бит записывается в j -ом разряде регистров 1, 16, 32 и 47, а второй бит в j -ом разряде - соответственно регистров 2, .17, 33 и 48, Соотношение кодировок заиесетшт в табп. 1 . а б л и ц а .1 Как следует из неавтономного принципа выпопнения операции умножения, определение суммы частичных произведений (или, что то же самое, частичных остаткок от деления на два) происходит с ошибками. /.1ля компенсации ошибок в каждом i--ом блоке служат узеп 13 и сумматор . Узеп 13 предназначен для формирования положительной и отрицательной поправок Р и N на основе младшего разряда регистра 4 и всех значащих разрядов регистров 1 и 2 в соответств н с логическими выражениями (n)-:/(o-j) Nrx(nl-y(o-jj- V (O-jj, x(n) - младший разряд регистра 4; а у - содержимые регистров 1 и 2. Работа узла 13 проиллюстрирована нь фиг. 2, где (d), N(1),..., |(п),(1), У ( (....(п)- разряды регистров множителя 1 и 2, закодированные в соответствии с табп 1; Р(с(),,..,Р( разряды положительной компенсации; М(а ),..., N (l- разряды отрицагельтюй компенсации. Сумматор-вычитатель 15 предетапя«. ет собой (п+4 )-раарядный комбинационный сумматор-вычи та те ль с паралпельным переносом, причем все разряды схемы, кроме ()-го, является двухвходовыми, а (п+2)-й разряд - трехвходовым, По первым входам на сумматор-вычита- те ль 15 всегда происходит передача содержимого регистра 5, по вторым входам - содержимое регистра 6, причем операция, выполняемая сумматором-вычитателем 15 над содержимым регистров 5, 6 и триггера 7, зависит от ее управляющих входов, связанных с выходами двухбитного регистра 8. Прибавпение кпи вычитание единицы к п - 2-oN разряду сумматора-вычитатепя 1 5 осуществляется с цепью выпопнения деления на два частичного резупьтата, полученного в резупьтате спожения ипи вычитания содержимых регистров 5 и 6. Деление суммы 1;-,О чпстичи1,Х riponaiiofUiUnii на др.а нообходимо для перевода ого из двоичной позиционной систем1 1 счислония в иабьггочную квпзиканоническук) систему счисления с цифрами О, 1 , 1 и дпн уменьдиения погрешности . -спи в днухбитном рег-истре 8 находилась i , то произойдет суммирование содержимого регистров 5 и G, еош 1 то произойдет суммированиг- со держимого рс-тистроп 5, 6 и вычитание из этой суммы соДержимо1 о триггера 7. же О, то произойдет суммирование содержимого periiCTpoB 5 и 6. Сумматор-вычитатепь 30 представляет собой (п+4)-х разрядный комбинационный сумматор)-вычитат(;пь, все входы которого трехразрядные, Глспи в управляющие входы сумматора-вычитатегтя 30 из мла/Диих разрядов регистров 16 и 17 поступает 1, то осуществляется суммиро- ванне содержимого регистров 21-23, еепи 1 , то от сук-гмы содержимого регистров 22 и 23 вычитается содержимое регистра 21, есгти О, то происходит суммирование содержимого регистров 22 и 23 Дпя трехразрядных входов сумматоров вычитатепей 15 и ЗО. ;:р/1 выпопно;: поразрядного суммирования, булевые вь( ражения имеют вид: 5: а be V oibc V аЪс аЪд. (о Р ctt) V ас V Ъс , где S - сумма; Р - перенос; в спучае выполнения вычитания S йЪс Ч d-bc V аЪс v о1Ъс, Р: d-b V ас V Ъс . Базовь е уравнения (З) составпень: ка основании уривнений (2) заменой с нас Объединяя выражегие дгш поразрядно-го суммировани-Я (2) и Г1оразряД юго вычитания (3), с учетом зправпяюших сигналов V и Vr I значение S Р определ яют следующим образом S::: obcV V dbcV V abcV аЪсУ. V 1111 V аЪс M V dbcV V аЪсЛ v dbc V at) V acV v ticV, V a-bV v acV uv V bc I1л Управляющие V и Vr соДержи ся в регистре Н и в viпадших разрядах регистров 1П li 7„ (согласно с табп. 1 , S.7 V 3 .0 где - соотв -iTTByoT вьтолненито по pa.Tpii/nioio с:г1ом еиия, , а b + с) , т - т;г.р, .,--лглогч. В 11чятания (OHi)V), -- (-)Vv)ni-;o двух рв..эрядпг-й 31 О ля сумматора-вычитатепя 15 пыпопне- и(5 оо1 азрядного сложения осуществгйет- я под вoздeйcтвI;e l Vt7 cg а поразрядное В ,питание - под тгозДействием q;, с ля сумматора-вычитатепя .U3 под воздействием V., происходит поразгялиое сложение, а под воз/хейстпием Vi-| - поразрядное вьтчитание. В суммато1-Ю вычит(:тепе . ч-их -еются двухразрядные входь;, булевые вы)а.жения, описывающие их, определяг,,тся как 5-0/0 / аЪ Р-аъ. Ввиду того, что Г1азря/ия MHO iaiMoro поступают, начиная со стерг.п.1х рр зрядов, послюдопатепьно в кпждьй бпок, : ::ОбхоДи МО их упогмдочить. С neritiK: соопи:;Дения однородности по блоках ncrio ihsyf T- ся блок 1-4 коммутации, Так1;м образом, он служи 1 дт;; колПчП/тацпи iiiujBi. поступивщего разряда множимого 6, в соответствующий ему вес. Регистр - с тужит для хранения уже поступивших рслзрядов. Содержимое регистра 3 имеет вид ООО „. 1 .,. OOOj при пепедачп ип i -го блока на (i + 1 )-и ог.ичигч рр; 3 сдвигается пй 1. разряд -лрлго S ; - значоиие j -го разрыло .ож-мого, тогда есии е ; -1. то ;:ioo-..c-:so-;r CVMMHjрование содержиь-ЯзГХ poj-::;:-/poE 3 w 4, еспи е -0, то производк):.:; Г1|№суач передача значения из регистра 4 i; р о-истр 21,, В первом блоке единица регнстре 3 находится в старшем разряхе, ес-яи , то в регистре 21 запяни-гся число ООО0.1 00000.,., так как в регистре 4 будет 0.000.... Кроме этого, едишша регистра 3 всегда суммирует с нулем j -го разряда регистра 4, Таким образом, бупевые выражения, оппсь-вающие состояния блока 14 коммутации следующие: R9.1 ( i j4-i-n) R4(0 j-f;j- -n) I о fi xi ( n л / ; 1 D 3 / i 1 n ,( с ; lRaiU)e(j} RMj)R4{j), где R3 , R4 , Rll - соответственно состояния регистров 3, 4 и 21, а (О- j- ; j+i-h) все разряды от О, п кроме j -го. Сумматор 31 по модулю два спужит для передачи содержимого регистра 24 в регистр 40, если в ее управляющий вход цоступает Ц-1 из единичного выхода триггера 25, Если q и Ъ - выходы двухразрядного регистра 24 и с и d выходы реiiMicrpa 4О, то Г1оги 1есксе выражение,

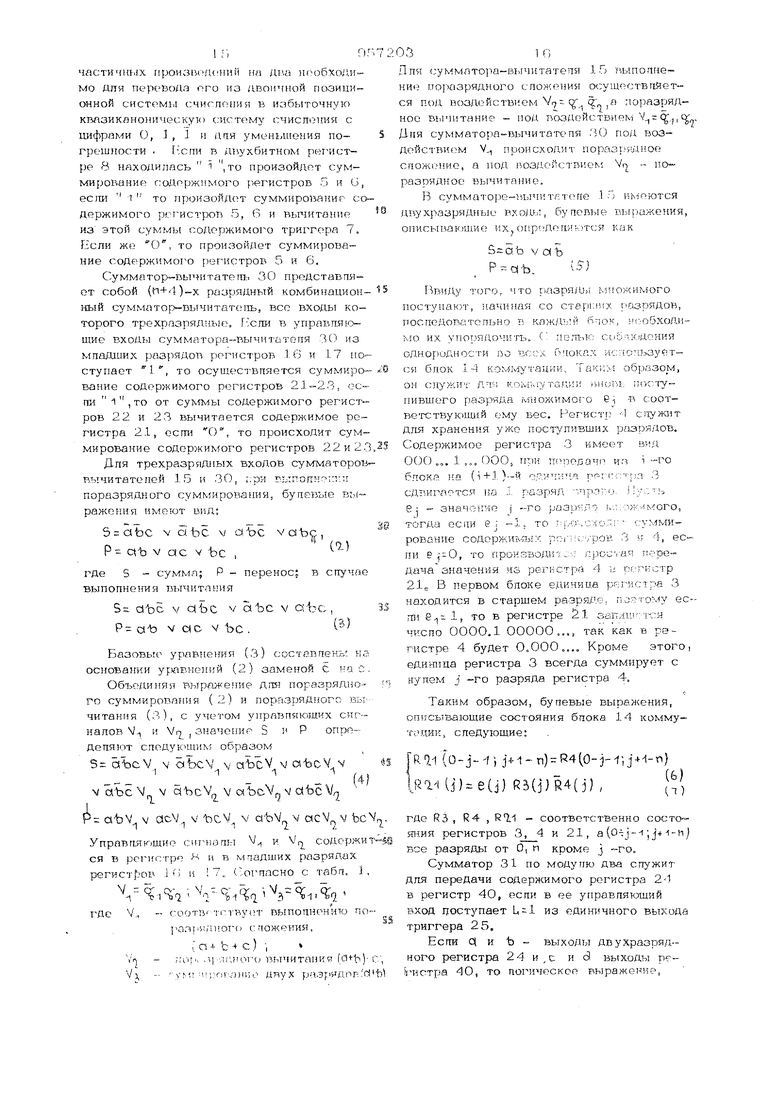

17or/

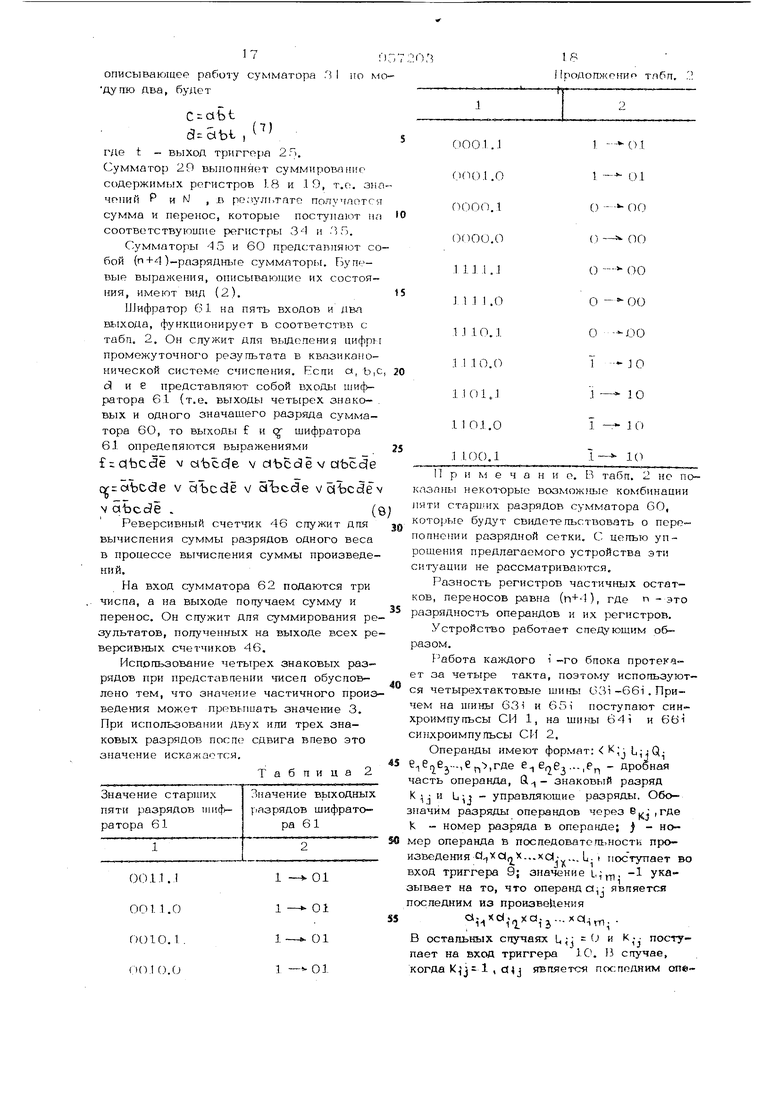

описывающее работу сумматора Л I по модупю два, будет C-abt dr&bt , где t - выход триггера 2 Я. Сумматор 29 выпопняет суммирование содержимых регистров 1-8 и .1 9, т.е. afi чепий Р и М , в ре;1ул1,тате получается сумма и перенос, которые nocTyiiaioT на соответствующие регистры З и Г). Сумматоры 45 и 60 представляют со бой {п+4 )-разрядш51е сумматоры. FSyneвые выражения, описывающие их состояния, имеют вид (2). и ифратор 61 на пять входов и два выхода, функционирует в соответствв с табп. 2. Он служит для выделет1я цифри промежуточного результата в квазиканонической системе счисления. Еспи а, Ь,с d и е представляют собой входы 1иифратора 61 (т.е. выходы четырех знаковых и одного значащего разряда сумматора 6О, то выходы f и ( щифратора 61 опреДепяются вь ражениями f:0bcde v аЪссЗе v dbcde v abode c rctbcde V dbcde v oibcde vabcdev V abcde .( Реверсивный счетчик 46 служит для вычиспения суммы разрядов одного веса в процессе вычисления суммы произведений. На вход сумматора 62 подаются три чиспа, а на выходе поггучаем сумму и перенос. Он спужит дпя суммирования ре зультатов, полученных на выходе всех ре версивных счетчиков 46. Использование четырех знаковых разрядов при представпении чисел обусловлено тем, что значение частичного произ ведения может превыщать значение 3. При использовании двух или трех знаковых разрядов посл( сдвига впево это значение искажается. Таблица 2

18 I родопженип тлбп. ,.. 0001.1 Примечание. В табп. 2 не показаны неко1-орые возмож Ш1е коь бинации пяти стари.их разрядов сумматора 60, KOTOjjbie будут свидетельствовать о перепопнепии разрядной сетки. С цепью упрощения предлагаемого устройства эти ситуации не рассматриваются, Г азность регистров частичных остатков, переносов равна (п+П, где п -это разрядность операндов и их регистров. Устройство работает спедуюшим образом. Кабота каждого i -го бпока протекает за четыре такта, поэтому испопьзуют- ся четырехтактовые щины G3i -66i . Причем на тины 63i и 651 поступают синхроимпульсы СИ 1, на шины 641 и 66i синхроимпульсы СП 2. Операнды имеют формат: K;J ...,е.-,где ...,е - дробная часть операнда, S-(- знаковый разряд и L - управляющие разряды. Обозначим разряды операндов через |ГДв К - номер разряда в операнде; j - номер операнда в последоватоль,ностк произведения (Х...хс1- ... L-i поступает во вход триггера 9; значение 1,. -1 укаывает на то, что операнд dij явгтяется последним из произведения i-l il °i3- - vn в остальных случаях U,; - поступает на вход триггера 10. В сггучае, когда , явпяется псх;педним опе 1 )О рандом суммы ироизв(доняя, тл, i n и ,Torua q,, :: цойствисм с ихрониз 1ции СИ 1 вход ная информация поступаетс;я на fxsrucTpi.i блока с номе{юм -1, на 1-i, .-i, Л (л, 11, 12., ноступает код О,- в страший и знаковый разряды регистра 5-i поступают знаковый разргщ Q, и старший разряд С -1 перво ло операнда d л из поспедоватепьности .--с( ,осгги т.,-1 , то в tpHrrep 9 поступает L 1 иначе L, - С) и в триггер 10 поступает К -- О, еспи 1 7 1, а в CTapuieM разряде регистра 3 и в триггере 7 за1П сывае1СЯ единица. ТогДл выходы уз па 13 и б пока 14 коммутации нулевые, а на выходах сумматора ВЬРитатепи 1 5 повторяется состояние регистра o-j, ибо все упарвпяю- аше сигнагсы на этом такте нл певые. На втором такте работы устройства синхронизируюпще импупьсы СИ 2 определяют момент передачи информации на регистры 1( . Кроме регистров 20.j и 22. состояния остапьных регистров ну певые. Состояьгия регистров 20., и 22. повторяют состояния регистров 3 и 5. На третьем, а затем и на четвертом так те та же самая ситуация повторяется, и, таким образом, состояния регистров 3 и 5, будут повторяться соответственно в регистрах 3(:Ц, 50., и 38., 528,, топько в регистре 52., значение содержимого регистра 5, будет сдвинуто на 1 разряд влево. На выходе схемы бО. повторяется состояние регистра 52,|, Со- стояния регистров 17, 48,, 49, 51., 53-,. 54,,, 55., 5G, 57., 58, 59 нулевые, С выхода шифратора 61 поступают пять старших разряд.ов и, таким образом, на основании кодировок, представпенных в табл. 2, определяется первая цифра множителя 6. , которая является старшей цифрой преобразованного члю- ла а,,., в квазикаЕюнической системе счис ления, а значит через 3 такта СИ 1 KJOM но принимать старигую цифру е-|г операн. да q и его знаковьн разряд на первый уровень первого бпока, а первый уровен второго бпока готов к приек-гу второй циф ры eQ onepatma а.,.. В дапьнейшем рассматриваются вычис nuTenbHj ie процессы в первом и во вто- ром блоке, в результате которых будут получены сооГветственно первый разрш е произведения а.,«а.,и второй разряд , чиста ц квазиканонической системе СЧИСГКЯИЯ. П отпг.чпг ;п R.,.., цифра . остлгп, разряды опе :1андрв и (j и 3.2(j нгзковыгг разряды d, , постзпает на два лади-их разряда югистра , а не в ,к.- истр 5. На этом такте бпок 1 -Ц номмутации В1)1попня1от соответствующие преобразования дпя передачи цис|)ры е., в старн ий и знаковый разряды 1к гистра 2 Ц, при этом в старшек и 3 -:aKOBON- разрядах регистра 3., за1Г 1саны единицы.. (Отстояния всех остагпэных регистров мупрвые. Сигнап СИ 2 опредепяет момент приема информации в регистры второго уровня. Из двухбитного регистра 8п спедуюшего вычисаитепьного бпока поступает цифра множитепя е,которая записывается в мпадших разрядах рег-истров .j. Состояния рс гистров 18.28, такие же как у соответствующих 1зегисгров первого уровня. Третий Л четвортт й такт.-: работы первого вычиспитепьнего бпока позвоШт от передавагъ выхо.днукj iiп роJXM.. сумматора-вычитатепя ЗГ) isa регистры 38 и 39,,, затем с них, со сдвигом на один разряд впево, - в регистры 52 .-i и 53 , После суммирования со.г.юржит ого регистров 52.., и 53,, в сумматог -;.. )(., и анализа пяти старших разрядов частичного произведения в шифраторе uJ ,; on рсгдсляется первая цифра {.озугпугато от умножения q,,,, на сц которую обозначаем через e,jr . Одновременно во р/гороь вычислзггеш:зном блоке (i.2) пропсходяч- спе-д юшие преобразования Под воздействием синхроимпульсов СИ .1, е,,,, (старшая цифра преобразованного операнда а . записывается в двухбитный регистр 8г), в старший разряд регистра поступает вторая цифр;а п операнда Д,|Г2.Состояния регистров первого уровня следую ш.ие. В регистры , 2г;, бг,, 7г, 9г|. .10, 11 .-j, 12 Г; г;оступа-. ют нули из регистров 47-;, 48,,, 51., 54, 56,,, 57..| , 58,.,, 59,., первого вычислительного бпока в регистр 3 г передается дробная часть (т„е. значащая единица) из регистра 50у со с.двигом ифаво на один разряд. При таком расредепении данных на первом уровне втоюго вь числитег1ьного блока повторяется .-а же самая вычист те)тьная процедура, гго и описана выше для первого блока при вычиспении е .., отпичие только в TONS, что содержимое регистра 8rj, т.е. .( , мо- я«;т равно О, 1 и;ш i (т.е. OJ. (.), 10), тогда в регистр 23rj записываются переносы, а в регистр частичный остаток от депения на 2. Выходы узпа блока 14 rj - нзлевые. В дальнейгием под воздействием синхроимлуль-219сов на регистры второго и третьего уров ней происходит дальнейшее суммирование содержимых регистров 22/ и 23ri соответственно в сумматоре-вьтчитатепе 30t и сумматоре 45г. С выходов сумматора 45г информация записывается в регистры 52 и SSrj, а затем, поспе оче редного суммирования в , сумматоре 60 содержимого регистра 52г2 и SSfj,произво дится анапиз пяти старших разрядов частинного произведения с помощью шифратора 61г2, на выходе которого определяется вторая цифра множитегш е которая является второй старшей цифрой операнда с(.,,представленного в квазиканонической системе счиспения. Таким образом, на четвертых уровнях первого и второго вычислительных блоков одновременно определены значения соответственно и о Рассмотрим как протекает дапъше вычисли те пьный процесс в первом, втором и третьем вычислительных бло1шх устройства В первом вычислительном блоке вычис лительная процедура протекает таким же образом, как и описана выше для вычисления ,при этом определяется л) т.е старшего разряда от умножения Если (т.е. операнд а является т, последним числом произведения П &) , то одновременно с поступлением в .регист 4 разрядов е-13 и 0.- (старший и знаковый разряды операнда ) в триггер 9 подается разряд , который передается потактно с первого вычислительного блока до второго уровня второго вы- гас ли тельного блока, где он будет управпять передачей е в реверсивный счетчик 46г и, таким образом, получим первую цифру результата умноженияц хд чс} уже в двоичной системе с исления. Под воздействием СИ 1 в двухбитный регистр Q-f, записывается el , ,а в регистр 8(- . На этом же такте в регистры Irj к 2 записываются содержимые регистров 47 и 48, в регистр 3fj, передается значение регистра 50, сдвинутое на оди)1 разряд вправо. В (п-1) старшие разряды регистра 4г поступает содержимое регистра 51-1, в его младший разряд записывается вторая старшая циф- ра ) операнда а ,,значение cyMiv-ibi и переноса частичных ггроизведений передаются из сумматора 60 в регистры 5г2. и 6,. Из триггера 51 в триггер 7rj записывается 1. с,,о:;тояния триггера 1О,2 и регистров II Q и i2r нулевые. На первом уровне узеп i.i.T формирует поло- 3 житеггьную и отркцательгтую кокшеисаш1к ошибки в соответствии с вырал ением (1). Узел 14 формирует множимое на основе содержимого регистров З, и 4-2-. На следующем такте сукгматор 202 формирует резкость содержимых регистров ,. В младшие разряды регистров 17г| поступает цифра Pfj и тогда сумматор-вычитатель ЗОг в соответствии с выражением (4 формирует очередные суммы частичных произведений и перенос суммы част1гчных произведений. Ввиду нулевого состояния триггера 25( на данном такте, ы 1ходы сумматора 31 по модулю два также нулевые. На третьем такте сумматор 45 ч формирует очередную сумму частичных произведений и их переносы с учетом KON neHcaции. Результаты передаются в регистры 52, со сдвигом Влево на один разряд, содержимое регистра 34. передается в регистр 49о также со сдвигом влево на один разряд. На четвертом такте сумматор 6Осформирует сумму частичных произведений и ее перенос.; г учетом поправки, Поспе анап:иза пяти старших разрядов определяется вторая старшая цифра бппот умножения старших разрядов операндов d,, и а.Описанный вычислительный процесс повторяется на всех последуюших вычисгштельных блоках При поступлении в первый вычислитель пый блок устройства старшего разряда операнда а г, на единичкьп вход триггера 10-1 подается К 1, и тогда поспе четырех тактов во втором вышслитепь- ном блоке содержимое реверсивного счетчика 46г2 передается в сумматор 62, выходы которого через регистры 1 Ij, 123, 27, 283, 433, 443, 583 и 59з подключены к входам сумматора 60j. Таким образом, сумматоры 62 служат Для сложения содержик-патх всех реверсивных счетчиков 46i по мере формирования суммы разрядов одного веса. Для большей ясности отмечаем, что в реверсивном счетчике 46 первого вычисш тельного блока формируется алгебраическая сумма всех старших- разрядов группы произведения, например, если имеется сумма liq.«7iVai,14,., Т, о после постуления : L - , а атем Ь jj в триггер О, он разрешает ыдачу в реверсивный счетчик 46 одноазрядные результаты вычисления соотетственно

.

V l 31«33«34 3:r

и фактически осуществляет суммирование старших разрядов А ,, Aj . Во втором и в последующих е вычисггетогсьных бпоках происходит то же самое для бопее мпадших разрядов.

При подаче в первый вычислитегн.-ный блок старшего раэрярл операнда «35 дается в триггер 9-,, а в триггер , указывающий на то, что необходимо суммировать содержр мое реверсивных с ютчиков, тогда .l передается из одного вычислитепьного бпокп в другой через трипперы 10, 23, 42 и 57. При этом резл пьтат пог чается в ЕМДе двух чисеп частичного резушитата к переноса в регистрах 11 и 12„ Яспи резул1 тат необходим в виде одного чкспа, то он может быть получен путем допонитепьного прохода через предпагаемое устройство. Старшие (Z +2)разряды ага-ебраического выpaжeниs вида

Ч т;

z:

1

-Л -

Шт. ()r

могут быть получены за

такта,

где г

константа, опреде 1яюш.ая необходимую точность окончательного резупьтата| Г;1|1,3.-- iE разрядность операндов;

П1- - количество сомножителей - количество вы шcпитeпьныx

блоков устройства. На следующем такте после выдачи k.,, rl можно принимать новую поср.едо-вательн.ость чисел, Спедоватепьно, основное преимущество конвейерного метода обработки информации, закпючаюшееся в эффективном использовании аппара- турь многорегистровых устройств, в данном случае сохраняется.

Таким образом, устройство вычисляет одно и то же алгебраическое выражение за гораздо меньшее количество тактов, чем устройство, выбранное в качестве прототипа, обладает значительно ботлпей по срав 1ению с ним производителькос-п ю и при этом оно может состоять из мсньщего кол11чества однотипных блоко1 „ vDo-ме того, Иэшопнение перемножения te дополнительном коде исключает и эобходимость в том, чтобы все опергишь выражения, подпгжащпго В1.числени1С:, бьпти обязат1 пьио 11опожителън1-1ми дробями,

что имеет место при вычиспс-и и этого выражения при помощи устройства, выбранного в качестве прототипа. Увепиче- ние скорости арифметического выражения достигается не только путем вычислеш{я его за Met-гьшее количество тактов, по сравнению с извсстныгу, но также и благодаря токту, что дпитепьность такта в предлагаемом устройстве является го- раадо меньшей, чем в прототипе, гго обеспечивается нахождение у частич -;ого рсзупьтата в устройстве но схеме без распространения перченоеов.

Фор м у Г а и 3 о б р е т е ;; к я

1, Вычис)1итегя1Ное устройстБО, сосгорлдее из п зыП1спитеШ: ных бпокоЕ, кажда й из которых содегжит порвтлй j jrHCTp множимого, первый р. множитепя, первый регистр частичных произведений, первый сумматор-вычитатепЬ; причем информационные входь; регистра множителя первого вычксяительного бпока по/хкпючеНЪ к соответствующим ИнфорМЭЦИО П1ЫМ

входам устройства, управггявдщий вход объединен с управляющим вхо/ШдМ регистр)а множимого и подкточен к тактовой шине устройства, информационные входы регистра 1 лнол-симого подключены к соотБстх:тЕукхцим информационным входам устройства о т л и ч а ю ш е о с я тем, что, с целью повьпиения быстродействия устройств в кандаый -5 --и вычисги-тепьгтьп бпок вве-Декы Второй, третий 4eTBepT)jii рг-г :стрь к-шожимого, второй, третий, четве-отый, .пятый, Шестой, седьмой и восьмой регист-ры множителя. втх)рой, третий и четвертый регистры частичных произведений, первый, второй, третий и четверть-й регистры переносов, первый, второй, третий, четвертый и пятьпЧ регистры поправок, первый, второй, третий, четвертый и пятый регистры реэупътата, первый, второй, трепгй и четверть й регистры переноса результата, первый,, второй, третий и четвертый рэгистрь; вес. очередной цифры множ.имого, первый, второй и тре-. тий регистры промежуточного ре.зупътата первый и второй триггеры Депитепл. первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой триггеры формирования окончательного результата, второй сумматор-вычитатепъ, первый, второй, третий и четвертый сумматоры, узе п формирот.5ания поправок, блок ком,мутации,игафра.-тор, сумматор по модулю два, ревеpCHBfaifi счетчик, причем в каждом вычисгштепьном блоке выходы первого и второго регистров множителя соединены соответст-259венно с первыми и BTOpbiNm входами уз ла формирования поправок, третий вход которого соединен с выходом мпадшего разряда первого регистра множимого и первым входом блока коммутации, выходы узла формирования поправок соединены соответственно с информационными входами первого и второго регистров поправок, выходы которых соединены соответственно с информационными входами первого сумматора, выходы переноса и суммы которого соединены соответственно с информационными входами третьего и четвертого регистров поправок, выходы третьего регистра поправок соединены со ответственно с информационными входами пятого регистра поправок, выходы первого множимого соединены соответстветю с входами первой группы блока коммутации, входы второй группы которого соединень соответственно с выходами перво го регистра веса очередной цифры множимого и информационными входами второго регистра веса очередной цифры мноншмого, выходы блока коммутации соедйнены соответственно с информационными входами второго регистра множимого, выходы которого соединены соответственно с .информационными входами третьего регистра множимого, выходы которого сое динены соответственно с -лиформационны ми входами четвертого регистра множимо го, выходы которого соединены соответственно с информационными входами первого регистра множимого (т+1)-го вычислительного блока, выходы второго регистра веса очередной цифры множимого соединены соответственно с информационнымиЪходами третьего региртра веса очередной цифры множимого, выходы которого соединены соответственно с информационными входами четвертого регистра веса очередной цифры множимого, выходы которого соединены соответственно с информационными входами первого регистра ве- са очередной цифры множимого (i +1 )-го вычислительного блока, входы младших разр5здов третьего и четвертого регистров множителя соединены соответственно с выходами старшего и младшего разрядов первого регистра переноса результата 0+1)го вычиспительного блока, входы старших разрядов третьего и четвертого регистров множителя соединены соответственно с выходами )1ервого и второго регистров множнтепя, выходы Третьего и четвертого регистров множителя соедиТ-юны соответственно с информационными входами пятого и пю.-того регистров мно0326жителя, выходы которых соединены соответственно с информационными входами седьмого и восьмого регистров множителя, выходы которых соединены соответственно с информационными входами первого и Второго регистров множите пя (i + 1 )-го вычислительного блока, выходы первого регистра частичного произведения соединены соответственно с информационными входами первой группы первого сумматора-вычитателя, информационные входы второй группы которого соединены соответственно с выходами первого регистра переноса, выход суммы первого сумматора-вычитателя соединен с информационным входом второго регистра частичного произведения, выходы которого соединены соответственно с информациoнliъ ми входалда первой группы второго сумматора-вычитатепя, информационные входы второй группы которЪго соединены и соответственно с выходами второго регистра множимого, а информационные вхо Д1.1 третьей группы-соответственно с выходами второго регистра переноса, инфо}: мационный вход которого соединен с выходом переноса первого сумматора-вычт тателя, выход младшего разряда четвертого ро- гистра множителя соединен с первым управпяюшим входом второго сумматора-вычитателя. Второй управляющий вход которого соединей с выходом младшего разряда третьего регистра множителя, выход суммы второго сумматора-вычитате- ля соединен с информационным входом третьего регистра частичного произведения, выходы которого соединены сеют- , петственно с информационными вкодами ,первой группы второго сумматора, ииформационные входы второй группы которого соединены соответственно с выходами четвертого регистра поправок, а входы третьей группы - соответственно с выходами третьего регистра переноса, информационный вход которого соединен с выходом переноса второго сумматора-вычитате ля. выход переноса второго суЬлматора соединен с информационным входом четвертого регистра переноса, а выход суммы - с информационньп входом четвертого регистр частичного произведения, выходы которого соединены соответственно с информационными входами первой группы третьего сумматора, информационные входы второй группы которого соединены соответственно с выходами пятого регистра поправок, а информационные входы третьей гр)уппы - соответственно с выходами четвертого регистра переноса, выход суммы третьего суммато1)а i го вычислигепьного бпока соединен с информационным входом первого регистра частичного произведения {)+. )--го вычис гтительмого бпока, а выход переноса - с информационным входом первого регистра переноса (i+l)-го вычисггатепь 1ого бпока едй1шчный выход первого триггера дети |1-егга соединен с информационным вкодом первого сумматора-вычитатепя и с ипфор мацио 1ным входом Второго триггера депи теля, единичные выходы первого и второго триггеров (|х)рмирования окончатегаь но резугпбтата соединены соответственно с информационными входами третьего и четвертого триггеров формирования окончатегтьного результата, единичные пь Коды которых соединещз соответстве(ню с информационными входами пятого и ше того триггеров формирования окончательного результата, единичные выходы которых соединены соответственно с инфор мационными входал-ш седьмого и восьмого триггеров с|юрмирования орсончатепьно- го результата, единичный выход третьего триггера формирования .окончатепьного результата соединен с управляющим входом сумматора но модулю два. выходы первого регистра промежуточного результата соединены соответственно с информат-шонными входами второго |зегистра промежуточного результата, выходы которого соединены соответственно с информационными входами сумматора по мо ду пю два, выходы которого соединены соответственно с информационными входшли третьего регистра промежуточного результата, выходы которого соединены соответственно с И1 формационными вхо дами реверсивного счетчика, управляющий вход которого соединен с единичным вы ходом пятого триггера формирования окон чательного результата, выход первого регистра результата соединен с информационным входом второго регистра резуль тата, выход которого соединен с информационным входом третьего регистра ре .зультата, выхоД которого соединен с информационным входом четвертого регистра результата, выход восьмого триггера формирования окончательного результата соединен с управляющим входом четвертого сумматора, выход первого регистра переноса результата соединен с,ин(юр мационным входом второго регистра переноса резупьтата, выход которого соединен с информационным входом третье™ го регистра переноса результата, выход которого сое/цпген с информационным г.хо дом четв }ртого регистра nepoFioca резупьтата, выходы етвертого и пятого регбистров результата, выход четвертого регист ра переноса результата соединоаы соот- ветственно с информационными входами четвертого сумматора, выход реперсив- ного с ютчика соединен с информационш 1м входом пятого регистра юзупьтата, выходы пяти старших разрядов третьего сумк)атора соединены COOTBOTCTKMIHO информационными входами шифратора, выходы шифратора i -го вы racпитofIЬHoгo бпока соединены соответственно с информационными входами первого регистра, промежуточного результата (i + -1)-ro вычислительного блока, выходы чегв фтого сумматора т-го вычислительного бпока соединены соответственно с инфор -,;апион- входами перврго регчгстрс резугштатаи первого регистра ncpeiioca рсззугП). тата (i+l)ro вычисгште1т,1,ного бпока, единичный выход седьмого триггера формирования окончательного резуптчтата 1 -го вычислительного бпока соодкнен с информациоп11ым входом первого триггера формирования окончатет, резупьтата (1+1)™го вычислитепьного блока, единичный выход восьмого триггера фор- кгарования окончательного результата вычислительного бпока сое/1ипон с информационным входом второго триггера формирования окончатепьього резут.-.тата (i+l)ro вычислительного блока, единичный выход второго триггера делителя -1-го вычислительн.ого бпока соединен с информационным входом первого триггера делителя (i+l)--ro вычис пи тельного блока, информационные вхо/ды второго рег истра множителя, первого регистра веса очередной цифры множимого, пе} вого регистра частичного произведения, первого регистра переноса, первого регистра промежуточного результата, первого регистра результата, первого регистра переноса резул1зтата, первого триггера Делителя, первого и второго тригге« ров формирования окончательного результата первого вычислительного блока подключены соответственно к информационным входам устройства, управляющие входы третьего, четвертого, седьмого и восьмого регистров множителя, первого, второго и пятого регистров поправки,вто рого и четвертого регистров веса очередной цифры множимого, второго и четвертого регистров множимого, второго и четвертого регистров частичного произведения, второго и четвертого регистра переноса, второго регистра промежуточно™ го результата, третьего; четвертого, седьмого и восьмого триггеров формирования окончательного результата, второго, четвертого н пятого регистров результата, второго и четвертого регистров переноса результатов, второго триггера делителя объединены и подключены к первой тактовой шине устройства, управляющие входы второго, пятого и шестого регистров множитепя, первого и третьего регистров веса очередной цифры множимого, третьего регистра множимого, первого и третьего регистров частичного произведения, первого и третьего регистров переноса, первого триггера делителя, первого и третьего регистров прюмежуточного результата, первого, второго, пятого и шестого триггеров формирования окон чатепьного результата, первого и третье:го регистров результата, первого и третьего регистров переноса результата объ 9 0330 единены и подключены к второй faXTOBo шине устройства. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узеп формирования поправок содержит п элементов И,причем первые входы элементов И 5гвляются соответственно первым входом узла формирования поправок, вторые входы элементов И являются соответственно вторым входом узла формирования поправок, третьи входы элементов И объединены и 5тл5потся третьим входом узла формирования поправок, выходы элементов И являются выходами узла формирования поправок. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ № 2О34341, кл. Q 06 F 7/38, опублик. 1976, 2.Авторское свидетельство СССГ № 656О59, кп. G 06 F 7/38, 1976 (прототип).

Й

.

fr

kт

о

g;

n

p

.

b

h-n

fr

-Ч

H--1

tn

®

Авторы

Даты

1982-09-07—Публикация

1980-11-17—Подача