ственно и с выходом первого элемента И через первый элемент задержки, первый вход первого элемента И подключен к первым входам первого элемента ИЛИ и второго элемента И и является шестым входом блока, а второй вход - к одному из выходов второго триггера, другой вход которого соединен с первыми входами третьего, четвертого и пятого э. ементов И, один из входов второго триггера является третьим входом блока, а другой вход подключен к выходу второго элемента ИЛИ, второй вход которого соединен с первыми входами третьего, четвертого и пятого и вторым входом первого элементов ИЛИ и является пятым входом блока, вторые вход.л третьего, четвертого и пятого элементс 1, И,}И являются седьмым входом блока, а третьего элемента ИЛИ подключен к одному из вхолчов третьего триггера, другой вход которого соединен с выходом шестого элемента ИЛИ, первый вход шестого элемента ИЛИ подключен к выходу пятого элемента И, а второй вход - к второму входу соответствуюш,его элемента И группы и выходу шестого элемента И, второй вход которого соединен с первым входом седьмого элемента ИЛИ и выходом второго элемента И, второй вход которого подключен к первому входу седьмого элемента И и к выходу четвертого триггера, один из входов четвертого триггера соединен с первым входом во.сьмого элемента И и является вторым входом блока, а другой вход - с одним из входов/ пятого триггера и выходом четвертого элемента ИЛИ, третий вход которого подключен к первому входу пятого элемента И непосредственно, а к выходу первого счетчика - через второй элемент задержки, первый вход первого счетчика соединен с первым входом второго регистра и выходом пятого элемента ИЛИ, а второй вход - с вторым входом второго регистра и выходом восьмого элемента ИЛИ, первый вход которого подключен к выходу девятого элемента И, один из входов которого соединен с выходом десятого элемента И и является четвертым выходом блока, а другие входы являются входом группы блока, третий вход второго регистра является первым входом блока, а выход подключен к вторым входам соответствуюших элементов И группы, второй вход восьмого элемента ИЛИ соединен с выходом одного из элементов И группы, а первый вход десятого элемента И подключен к первому входу одиннадцатого элемента И и является четвертым входом блока, вfopoй вход десятого элемента И соединен с одним из выходов первого триггера, а третий вход - с выходом четвертого элемента И, второй вход которого подключен к одному из выходов пятого триггера, другой выход которого является вторым выходом блока, а другой вход соединен с выходом седьмого элемента ИЛИ, второй вход которого подключен к выходу седьмого элемента И, второй вход седьмого элемента И соединен с одним из выходов третьего триггера, другой выход которого подключен к второму входу соответствуюш,его элемента И группы и второму входу одиннадцатого элемента И, выход которого соединен с вторыми входами соответствуюш.их элементов И группы, третий вход седьмого элемента ИЛИ подключен к третьему входу третьего элемента ИЛИ и выходу восьмого элемента И, второй вход которого соединен с вторым входом пятого элемента И и одним из выходов первого триггера, а четвертый вход третьего элемента ИЛИ подключен к выходу третьего элемента И, второй вхрд которого соединен с первым входом первого элемента И.

3. Устройство по п. 1, отличающееся тем, что блок управления содержит девятый элемент ИЛИ, входы которого являются групповым и третьим входами блока, а выход подключен к первым входам двенадцатого и тринадцатого элементов И и входу второго счетчика, первый выход которого соединен с первым входом четырнадцатого элемента И, а второй выход - с первыми входами пятнадцатого и шестнадцатого элементов И, второй вход шестнадцатого элемента И подключен к второму входу двенадцатого элемента И и выходу шестого триггера, один из входов которого через третий элемент задержки соединен с выходом шестнадцатого элемента И, а другой вход - с выходом десятого элемента ИЛИ, входы которого подключены к соответствуюшим входам девятого и одиннадцатого элементов ИЛИ, входы одиннадцатого элемента ИЛИ являются третьим, пятым и шестым входами блока, а выход соединен с первым входом третьего регистра, второй вход которого подключен к выходу двенадцатого элемента ИЛИ, входы которого соединены с выходами двенадцатого и тринадцатого элементов И, второй вход которого подключен к одному из выходов седьмого триггера, входы которого являются шестым входом блока, второй вход четырнадцатого элемента И соединен с первым входом семнадцатого элемента И и одним из входов девятого элемента ИЛИ, а выход - с первым входом тринадцатого элемента ИЛИ непосредственно и с одним из входов восьмого триггера - через четвертый элемент задержки, другой вход восьмого триггера подключен к первому входу третьего счетчика и выходу четырнадцатого элемента ИЛИ, первый вход которого является четвертым входом блока, а второй вход соединен через пятый элемент задержки с выходом четвертого счетчика, последовательно соединенного с пятым счетчиком, выходы четвертого и пятого счетчиков являются первым выходом блока, а выход четвертого счетчика подключен к входу шестого элемента задержки, выход которого является четвертым выходом блока, вход пятого счетчика соединен с выходом пятнадцатого элемента ИЛИ, первый вход которого подключен к одному из входов десятого элемента ИЛИ, а второй вход -.к выходу семнадцатого элемента И, второй вход которого соединен с выходом восьмого триггера, второй вход третьего счетчика через седьмой элемент задержки подключен к выходу тринадцатого элемента ИЛИ, второй вход которого соединен с выходом пятнадцатого элемента И, второй вход которого подключен к выходу элемента НЕ, вход которого является вторым входом блока, выходы четвертого и пятого элементов задержки и семнадцатого элемента И являются третьим выходом блока, а другой выход седьмого триггера, выходы третьего регистра, третьего счетчика, третьего элемента задержки и четырнадцатого элемента И являются вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования графической информации | 1982 |

|

SU1068982A1 |

| Устройство для отображения информации | 1991 |

|

SU1807520A1 |

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1096675A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1037296A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для отображения информации | 1987 |

|

SU1476523A1 |

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1164763A2 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ, содержащее блок управления, первый выход которого является первым выходом устройства, а второй выход подключен к входу блока памяти, выход которого соединен с информационным входом первого регистра, управляющий вход которого подключен к третьему выходу блока управления, а выход является вторым выходом устройства, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит блок задания режима работы, первый вход: которого является информаци онным входом устройства, второй и третий входы - входами признаков устройства, четвертый вход - тактовым входом устройства, а пятый вход соединен с первым входом блока управления и является входом начальной установки устройства, группу последовательно соединенных коммутаторов, первый вход первого из которых подключен к первому выходу блока задания режима работы, второй выход которого является третьим выходом устройства, а третий выход соединен с вторым входом блока управления и является четвертым выходом устройства, блоки декодирования, первые входы которых подключены к четвертому выходу блока задания режима работы, пятый выход и щестой вход которого соединены с третьим входом и четвертым выходом блока управления соответственно, и дополнительный коммутатор, входы которого подключены к первым выходам блоков декодирования, вторые выходы которых соединены с входами группы блока управления, четвертый вход которого подключен к седьмому входу блока задания режима работы, одному из выходов дополнительного коммутатора и является пятым выходом устройства, остальные выходы дополнительного коммутатора соединены с первыми входами соответствующих коммутаторов группы и с вторыми входами блоков декодирования, кроме последнего и предпостеднего, второй вход которого подключен к первому входу одного из коммутаторов группы и первому выходу последнего блока декодирования, второй вход последнего блоi ка декодирования соединен с выходом одного из коммутаторов группы, а третий вход (Л каждого блока декодирования, кроме первого, подключен к второму входу соответствующего коммутатора группы и третьему вь1ходу предыдущего блока декодирования; третий выход последнего блока декодирования соединен с вторым входом первого коммутатора группы, выход которого подключен к пятому входу блока управления, шестой вход которого является сигнальным входом устройства, четвертые выходы блоков декодирования соединены с входами группы блока задания режима работы, шестой вы00 ход которого подключен к третьему входу первого блока декодирования, а четвертые входы блоков декодирования, кроме последнего, соединены с выходами соответствующих коммутаторов группы. 2. Устройство по п. 1, отличающееся тем, что блок задания режима работы содержит группу элементов И, выходы которых являются первыми, третьим, пятым и-шестым выходами блока, а первые входы подключены к выходам первого триггера, один из входов которого соединен с выходом первого элемента ИЛИ, а другой - с первым входом второго элемента ИЛИ непосред

1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах ввода-вывода ЭВМ, автоматизированных системах управления и системах отображения информации.

Известно устройство вывода графиков для неоднозначных функций, содержащее последовательно соединенные счетчик адреса, оперативное ЗУ, регистр и формирователь 1.

Недостатком устройства является большая избыточность принимаемых и отображаемых в рецепторном коде графических изображений, а следовательно, большое избыточное время загрузки информационных магистралей под пересылку графической информации, большой избыточный требуемый объем внешней памяти для хранения графической информации в рецепторном коде и большое избыточное время приема графической информации.

Наиболее близким по технической сушности к изобретению является устройство для преобразования графической информации, содержащее первый регистр, выход которого подключен к модулятору ЭЛТ, а второй вход соединен с выходом первого блока памяти, вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго регистра, второй вход котррого соединен с выходом второго блока памяти, вход которого соединен с выходом второго элемента И, первый вход которого соединен с выходом третьего регистра, второй вход которого соединен с выходом третьего блока памяти, выход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом четвертого регистра, вход которого соединен с вторым входом третьего элемента И

и выходом третьего счетчика, вход которого соединен с первым входом третьего регистра, вторым входом второго элемента И и выходом второго счетчика, вход которого соединен с первым входом второго регистра, вторым входом первого элемента И и выходом первого счетчика, вход которого соединен с первым входом первого регистра и выходом генератора импульсов. В данном устройстве информация о графическом изображении предварительно полностью записывается во все три блока памяти и регистр четвертый в «сжатом с- помощью трехкаскадного одномерного самоадаптирующего блочного кодирования виде. Затем с началом развертки графическая информаци-я декодируется в рецепторную матрицу, которая по ходу растровой развертки подается на модулятор ЭЛТ. При этом коэффициент сжатия, а следовательно, выигрыш в объеме внешней памяти для хранения графической информации и времени загрузки информационных магистралей в среднем составляет не менее 60% от теоретического максимально возможного коэффициента сжатия графических изображений 2.

Недостатки известного устройства следующие. Сложность, обусловленная необходимостью использования в самом устройстве большого избыточного объема памяти для хранения графической информации, так

как для осуществления возможности отображения абсолютно любой графической информации с вероятностью равной единице необходимо, чтобы объем первого блока памяти был равен объему информационного рельефа экрана (например, для огображения изображения, в котором единицы и нули, соответствующие черным и белым элементам разложения изображения, еледуют поочередно друг за другом, или для отображения изображения, состоящего из одних единиц). Таким образом, в результате получается проигрыш в объеме памяти даже по сравнению с обычным пЪлнографическим дисплеем с рецепторным методом кодирования графической информации на величину объема памяти, равного сумме объемов памяти второго, третьего блоков памяти и четвертого регистра. Данный недостаток обусловлен тем, что устройство не позволяет декодировать и преобразовывать в рецепторный код «сжатую графическую информацию по мере поступления в устройство. Ограниченные функциональные возможности, поскольку в устройстве отсутствует возможность ввода в устройство с целью вывода из него в дальнейшем «несжатой графической информации в рецепторном коде, что ограничивает область его применения Кроме того, поскольку декодирование графической информации и соответственно появление рецепторной матрицы графического изображения на выходе устройства происходит только в процессе отображения, то это не позволяет технически осуществлять редактирование графической информации с помощью светого пера. Неоптимальное с точки зрения получения максимального коэффициента сжатия кодирование «сжатой графической информации, записываемой в устройстве, т.е. определенная степень избыточности необходимой для записи в устройство «сжатой графической информации, а следовательно, также избыточность внешней памяти для хранения графической информации и времени загрузки информационных магистралей под пересылку графической информации. Наиболее оптимальным с точки зрения достижения максимального «сжатия графической информации является многокаскадное блочное кодирование с учетверением в каждом следующем звене (объеме кодируемой графической информации) количества кодируемой графической информации. Поэтому более оптимальным с точки зрения максимального «сжатия для объема графической информации, равного объему информационного рельефа экрана ЭЛТ, является не трехкаскадное одномерное самоадаптирующееся блочное кодирование, примененное в прототипе, а шестикаскадное самоадаптирующееся одномерное блочное кодирование, при котором достигаемый коэффициент сжатия составляет порядка 80- 90°/о от теоретического максимально возможного коэффициента сжатия.

Цель изобретения - повышение быстродействия и упрощение устройства.

Поставленная цель достигается тем, что устройство для преобразования графической информации, содержащее блок управления.

первый выход которого является первым выходом устройства, а второй выход подключен к входу блока памяти, выход которого соединен с информационным входом первого регистра, управляющий вход которого подключен к третьему выходу блока управления, а выход является вторым выходом устройства, содержит блок задания режима работы, первый вход которого является информационным входом устройства, второй и

третий входы - входами признаков устройства, четвертый вход - тактовым входом устройства, а пятый вход соединен с первым входом блока управления и является входом начальной установки устройства, группу последовательно соединенных коммутаторов, первый вход первого из которых подключен к первому выходу блока задания режима работы, второй выход которого является третьим выходом устройства, а третий выход соединен с вторым входом блока управления и является четвертым выходом устройства, блоки декодирования, первые входы которых подключены к четвертому выходу блока задания режима работы, пятый выход и шестой вход которого соединены с третьим входом и четвертым выходом блока управления соответственно, и дополнительный коммутатор, входы которого подключены к первым выходам блоков декодирования, вторые выходы которых соединены с входами группы блока управления, четвертый

0 вход которого подключен к седьмому входу блока задания режима работы, одному из выходов дополнительного коммутатора и является пятым выходом устройства, остальные выходы дополнительного коммутатора соединены с первыми входами соответствующих коммутаторов группы и с вторыми входами блоков декодирования, кроме последнего и предпоследнего, второй вход которого подключен к первому входу одного из коммутаторов группы и первому выходу последнего блока декодирования, второй вход последнего блока декодирования соединен с выходом одного из коммутаторов группы, а третий вход каждого блока декодирования, кроме первого, подключен к второму входу соответствующего коммутатора группы и

5 третьему выходу предыдущего блока декодирования, третий выход последнего блока декодирования соединен с вторым входом первого коммутатора группы, выход которого подключен к пятому входу блока управления, шестой вход которого является сигнальным входом устройства, четвертые выходы блоков декодирования соединены с входами группы блока задания режима работы, шестой выход которого подключен к третьему входу первого блока декодирования, а

5 четвертые входы блоков декодирования, кроме последнего, соединены с выходами соответствующих коммутаторов группы. Блок задания режима работы содержит группу элементов И, выходы которых являются первым, третьим, пятым и шестым выходами блока, а первые входы подключены к выходам первого триггера, один из входов которого соединен с выходом первого элемента ИЛИ, а другой - с первым входом второго элемента ИЛИ непосредственно и с выходом первого элемента И через первый элемент задержки, первый вход первого элемента И подключены к первым входам первого элемента ИЛИ и второго элемента И и является uiecTbiM входом блока, а второй вход - к одному из выходов второго триггера, другой вход которого соединен с первыми входами третьего, четвертого и пятого элементов И, один из входов второго триггера является третьим входом блока, а другой вход подключен к выходу второго элемента ИЛИ, второй вход которого соединен с первыми входами третьего, четвертого и пятого и вторым входом первого элемептов .ИЛИ и является пятым входом блока, вторые входы третьего, четвертого и пятого элементов ИЛИ являются седьмым входом блока, а выход третьего элемента ИЛИ подключен к одному из входов третьего триггера, другой вход которого соединен с выходом шестого элемента ИЛИ, первый вход шестого элемента ИЛИ подключен к выходу пятого элемента И, а второй вход - к второму входу соответствующего элемента И группы и выходу шестого элемента И, второй вход которого соединен с первым входом седьмого элемента ИЛИ и выходом второго элемента И, второй вход которого подключен к первому входу седьмого элемента И и к выходу четвертого триггера, один из входов четвертого триггера соедииен с первым входом восьмого элемента И и является-вторым входом блока, а другой вход - с одним из входов пятого триггера и выходом .четвертого элемента ИЛИ, третий вход которого подключен к первому входу пятого элемента И непосредственно, а к выходу первого счетчика - через второй элемент задержки, первый вход первого счетчика соединен с первым входом второго регистра и выходом пятого элемента ИЛИ, а второй вход - с вторым входом второго регистра и выходом восьмого элемента ИЛИ, первый вход которого подключен к выходу девятого элемента И, один из входов которого соединен с выходом десятого элемента И и является четвертым выходом блока, а другие входы являются входом группы блока, третий вход второго регистра является первым входом блока, а выход подключен к вторым входам соответствующих элементов И группы, второй вход восьмого элемента. ИЛИ соединен с выходом одного из элементов И группы, а первый вход десятого элемента И подключен к первому входу одиннадцатого элемента И и является четвертым входом блока, второй вход десятого элемента И соединен с одним из выходов первого триггера, а третий вход - с выходом четвертого элемента И, второй вход которого подключен к одному из выходов пятого триггера, другой выход которого является вторым выходом блока, а другой вход соединен с выходом седьмого элемента ИЛИ, второй вход которого подключен к выходу седьмого элемента И, второй вход седьмого элемента И соединен с одним из выходов третьего триггера, другой выход которого подключен к второму входу соответствующего элемента И группы и второму входу одиннадцатого элемента И, выход которого соединен с вторыми входами соответствующих элементов И группы, третий вход седьмого элемента ИЛИ подключен к третьему входу третьего элемента ИЛИ и выходу восьмого элемента И, второй вход которого соединен с вторым входом пятого элемента И и одним из выходов первого триггера, а четвертый вход третьего элемента ИЛИ подключен к выходу третьего элемента И, второй вход которого соединен с первым входом первого элемента И. Блок управления содержит девятый элемент ИЛИ, входы которого являются групповым и третьим входами блока, а выход подключен к входам двенадцатого и тринадцатого элементов И и входу второго счетчика, первый выход которого соединен с первым входом четырнадцатого элемента И, а второй выход - с первыми входами пятнадцатого и шестнадцатого элементов И, второй вход шестнадцатого элемента И подключен к второму входу двенадцатого элемента И и выходу шестого триггера, один из входов которого через третий элем.ецт задержки соединен с выходом шестнадцатого элемента И, а другой вход - с выходом десятого элемента ИЛИ, входы которого подключены к соответствующим входам девятого и одиннадцатого элементов ИЛИ, в.ходы одиннадцатого элемента ИЛИ являются третьим, пятым и шестым входами блока, а выход соединен с первым входом третьего регистра, второй вход которого подключен к выходу двенадцатого элемента ИЛИ, выходы которого соединены с выходами двенадцатого и тринадцатого элементов И, второй вход которого подключен к одному из выходов седьмого триггера, входы которого являются шестым входом блока, второй вход четырнадцатого элемента И соединен с первым входом семнадцатого элемента И и одним из входов девятого элемента ИЛИ, а выход - с первым входом тринадцатого элемента ИЛИ непосредственно и с одним из входов вось.мого триггера - через четвертый элемент задержки, другой вход восьмого триггера подключен к первому входу третьего счетчика и выходу четырнадцатого элемента ИЛИ, первый вход которого является

четвертым входом блока, а второй вход соединен через пятый элемент задержки с выходом четвертого счетчика, последовательно соединенного с пятым счетчиком, выходы четвертого и пятого счетчиков являются первым выходом блока, а выход четвертого счетчика подключен к входу шестого элемента задержки, выход которого является четвертым выходом блока, вход пятого счетчика соединен с выходом пятнадцатого элемента ИЛИ, первый вход которого подключен к одному из входов десятого элемента ИЛИ, а второй вход - к выходу семнадцатого элемента И, второй вход которого соединен с выходом восьмого триггера, второй вход третьего счетчика через седьмой элемент задержки подключен к выходу тринадцатого элемента ИЛИ, второй вход которого соединен с выходом пятнадцатого элемента И, второй вход которого подключен к выходу элемента НЕ, вход которого является вторымвходом блока, выходы четвертого и пятого элементов задержки и семнадцатого элемента И являются третьим выходом блока , а другой выход седьмого триггера, выходы третьего регистра, третьего счетчика, третьего элемента задержки и четырнадцатого элемента И являются вторым выходом блока. Устройство позволяет принимать, декодировать и записывать в ЗУ регенерации а затем отображать как «сжатую с помощью шестикаскадного самоадаптирующегося одномерного блочного кода, так и «несжатую графическую информацию в виде рецепторной матрицы изображения. Под рецепторной матрицей подразумевается матрица, число разрядов которой равно информационной емкости экрана ЭЛТ (числу элементов разложения в строке, помноженному на число строк, задействованных для отображения). Наличие черного элемента в определенном месте экрана соответствует записи в соответствующем разряде рецепторной матрицы единицы, запись же нуля соответствует белому фону на экране. В устройстве принят стандартный телевизионной метод отображения с чересстрочной разверткой. Частота регенерации полукадров 50 Гц. Во избежание чересстрочных мельканий, утомляющих оператора, информация в четном и нечетном полукадрах одинакова.

Методика самоадаптирующегося блочного кодирования состоит в следующем. Сначала изображение разбивается на больщие блоки, называемые исходными, которые кодируются один за другим. Если все элементы изображения в данном блоке белые, то он кодируется одним префиксом «О. В остальных случаях блоку приписывается префикс «1, после чего блок подразделяется на несколько субблоков. Каждый из субблоков подвергается такой же процедуре, что и исходный бло-к, до тех пор, пока в конечном счете не получается элементарный субблок, который кодируется с помощью обычного префиксного блочного кода. Такая методика эквивалента указанному иерархическому разбиению на блоки и относительно проста, поскольку на каждом этапе требуется лищь . выявлять блоки, состоящие из одних белых (фоновых) элементов. С целью упрощения в устройстве принята следующая иерархия

разбиения рецепторной матрицы изображения на блоки следующих размеров. 288 строк разбиваются на 18 групп по 16 строк. Каждая из 18 групп разбивается на 4 подгруппы по 4 строки, которые в свою очередь разбиваются на 4 подгруппы по 1 строке в подгруппе. Каждая строка разбивается на 7 подгрупп по 64 э.темента разложения изображения. В свою очередь каждая подгруппа ИЗ64 элементов разбивается на 4 подгруппы по 16 элементов, которые в свою очередь

разбиты на 4 подгруппы по 4 элемента разложения изображения в каждой.

Кодирование происходит следующим образом.

Вначале анализируется первая из 18 групп по 16 строк. Если она состоит из одного фона, т.е. одних нулей, то кодируется одной цифрой - префиксом «О и происходит переход к анализу следующей второй группы из 16 строк. Если и во второй группе отсутствует информация, то записывается второй «О и происходит переход к анализу третьей группы из 16 строк. Допустим в 3-й группе есть информация. В этом случае записывается префикс «1 и начинается анализ каждой из 4 подгрупп по 4 строки в этой 3-й

группе. Если первые 3 подгруппы состоят из нулей, а в четвертой подгруппе есть информация, то записывается три нуля, а затем префикс «1, и происходит переход к анализу 4 подгрупп по 1 строке в каждой, составляющих 4-ю подгруппу из 4 строк и т.д. В конце происходит переход к анализу подгрупп по 4 элемента разложения в каждой и в случае, если в подгруппе одни нули, то она кодируется одним разрядом, префиксом «О, а если в подгруппе есть информация,

то она кодируется префиксом «1, после чего записываются в рецепторном коде все 4 анализируемые разряда, соответствующие 4 элементам разложения информационного рельефа экрана.

Таким образом, в процессе кодирования

кодируются одним разрядом «О и исключаются из рассмотрения блоки, не содержащие информации, вначале размером, соотв тствующим 16 строкам по 448 элементов разложения, затем 4 строкам по 448 элементов,

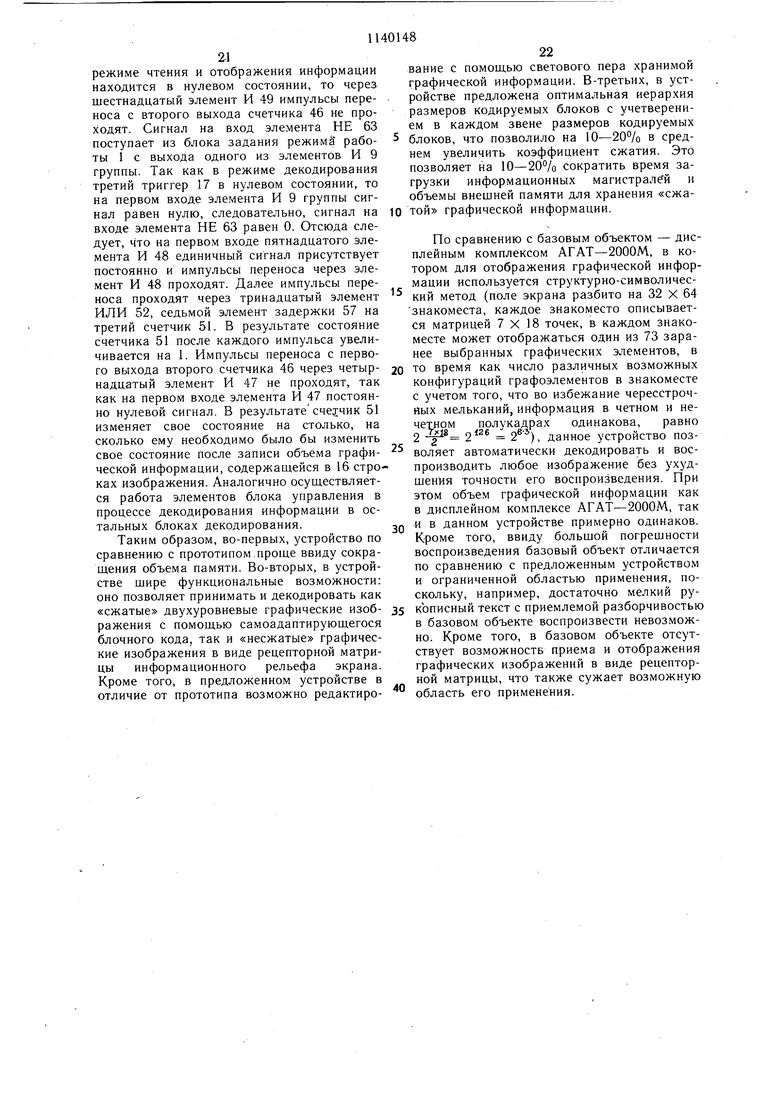

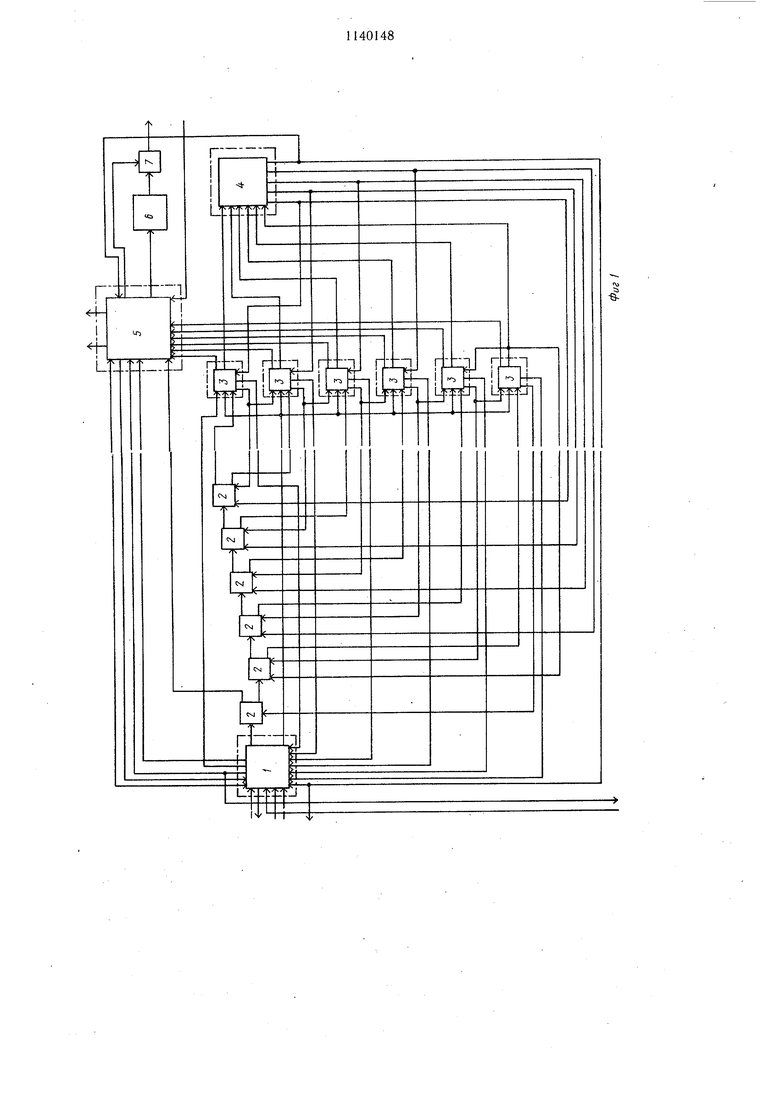

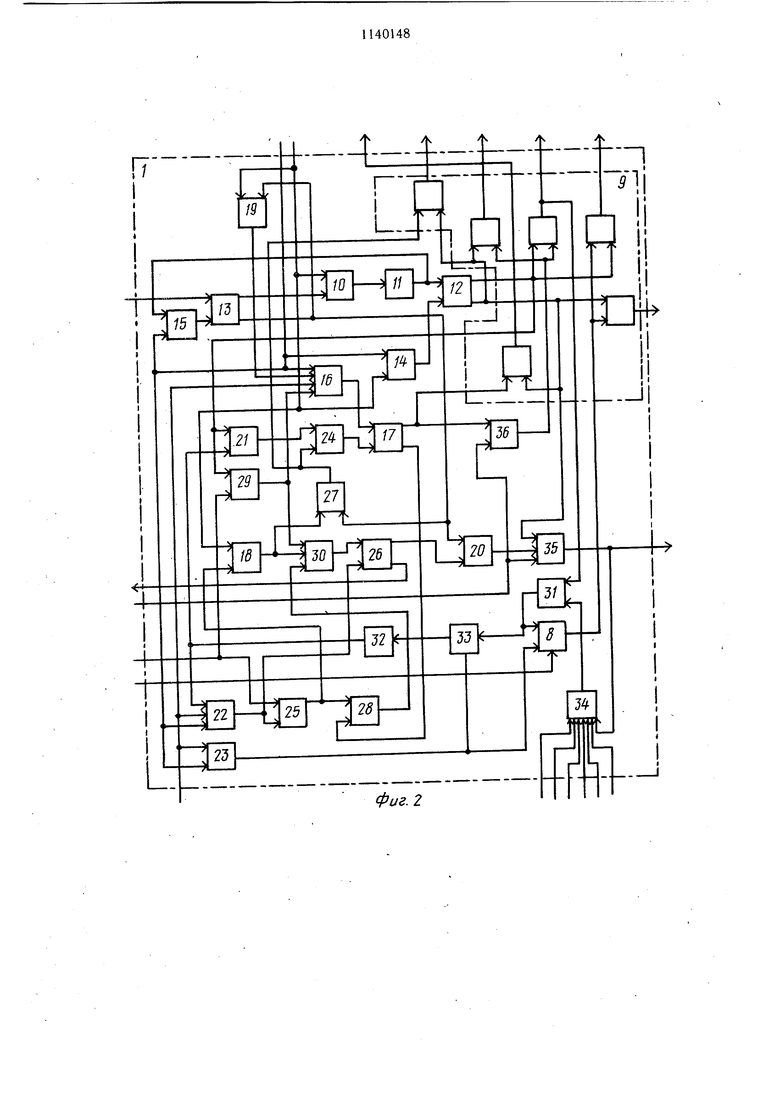

затем 1 строке по 448 элементов, затем 64 элементам, затем 16 элементам и наконец 4 элементам разложения изображения. Предлагаемое устройство производит обратное преобразование графической информации из «сжатой формы в рецепторную матрицу, соответствующую информационному рельефу экрана. Затем декодированная графическая информация записывается в ЗУ хранения информационного рельефа графического изображения. Кроме того, предлагаемое устройство при наличии соответствующего управляющего сигнала может пропускать и записывать в ЗУ регенерации «несжатую графическую информацию в виде рецепторной матрицы. Устройство, таким образом, позволяет декодировать «сжатую с помощью щестикаскадного самоадаптирующегося одномерного блочного кода графическую информацию по мере ее поступления (побайтно) в рецепторную матрицу графического изображения и записывать эту рецепторную матрицу графического изображения в ЗУ регенерации для отображения и при необходимости редактирования с помощью светового пера. При этом возможно декодирование абсолютно любых графических изображений, а поскольку декодирование осуществляется по мере поступления «сжатой графической информации, то в самом узле декодирования используется для временного хранения поступающей «сжатой графической информации всего лищь регистр на 8 разрядов, в то время как для той же цели в прототипе используются три блока памяти и четвертый регистр. Требуемый объем памяти для декодированной графической информации (рецепторной матрицы) равен информационной емкости экрана т.е. объему памяти полнографических дисплеев и, следовательно, меньще, чем в прототипе, на величину суммарного объема второго, третьего блоков памяти и четвертого регистра. Коэффициент сжатия графической информации, .декодируемой устройством, больще, чем в прототипе, и для типичных графических изображений составляет 80- 90% от теоретического максимально возможного коэффициента сжатия, т.е. избыточность декодируемой графической информации значительно меньще, чем в прототипе. Повыщение коэффициента сжатия графической информации позволяет сократить время загрузки внещних информационнь1х магистралей под пересылку «сжатой графической информации, уменьщить объем внещней памяти для хранения «сжатой графической информации и время приема «сжатой графической информации устройством. Кроме того, устройство позволяет принимать по байтам, отображать и при необходимости редактировать с помощью светового пера как сжатую с помощью самоадаптирующегося блочного кода, так и «несжатую графическую информацию в виде рецепторного кода. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема блока задания режима работы; на фиг. 3 - функциональная схема блока управления. Устройство содержит блок задания режима работы 1 коммутаторы 2, блоки декодирования 3, дополнительный коммутатор 4, блок управления 5, блок памяти 6, первый регистр 7, второй регистр 8, группу элементов И 9, первый элемент И 10, первый элемент задержки И, первый триггер 12, второй триггер 13, первый элемент ИЛИ 14, второй элемент ИЛИ 15, третий элемент ИЛИ 16, третий триггер 17, второй элемент И 18, третий элемент И 19, четвертый элемент И 20, пятый элемент И 21, четвертый элемент ИЛИ 22, пятый элемент ИЛИ 23, щестой элемент ИЛИ 24, четвертый триггер 25, пятый триггер 26, щестой элемент И 27, седьмой элемент И 28, восьмой элемент И 29, седьмой элемент ИЛИ 30, восьмой элемент ИЛИ 31, второй элемент задерж ки 32, первый счетчик 33, девятый элемент И 34, десятый элемент И 35, одиннадцатый элемент И 36, девятый элемент ИЛИ 37, десятый элемент ИЛИ 38, одиннадцатый элемент ИЛИ 39, ще.стой триггер 40, седьмой триггер 41, двенадцатый элемент И 42, тринадцатый элемент И 43, двенадцатый элемент ИЛИ 44, третий регистр 45, второй счетчик 46, четырнадцатый элемент И 47, пятнадцатый элемент И 48, щестнадцатый элемент И 49, третий элемент задержки 50, третий счетчик 51, тринадцатый элемент ИЛИ 52, четырнадцатый элемент ИЛИ 53, четвертый элемент задержки 54, пятый элемент задержки 55, щестой элемент задержки 56, седьмой элемент.задержки 57, четвертый счетчик 58, пятый счетчик 59, пятнадцатый элемент ИЛИ 60, семнадцатый элемент И 61, восьмой триггер 62 и элемент НЕ 63. Устройство работает следующим образом. Блок 1 задания режима работы предназначен для приема в параллельном коде очередного байта графической информации, выдачи этого байта в последовательном коде в зависимости от управляющих сигналов на входе блока, только на вход блока управления 8 (информация не закодирована рецепторным кодом и представлена в виде рецепторной матрицы) либо, через коммутаторы 2 на блоки декодирования 3 и блок управления 8. По окончании декодирования и записи рецепторной матрицы графического изображения в блок памяти 6 или по окончании «транзитной передачи незакодированной графической информации блок задания режима работы 1 автоматически переводит устройство в режим непрерывного чтения с регенерацией. Кроме того, блок задания режима работы синхронизирует процесс декодирования графической информации со скоростью поступления очередных байтов графической информации, т.е. по окончании декодирования или транзитной пересылки в блок управления, блок 1 выдает сигнал о готовности к приему следующего байта графической информации. Коммутатрры 2 предназначены для коммутации поступающих входных сигналов (в зависимости от управляющих сигналов на первом и втором входах). Блок управления 5 предназначен для управления записью и считыванием графической информации в блок памяти 6. Первый блок декодирования служит для определения того факта, какое значение (нулевое или единичное) имеют префиксные разряды, кодирующие первичные группы по 16 строк в каждой. Всего в закодированной графической информации таких префиксных разрядов 18, т.е. равно количеству первичных групп по 16 строк, на которые разбита рецепторная матрица графического изображения. Если значение префикса равно О, то в блоке памяти 6 ничего не записывается, а И- J,fтретий счетчик 51 в блоке управления 5 под действием сигналов из первого блока декот1ЛТ1/- ТОГл: ЛЛ/ иГиоП/Ю1ЛОГЮГЧ13ОГч Г ТТГ 1 ОПСЧ// дирования меняет значение адреса на величину, необходимую для записи объема памяти, соответствующего; объему памяти на 16 строках графического изображения (448 X 16/8 896, в блоке памяти 6 по каждому адресу хранится один байт графической информации в рецепторном коде). Если префикс равен 1, то первый-блок декодирования переключает последний ко.ммутатор группы так, что его вход коммутирует,ся на выход и далее на четвертый вход следующего блока декодирования. При этом в следующий блок декодирования одновременно из первого блока декодирования посылается импульс инициирован :1Я начала декодирования, по которому второй блок декодирования определяет значение следующего разряда. Следующий блок декодирования анализирует префиксные разряды, относящиеся к каждой из 4 подгрупп по 4 строки в каждой, на которые разбита анализируемая первичная группа из 16 строк, значение префиксного разряда которой, определенное первым блоком декодирования, равно 1. Если очередное значение префикса подгруппы равно «О, то это означает, что в очередных 4 строках графической информации от сутствует информация (один фон). В этом случае третий счетчик (счетчик адреса),51 в блоке управления 5 под действием сигналов из блока декодирования меняет свое значение на величину, необходимую для записи объема информации, который содержится в четырех строках графического изображения (448 X 4/8 224). После этого -блок декодирования анализирует следующий префиксный разряд, относящийся к следующей подгруппе графической информации на 4 строках. Если очередной префиксный разряд равен 1, то в соответствующем коммутаторе группы управляющим сигналом с блока декодирования первый вход переключается на выход и далее на четвертый вход следующего по порядку блока декодирования. Кроме того, тот же управляющий сигнал из блока декодирования поступает и на следующий по порядку блок декодирования для инициирования (запуска) его работы. Следующий по порядку блок декодирования в соответствии с иерархией разбиения блоков анализирует наличие или отсутствие информации в каждой из 4 строк, на которые разбита подгруппа из 4 строк с единичным префиксо.м. Алгоритм работы следующего блока декодирования аналогичен алгоритму работы предыдущего. Следующий блок декодирования анализирует наличие или отсутствие информации в каждой из 7 подгрупп по 64 элемента разложения изображения, на которые разбита каждая строка графической информации. Алгоритм работы его аналогичен алгоритмам ibi/j.. ui %, и11ЬД,. Clt/llVyt/rillriCtl работы предыдущих блоков декодирования 3. Следующий по порядку блок декодирования анализирует наличие или отсутствие нефоновой информации в каждой из 4 подгрупп по 16 элементов разложения, на которые разбиты.подгруппы из 64 элементов разложения, анализируемые блоком декодирования 14. Анализируются подгруппы по 16 элементов только тех подгрупп из 64 элементов, префикс которых, определенный предыдущим блоком декодирования, равен 1. Последний блок декодирования анализирует наличие или отсутствие информации -в каждой из 4 подгрупп по 4 элемента разложения, на которые разбиты подгруппы из 16 элементов разложения изображения. Если нефоновая информация в тетраде отсутствует, значение второго счетчика 46 в блоке управления 5 меняется на 4. Если анализируемый префикс равен «1, то очередные 4 разряда ненулевой тетрады записываются в блок памяти 6 в соответствующее место рецепторной матрицы. Каждый из блоков декодирования имеет счетчик анализируемых групп или подгрупп. В соответствии с иерархией разбиения в первом блоке декодирования счетчик считает до 18, во втором блоке с периодом 4, а в следующем 4, далее 7, затем 4 и в последнем с периодом 4. Выходы счетчиков поданы на дополнительный коммутатор 4, который осуществляет необходимую коммутацию коммутаторов группы и подключение блоков декодирования в обратном направлении снизу вверх. Например, когда последний блок декодирования проанализировал очередные 4

13

тетрады по 4 элемента разложения, то он посылает импульс, который поступает на один из коммутаторов группы, предыдущий блок декодирования и дополнительный коммутатор 4. Под действием этого импульса вход коммутатора коммутируется на выход и далее на вход следующего коммутатора, а далее на четвертый предыдущего блока декодирования. В блоке декодирования при этом инициируется начало анализа префиксного разряда очередной подгруппы из 16 разрядов. Если же в блоке декодирования проанализированы все четыре префиксных разряда четырех подгрупп по 16 разрядов, то с выхода счетчика до 4 этого блока на вход дополнительного коммутатора 4 подан потенциальный единичный сигнал. В этом случае импульсным сигналом конца декодирования последних 4 разрядов в четвертой 16-р23рядной подгруппе с выхода последнего блока декодирования начало анализа очередного префиксного разряда в предыдущем блоке декодирования не инициируется, а инициируется начало анализа префиксного разряда очередной подгруппы из 64 разрядов в предшествующем по порядку блоке декодирования из дополнительного коммутатора 4. Кроме того, из дополнительного коммутатора 4 импульсный сигнал поступает на второй вход соответствующего коммутатора группы и вход коммутатора коммутируется через выход на вход соответствующего блока декодирования, далее через последующий коммутатор на вход соответствующего блока декодирования. .В дальнейщем инициация работы блоков декодирования аналогична алгорит.му работы предыдущих блоков декодирования. В конце, когда декодирована вся графическая информация, с выходов счетчиков блоков декодирования, кроме последнего, на дополнительный коммутатор поданы потенциальные сигналы, а с выхода последнего блока декодирования подается импульсный сигнал окончания декодирования последних 4 разрядов рецепторной матрицы, в результате чего дополнительный коммутатор 4 выдает импульсный сигнал окончания декодирования на блок задания режима работы 1, который переводит блок управления 5 в режим непрерывного чтения и отображения на экране ЭЛТ записанной в блоке памяти 6 информации. Если последняя подгруппа графической информации, соответствующая 16 строкам (4 строкам, 1 строке, 64 элементам разложения, 16 элементам разложения рецепторной матрицы), нулевая, то в допол,нительный коммутатор 4 посылается сигнал об этом и блок 4 по окончании установки счетчика 51 в блоке управления 5 в нулевое состояние выдает сигнал об окончании декодирования и начале регенерации на ЭЛТ графической информации.

14

Вход начальной установки устройства предназначен для приема импульса начальной установки устройства от блока развертки. Импульс приходит в момент включения устройства до начала процесса отображения или приема графической информации.

Вход признака предназначен для приема единичного управляющего сигнала, свидетельствующего о том, что получаемая графическая информация не закодирована 0 («не сжата) блочным кодом. По этому сигналу коммутаторы и блоки декодирования отключаются и принимаемая графическая информация без изменений «транзитом через блок задания режима работы 1 записывается в блок па.мяти 6 через блок управления 5.

Третий выход предназначен для подачи сигнала, свидетельствующего о готовности устройства принять очередной байт графической информации.

0 , Вход признаков предназначен для приема управляющего сигнала, свидет&пьствующего о том, что очередной байт графической информации заслан во второй приемный регистр 8 блока 1 задания режима работы

5 и можно продолжить декодирование или переслать этот байт в блок памяти 6 (если принимается незакодированная графическая информация).

Информационный вход предназначен для приема в параллельном коде очередного бай0 та графической информации в прие.мный регястр 8 блока задания режима работы 1.

Пятый вход предназначен для выдачи

из устройства сигнала окончания декодиро-вания графической информации. Выход

может использоваться для контроля исправ5 ности узла декодирования.

Тактовый вход предназначен для приема тактовых импульсов от блока развертки. Частота тактовых импульсов равна частоте следования 448 элементов разложенияв течение прямого хода луча ЭЛТ по строке (59 МКС при принятом в устройстве телевизионном методе развертки).

Четвертый- выход предназначен для выдачи сигнала окончания ,регенерации графического изображения в полукадре. Сигнал

5 выдается в кодер для возможного запуска его работы при необходимости.

Первый выход предназначен для выдачи в блок развертки сигнала окончания вывода 448 элементов разложения информационной строки графического изображения. По этому сигналу блок развертки до начала нового полукадра прекращает выдачу тактовых импульсов, а до начала нового полукадра начинает генерацию тактовых импульсов с таким расчетом, чтобы 9-й по счету

5 тактовый импульс совпадал с началом развертки; для выдачи в кодер сигнала окончания вывода всей рецепторной матрицы

15 графического изображения из блока памяти 6. По этому сигналу кодер выдает последний байт графической информации из устройства, а также сигнал окончания вывода всего графического изображения из устройства. Второй выход предназначен для выдачи кода подсвета графического изображения в последовательном виде построчно в соответствии с разверткой на модулятор ЭЛТ. Сигнальный вход предназначен для приема управляющего импульсного сигнала от усилителя сигнала от светового пера, после приема этого сигнала запись новой информации в блок памяти 6 происходит со стираннем информации, записанной ранее; для приема управляющего импульсного сигнала от усилителя сигнала от светового пера, после приема этого сигнала запись новой инф.эрмации в олок памяти 6 происходит без стирания информации, записанной ранее; для приема сигнала от светового пера, усиленного усилителем сигнала от светового пера. Блок управления и блок задания режима работы функционируют следующим образом. После включения устройства па вход начальной установки поступает импульс начальной установки, по которому блоки устройства устанавливаются в исходное для работы состояние. В блоке задания режима работы 1 этот импульс через первый эле.мент ИЛИ 14 устанавливает первый триггер 12 в нулевое состояние, через второй элемент ИЛИ 15 устанавливает второй триггер 13 в нулевое состояние, через четвертый элемент ИЛИ 22 устанавливает четвертый и пятый триггеры 25 и 26 в нулевое состояние. через пятый элемент ИЛИ 23 устанавливает в нулевое состояние первый счетчик 33, считающий до 8 и второй регистр 8 на 8 разрядов. С нулевого выхода триггера 26 на второй выход поступает высокий единичный потенциал, что свидетельствует о готовности устройства к приему информации. Следом за импульсом начальной установки на тактовый вход поступают тактовые импульсы. В блоке задания режима работы тактовые импульсы поступают на первый вход десятого элемента И 35 и первый вход одинпадцатого элемента И 36. Так как пятый триггер 26 установлен импульсом начальной установки в нулевое состояние, то на втором входе четвертого элемента И 20 нулевой потенциал, следовательно, на выходе элемента И 20, а значит и на третьем входе десятого элемента И 35 нулевой потенциал. Отсюда следует, что тактовые импульсы через элемент И 35 на блоки декодирования не поступают в исходном состоянии. Третий триггер 17 импульсом начальной установки установлен в единичное состояние, значит тактовые импульс.ы через одиннадцатый эле16мент И 36 пройдут. С выхода элемента И 36 тактовые импульсы далее поступают на вторые входы соответствующих элементов И группы 9. Так как первый триггер 12 установлен импульсом начальной установки в нулевое состояние, то на первом входе соответствующего элемента И группы 9 высокий единичный потенциал и тактовые импульсы, следовательно, через один элемент И группы пройДут, а через другой элемент И не пройдут. С выхода данного элемента И группы 9 тактовые импульсы поступают на блок управления 5. В блоке управления 5 тактовые импульсы поступают на третий вход девятого элемента ИЛИ 37, первый вход семнадцато -о элемента И 61 и второй вход четырнадцатого элемента И 47. В исходном состоянии импульсом начальной установки шестой, седьмой и восьмой триггеры 40, 41, 62 установлены в нулевое состояние, второй-пятый счетчики 46, 51, 58, 59 тоже установлены в нулевое состояние, третий регистр 45 также установлен в нулевое состояние. Тактовый импульс с выхода девятого элемента ИЛИ 37 поступает на вход второго счетчика 46 и первые входы двенадцатого и тринадцатого элементов И 42, 43. Так как триггеры 40, 41 в исходном положении в нулевом состоянии, то через элементы И 42, 43 тактовые импульсы не проходят. Второй счетчик 46 имеет период счета 8. На своем первом выходе счетчик 46 выдает периодически один импульс переноса, который, пройдя через четырнадцатый элемент И 47, поступает на второй выход и далее в блок памяти 6 для инициирования считывания очередного байта графической информации по адресу, указываемому третьим счетчиком 51. Рецепторная матрица графического изображения хранится в блоке памяти 6 по байтам, что позволяет снизить требования по быстродействию к блоку памяти. Через четвертый элемент задержки 54 импульс инициирования считывания через третий выход поступает на управляющий вход первого регистра 7. Элемент задержки 54 задерживает импульс на время, необходимое блоку памяти 6 для выдачи на выходных шинах в параллельном коде очередного байта графической информации. Он представляет собой счетчик на определенное количество импульсов с триггером и элементом И, С приходом на его вход импульса инициирования считывания разрещается счет тактовых импульсов. После определенного тактового импульса счетчик выдает на своем выходе импульс переноса и запрещается прохождение в дальнейшем на вход счетчика тактовых импульсов. С приходом импульса на управляющий вход первого регистра 7 в него записывается через информационный вход в параллельном коде байт графической информации с выхода блока памяти 6. Импульс считывания с выхода четырнадцатого элемента И 47 поступает также на первый вход тринадцатого элемента ИЛИ 52 и, пройдя через него, поступает на седьмой элемент задержки 57, который задерживает импульс на время несколько большее, чем время цикла обращения к блоку памяти 6. Структура построения элемента задержки 57 аналогична структуре построения .элемента задержки 54. С выхода элемента задержки 57 импульс поступает на третий счетчик (счетчик адреса) 51, увеличивая его состояние на 1, подготавливая тем самым схему к считыванию следующего очередного байта графической информации. Второй счетчик 46 выдает на своем первом выходе импульс периодически один раз на 8 приходящих импульсов с таким расчетом, чтобы первый импульс, пройдя через элемент И 47 и Элемент задержки 54, в начальныи момент установил восьмой триггер 62 в единичное состояние и через семнадцатый элемент И 61 прошел на третий выход и далее на первый регистр 7 9-й по счету тактовый импульс. Время задержки элемента задержки 54 подбирается из условия того, чтобы в начальный момент первый импульс на управляющий вход первого регистра 7 приходил на полтакта раньше девятого тактового импульса, пропущенного элементом И 61. В дальнейшем восьмой триггер 62 остается открытым и тактовые импульсы постоянно проходят через элемент И 61 на управляющий вход первого регистра 7 и второй вход пятнадцатого элемента ИЛИ 60. Тактовые импульсы с выхода элемента И 61 поступают на второй вход пятнадцатого элемента ИЛИ 60, а с его выхода на вход пятого счетчика 59. Счетчик 59 считает с периодом 448 и выдает на своем выходе с каждым 448-м импульсом импульс переноса, который поступает на четвертый счетчик 58 и на первый выход блока 5 и далее на первый выход устройства для формирования растра полукадра (не показано). С получением 448 тактовых импульсов, с 448-м тактовым импульсом с выхода счетчика 59 на первый выход устройства подается импульс переноса, по Которому выдача тактовых импульсов до начала формирования новой телевизионной строки запрещается. С началом формирования очередной телевизионной строки блок развертки начинает выдавать тактовые импульсы. При этом первые 8 тактовых импульсов считают из первого регистра 7 байт графической информации, записанный туда после 448 тактового импульса при формировании предыдущей строки. Четвертый счетчик 58 считает с периодом 288 и с приходом на его вход с выхода счетчика 59 228-го импульса переноса выдает на своем выходе импульс переноса, поступающий через шестой элемент задержки (примерно на три четверти такта) 56 на блок задания режима работы 1. Этот импульс с выхода элемента задержки 56 свидетельствует о том, что из блока памяти 6 полностью считана рецепторная матрица графического изображения. Элемент задержки 54 необходим для того, чтобы не прервать формирование последнего элемента изображения в полукадрё. Импульс переноса с выхода четвертого счетчика 58, кроме того, поступает через пятый элемент задержки 55 и четырнадцатый элеtyieHT ИЛИ 53 на триггер 62 и счетчик адреса 51, а с выхода элемента задержки 55 - на первый выход блока для установки первого регистра 7 в нулевое состояние. Элемент задержки 55 задерживает импульс на такои промежуток врем.ени, и для того, чтобы он не обогнал задержанные импульсы с выходов элементов задержки 54 и 57. Время это составляет порядка не более трех четвертых времени одного такта. Алгоритм работы блока развертки в режиме отображения графической информации осуществляется при наличии специального разрешающего сигнала, формируемого следующим образом. В исходном состоянии первый триггер 12 находится в нулевом состоянии, а третий триггер 17 - в единичном. Следовательно, на выходе соответствующего элемента И 9 группы высокий единичный потенциал, который поступает на третий выход (на кодер), а с него - на блок 5, а также на блок 1. Через кодер сигнал проходит в том случае. если не происходит кодирование и выдача из устройства «сжатой или «несжатой графической информации кодером. При отсутствии разрешающего сигнала формирование телевизионной развертки прекращается и осуществляется из блока 5 только непрерывная выдача тактовых импульсов. Кроме того, при этом запрещается и работа со световым пером. Данный режим используется только при приеме, декодировании и записи в блок памяти 6 графической информации, а также при кодировании и выдаче графичеС.кой информации из устройства. Режим приема, декодирования и записи в блок памяти 6 графической информации осуществляется следующим образом. В блоке задания режима работы 1 в исходном состоянии пятый триггер 26 находится в нулевом состоянии. Сигнал с его нулевого выхода свидетельствует о том, что второй регистр 8 готов к приему графической информации. Первый байт графической информации засылается в параллельном коде в регистр 8, а на первый вход четвертого триггера 25 по второму входу приходит единичный импульсный сигнал, свидетельствующий о том, что байт графической информации заслан в регистр 8. Если сигнал на третьем входе при этом отсутствует, то это свидетельствует о том, что графическая информация закодирована блочным кодом. Сигнал с второго входа переводит триггер 25 в единичное состояние. Единичный сигнал с единичного выхода триггера 25 поступает на второй вход второго элемента И-18, первый вход которого соединен с выходом шестого элемента задержки 56. После окончания цикла регенерации с появлением на выходе четвертого счетчика 58 импульса переполнения этот сигнал проходит через элемент задержки 56, поступает на блок задания режима работы 1 и проходит через элемент И 18. С выхода элемента И 18 сигнал поступает на второй вход седьмого элемента ИЛИ 30 и второй вход шестого элемента И 27. С выхода элемента ИЛИ 30 импульс устанавливает пятый триггер 26 в единичное состояние н на втором выходе отсутствует сигнал. Это свидетельствует о том, что байт графической информации принят и устройство приступило к декодированию графической информации. Так как второй триггер 13 в исходном состоянии установлен в нулевое состояние, то на его втором нулевом выходе единичпый сигнал. Этот сигнал подан на первые входы четвертого и шестого элементов И 20 и 27. Таким образом, сигнал с выхода элемента: И 18 проходит через элемент И 27 на второй вход шестого элемента ИЛИ 24, а с его выхода на второй вход (установки нулевого состояния) третьего триггера 17. Триггер 17 устанавливается в нулевое состояние, следовательно, сигнал на выходе соответствуюш,его элемента И 9 группы, а значит на третьем выходе отсутствует. В результате работа со световым пером временно запреш,ета, блок развертки перестает генерировать напряжение развертки и непрерывно выдает тактовые импульсы. Тактовые импульсы прежним путем поступают на блок задания режима работы устройства 1, но через одиннадцатый элемент И 36 они уже ке проходят так как третий триггер 17 в нулевом состоянии. Через десятый элемент И 35 тактовые импульсы проходят, так как на первом входе элемента И 35 единичный сигнал с нулевого выхода первого триггера 12, а на втором - единичный сигнал с выхода четвертого элемента И 20. Кроме того, сигнал с выхода элемента И 27 поступает на первый вход одного из элементов И 9 группы. На второй вход этого элемента И подается единичный сигнал с второго нулевого выхода триггера 12, который в исходном состоянии находится в нулевом состоянии. В результате импульс через данный элемент И 9 группы проходит, а дальше с выходе блока задания режима работы 1 поступает в блок первый декодирования и запускает его в работу. С выхода десятого элемента И 35 тактовые импульсы поступают на блоки декодирования, а также на один из входов девятого элемента И 34. На другие входы элемента И 34 в исходном состоянии поданы из блоков декодирования единичные сигналы. Пройдя через элемент И 34, тактовые импульсы через восьмой элемент ИЛИ 31 поступают на счетный вход первого счетчика 33 и второй вход второго регистра 8. С каждым приходящим импульсом регистр 8 выдает по одному-биту графической информации на своем выходе, а счетчик 33 подсчитывает количество выданных битов графической информации. Период

счета счетчика 33 равен 8. С каждым восьмым приходящим тактовым импульсом счетчик 33 выдает на выходе импульс переноса. Этот импульс, пройдя через второй элемент задержки 32, поступает на первый вход четвертого элемента ИЛИ 22 и с его выхода на вторые входы четвертого и пятого триггеров 25, 26. Триггеры 25, 26 устанавливаются в нулевое состояние. С нулевого выхода триггера 26 на второй выход подается единичный сигнал. Это свидетельствует о

0 том, что устройство закончило декодирование очередного байта графической информации и готово к приему следующего. При этом до приема очередного байта графической информации десятый элемент И 35 тактовые импульсы не пропускает, так как на третьем его входе отсутствует сигнал с выхода четвертого элемента И 20, к второму входу которого подсоединен единичный выход пятого триггера 26. После того, как очередной байт графической информации заслан во второй регистр 8 через первый вход, на второй вход приходит импульс, который перебрасывает в единичное состояние четвертый триггер 25. Так как на втором входе седьмого элемента И 28 в этом случае единичный сигнал с нулевого выхода третьего

5 триггера 17, то на выходе элемента И 28 появляется единичпый сигнал, который, пройдя через седьмой элемент ИЛИ 30, устанавливает триггер 26 в единичное состояние. В этом случае на выходе элемента И 20 появляется едипичный сигнал и тактовые импульсы через элемент И 35 проходят на схемы декодирования. Соответственно поразрядно выдается графическая информация из регистра 8 на блоки декодирования.

В процессе декодирования первый бит

5 Графической инфор.мации с выхода регистра 8 проходит через соответствующий элемент И 9 группы и далее через коммутаторы 2 группы поступает на четвертый вход первого блока декодирования. Импульс запуска процесса декодирования поступает в первый блок декодирования с выхода шестнадцатого элемента И 49. Тактовые импульсы поступают на третий вход девятого элемента ИЛИ 37 в блок управления 5. С выхода элемента ИЛИ 37 импульсы поступают на

5 второй счетчик 46, который с каждым восьмым импульсом на входе выдает на втором выходе импульс переноса. Так как шестой триггер 40 в исходном состоянии, а также в

21 режиме чтения и отображения информации находится в нулевом состоянии, то через шестнадцатый элемент И 49 импульсы переноса с второго выхода счетчика 46 не проходят. Сигнал на вход элемента НЕ 63 поступает из блока задания режимй работы 1 с выхода одного из элементов И 9 группы. Так как в режиме декодирования третий триггер 17 в нулевом состоянии, то на первом входе элемента И 9 группы сигнал равен нулю, следовательно, сигнал на входе элемента НЕ 63 равен 0. Отсюда следует, что на первом входе пятнадцатого элемента И 48 единичный сигнал присутствует постоянно и импульсы переноса через элемент И 48 проходят. Далее импульсы переноса проходят через тринадцатый элемент ИЛИ 52, седьмой элемент задержки 57 на третий счетчик 51. В результате состояние счетчика 51 после каждого импульса увеличивается на 1. Импульсы переноса с первого выхода второго счетчика 46 через четырнадцатый элемент И 47 не проходят, так как на первом входе элемента И 47 постоянно нулевой сигнал. В результате счедгчик 51 изменяет свое состояние на столько, на сколько ему необходимо было бы изменить свое состояние после записи объема графической информации, содержаплейся в 16 строках изображения. Аналогично осуществляется работа элементов блока управления в процессе декодирования информации в остальных блоках декодирования. Таким образом, во-первых, устройство по сравнению с прототипом проще ввиду сокращения объема памяти. Во-вторых, в устройстве щире функциональные возможности: оно позволяет принимать и декодировать как «сжатые двухуровневые графические изображения с помощью самоадаптирующегося блочного кода, так и «несжатые графические изображения в виде рецепторной матрицы информационного рельефа экрана. Кроме того, в предложенном устройстве в отличие от прототипа возможно редактиро22вание с помощью светового пера хранимой графической информации. В-третьих, в устройстве предложена оптимальная иерархия размеров кодируемых блоков с учетверением в каждом звене размеров кодируемых блоков, что позволило на 10-20% в среднем увеличить коэффициент сжатия. Это позволяет на 10-20% сократить время загрузки информационных магистралей и объемы внешней памяти для хранения «сжатой графической информации, По сравнению с базовым объектом - дисплейным комплексом АГАТ-2000М, в котором для отображения графической информации используется структурно-символический метод (поле экрана разбито на 32 X 64 знакоместа, каждое знакоместо описывается матрицей 7X18 точек, в каждом знакоместе может отображаться один из 73 заранее выбранных графических элементов, в то время как число различных возможных конфигураций графоэлементов в знакоместе с учетом того, что во избежание чересстрочных мельканий, информация в четном и нечетном полукадрах одинакова, равно т 18 2 ), данное устройство позволяет автоматически декодировать и воспроизводить любое изображение без ухудщенИя точности его воспроизведения. При этом объем графической информации как в дисплейном комплексе АГАТ-2000М, так и в данном устройстве примерно одинаков. Кроме того, ввиду большой погрешности воспроизведения базовый объект отличается по сравнению с предложенным устройством и ограниченной областью применения, поскольку, например, достаточно мелкий рукописный текст с приемлемой разборчивостью в базовом объекте воспроизвести невозможно. Кроме того, в базовом объекте отсутствует возможность приема и отображения графических изображений в виде рецепторной матрицы, что также сужает возможную область его применения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Друзин Я | |||

| В | |||

| и Коганер С | |||

| Э | |||

| Телевизионные системы отображения информации | |||

| Л., «Энергия, 1975, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1978 |

|

SU732941A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1985-02-15—Публикация

1982-08-09—Подача