Изобретение относится к области вычислительной техники и предназначено для применения в цифровых вычислительных машинах, их памяти и уст- ройствах обмена информацией,а также в каналах связи сетей ЭВМ для повышения верности информации.

Целью изобретения является расширение функциональных возможностей путем обеспечения режима кодирования информации и повышения помехоустойчивости за счет исправления плавающей групповой ошибки.

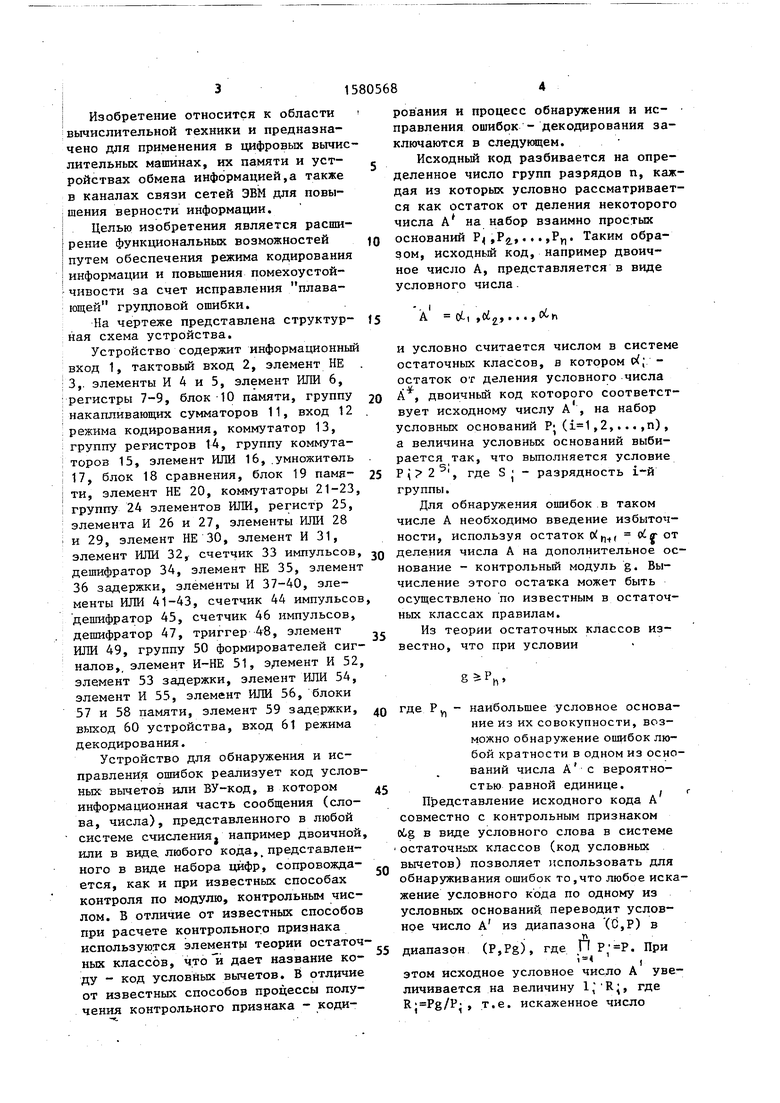

На чертеже представлена структур- ная схема устройства.

Устройство содержит информационный вход 1, тактовый вход 2, элемент НЕ 3, элементы И 4 и 5, элемент ИЛИ 6, регистры 7-9, блок 10 памяти, группу накапливающих сумматоров 11, вход 12 режима кодирования, коммутатор 13, группу регистров 14, группу коммутаторов 15, элемент ИЛИ 16, умножитель 17, блок 18 сравнения, блок 19 памя- ти, элемент НЕ 20, коммутаторы 21-23, группу 24 элементов ИЛИ, регистр 25, элемента И 26 и 27, элементы ИЛИ 28 и 29, элемент НЕ 30, элемент И 31, элемент ИЛИ 32, счетчик 33 импульсов, дешифратор 34, элемент НЕ 35, элемент 36 задержки, элементы И 37-40, элементы ИЛИ 41-43, счетчик 44 импульсов дешифратор 45, счетчик 46 импульсов, дешифратор 47, триггер 48, элемент ИЛИ 49, группу 50 формирователей сигналов, элемент И-НЕ 51, элемент И 52, элемент 53 задержки, элемент ИЛИ 54, элемент И 55, элемент ИЛИ 56, блоки 57 и 58 памяти, элемент 59 задержки, выход 60 устройства, вход 61 режима декодирования.

Устройство для обнаружения и исправления ошибок реализует код условных вычетов или ВУ-код, в котором информационная часть сообщения (слова, числа), представленного в любой системе счисления4 например двоичной, или в виде, любого кода, представленного в виде набора цифр, сопровожда- ется, как и при известных способах контроля по модулю, контрольным числом. В отличие от известных способов при расчете контрольного признака используются элементы теории остаточ- ных классов, что и дает название коду - код условных вычетов. В отличие от известных способов процессы получения контрольного признака - кодирования и процесс обнаружения и исправления ошибок - декодирования заключаются в следующем.

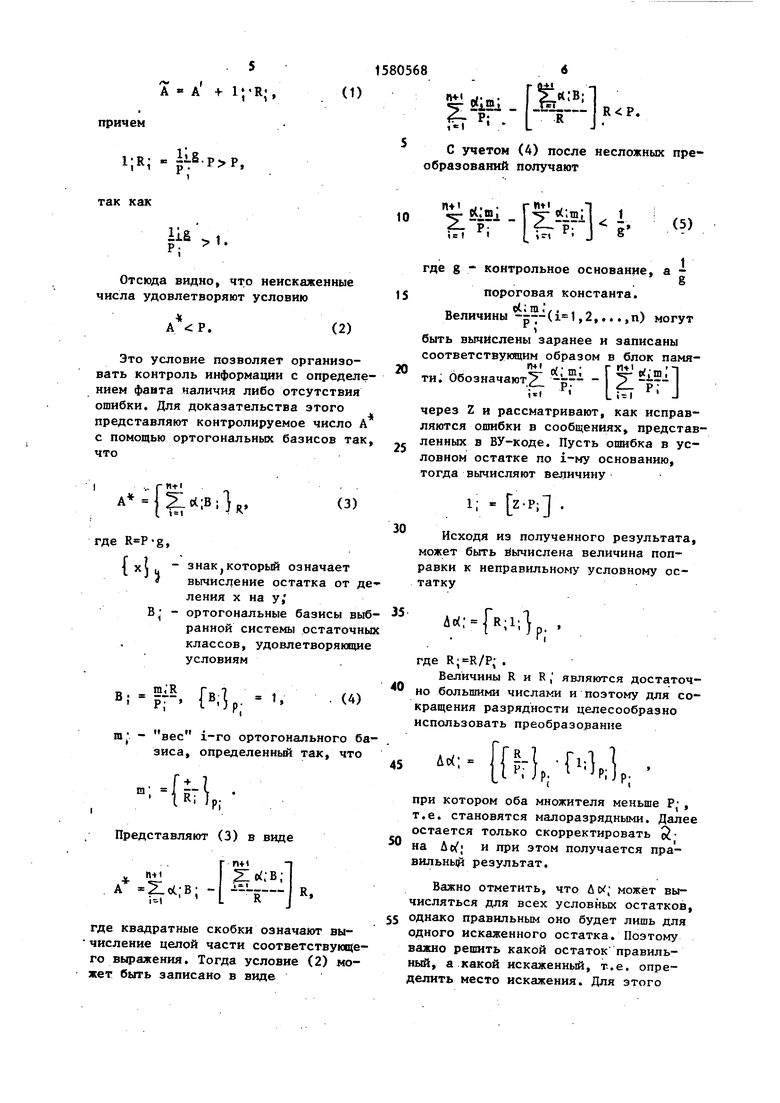

Исходный код разбивается на определенное число групп разрядов п, каждая из которых условно рассматривается как остаток от деления некоторого числа А на набор взаимно простых оснований V,Ј,...,РМ. Таким образом, исходный код, например двоичное число А, представляется в виде условного числа

А с/-| ,сЈг,..., обц

и условно считается числом в системе остаточных классов, в котором tf; - остаток от деления условного числа А , двоичный код которого соответствует исходному числу А , на набор условных оснований Р- (,2,...,п), а величина условных оснований выбирается так, что выполняется условие , где Sj - разрядность 1-й группы.

Для обнаружения ошибок в таком числе А необходимо введение избыточности, используя остаток ( оЈя- от деления числа А на дополнительное основание - контрольный модуль g. Вычисление этого оста-ска может быть осуществлено по известным в остаточных классах правилам.

Из теории остаточных классов известно, что при условии

9 Р

s - h

где Р у, - наибольшее условное основание из их совокупности, возможно обнаружение ошибок любой кратности в одном из оснований числа А с вероятностью равной единице. Представление исходного кода А совместно с контрольным признаком otg в виде условного слова в системе остаточных классов (код условных вычетов) позволяет использовать для обнаруживания ошибок то,что любое искажение условного кода по одному из условных оснований переводит условное число А из диапазона (С,Р) в

диапазон (P,Pg), где П . При

л

этом исходное условное число А увеличивается на величину 1, 1Ц, где Rj Pg/P; т.е. искаженное число

r- i

А + IJ RJ,

(1)

причем

IJR;

ii.e.

,

гг.-№--ЧС учетом (4) после несложных преобразований получают

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и их элементах, использующих код условных вычетов. Наличие двух режимов работы позволяет использовать предлагаемое устройство в устройствах повыщения верности систем передачи данных, а также для повышения верности информации в сетях ЭВМ. Цель изобретения является расширение функциональных возможностей путем обеспечения режима кодирования информации и повышения помехоустойчивости за счет исправления "плавающей" групповой ошибки. Устройство содержит информационный 1 и тактовый 2 входы, элементы НЕ 3,30 и 20, элементы И 4, 5,31,37,38,39,40,52,55,26 и 27, элементы ИЛИ 6,29,32,41,42,43 и 49,56,16,54 и 28, регистры 7,8,9 и 25, счетчики 33,44 и 46 импульсов, дешифраторы 34,47 и 45, группу 50 формирователей сигналов, группу накапливающих сумматоров 11, вход 12 режима кодирования, коммутаторы 13,21,22 и 23, группу регистров 14, группу коммутаторов 15, блоки 10,19,57 и 58 памяти, элемент И-НЕ 51, элементы 36, 59 и 53 задержки, триггер 48,умножитель 17, блок 18 сравнения, группу 24 элементов ИЛИ, выход 60 и вход 61 режима декодирования. 1 ил.

так как

.

Отсюда видно, что неискаженные числа удовлетворяют условию

.

(2)

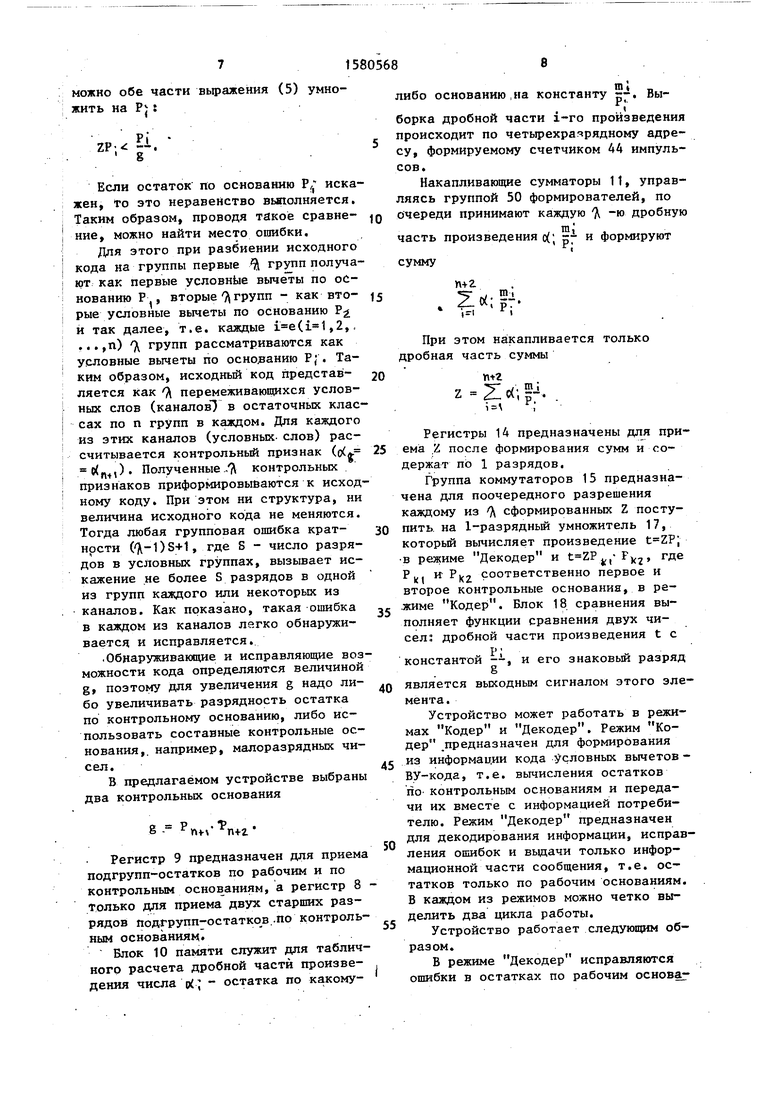

Это условие позволяет организовать контроль информации с определением фанта наличия либо отсутствия ошибки. Для доказательства этого представляют контролируемое число А с помощью ортогональных базисов так, что

fn-н .

(3)

где ,

Н

- знак который означает « вычисление остатка от деления х на у;

- ортогональные базисы выб- 35 Ло( J R l l панной системы остаточных I J Р1

ранной системы остаточных классов, удовлетворяющие условиям

Р;

где .

В;

m, R

Г R 7 - i Р; (Мр; -

га;

- вес 1-го ортогонального базиса, определенный так, что

-(rL

Представляют (3) в виде

(VH

гн«

i-i

R,

где квадратные скобки означают вы- числение целой части соответствующего выражения. Тогда условие (2) может быть записано в виде

10

г ЧВД-;. «)

ri L - J в

ти.

где g - контрольное основание, а О

пороговая константа.

Величины k(i 1,2,..., п) могут

быть вычислены заранее и записаны

соответствующим образом в блок памя- . Обозначают ™ - Т

;.( r« J

через Z и рассматривают, как исправляются ошибки в сообщениях, представленных в ВУ-коде. Пусть ошибка в условном остатке по i-му основанию, тогда вычисляют величину

1; Z-P; .

Исходя из полученного результата, может быть вычислена величина поправки к неправильному условному остатку

35 Ло( J R l l I J Р1

40

45

50

Р;

где .

Величины R и R , являются достаточно большими числами и поэтому для сокращения разрядности целесообразно использовать преобразование

4 {{Рг1„-Г« Ц.

U г(г,

при котором оба множителя меньше Р(- , т.е. становятся малоразрядными. Далее остается только скорректировать сЈ на и при этом получается правильный результат.

Важно отметить, что А может вычисляться для всех условных остатков, однако правильным оно будет лишь для одного искаженного остатка. Поэтому важно решить какой остаток правильный, а какой искаженный, т.е. определить место искажения. Для этого

можно обе части выражения (5) умножить на Pj j

ZP; Јi.

1 g

Если остаток по основанию Р искажен, то это неравенство вдаолняется. Таким образом, проводя такое сравнение, можно найти место ошибки.

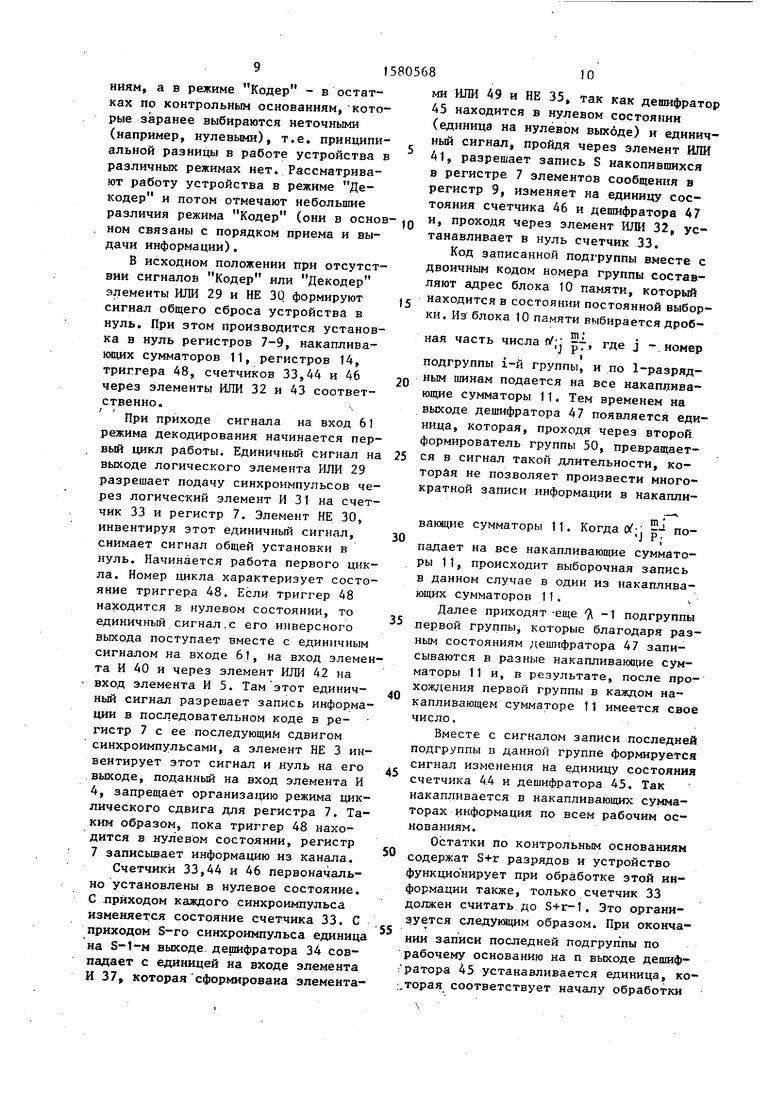

Для этого при разбиении исходного кода на группы первые групп получают как первые условные вычеты по основанию Р , вторые 7 групп - как вторые условные вычеты по основанию Р и так далее, т.е. каждые (i-I,2,. ...,п) Д групп рассматриваются как условные вычеты по основанию Р;. Таким образом, исходный код представляется как Д перемеживающихся условных слов (каналов) в остаточных классах по п групп в каждом. Для каждого из этих каналов (условных- слов) рассчитывается контрольный признак (Х -в(п+,). Полученные /Д контрольных признаков приформировываются к исходному коду. При этом ни структура, ни величина исходного кода не меняются. Тогда любая групповая ошибка крат- нрсти (-1)8+1, где S - число разрядов в условных группах, вызывает искажение не более S разрядов в одной из групп каждого или некоторых из каналов. Как показано, такая ошибка в каждом из каналов легко обнаруживается и исправляется.

.Обнаруживающие и исправляющие возможности кода определяются величиной g, поэтому для увеличения g надо либо увеличивать разрядность остатка по контрольному основанию, либо использовать составные контрольные основания, например, малоразрядных чисел.

В предлагаемом устройстве выбраны два контрольных основания

ё- ргт-ттнгРегистр 9 предназначен для приема подгрупп-остатков по рабочим и по контрольным основаниям, а регистр 8 Только для приема двух старших разрядов подгрупп-остатков .по контрольным основаниям

Блок 10 памяти служит для табличного расчета дробной части произведения числа р(; - остатка по какомуml

либо основанию на константу . Выборка дробной части 1-го произведения происходит по четырехразрядному адресу, формируемому счетчиком 44 импульсов.

Накапливающие сумматоры 11, управляясь группой 50 формирователей, по очереди принимают каждую -ю дробную

часть произведения о(; pf и формируют

сумму

15

п+г

Т ы- Э-1 Ъ

При этом накапливается только дробная часть суммы

тг

.

;

р.

Регистры 14 предназначены для при- ема L после формирования сумм и содержат по 1 разрядов.

Группа коммутаторов 15 предназначена для поочередного разрешения каждому из сформированных Z посту- пить на 1-разрядный умножитель 17, который вычисляет произведение в режиме Декодер и ,,, F, где PKJ и Р соответственно первое и второе контрольные основания, в ре- жиме Кодер. Блок 18 сравнения выполняет функции сравнения двух чисел s дробной части произведения t с

константой --, и его знаковый разряд

Ь

является выходным сигналом этого элемента.

Устройство может работать в режимах Кодер и Декодер. Режим Кодер предназначен для формирования из информации кода условных вычетов - ВУ-кода, т.е. вычисления остатков по контрольным основаниям и передачи их вместе с информацией потребителю. Режим Декодер предназначен для декодирования информации, исправления ошибок и выдачи только информационной части сообщения, т.е. остатков только по рабочим основаниям. В каждом из режимов можно четко выделить два цикла работы.

Устройство работает следующим образом.

В режиме Декодер исправляются ошибки в остатках по рабочим основа

915

ниям, а в режиме Кодер - в остатках по контрольным основаниям, которые заранее выбираются неточными (например, нулевыми), т.е. принципиальной разницы в работе устройства в различных режимах нет. Рассматривают работу устройства в режиме Декодер и потом отмечают небольшие различия режима Кодер (они в основном связаны с порядком приема и выдачи информации).

В исходном положении при отсутствии сигналов Кодер или Декодер элементы ИЛИ 29 и НЕ 30 формируют сигнал общего сброса устройства в нуль. При этом производится установка в нуль регистров 7-9, накапливающих сумматоров 11, регистров 14, триггера 48, счетчиков 33,44 и 46 через элементы ИЛИ 32 и 43 соответ

ственно.

При приходе сигнала на вход 61 режима декодирования начинается первый цикл работы. Единичный сигнал на выходе логического элемента ИЛИ 29 разрешает подачу синхроимпульсов через логический элемент И 31 на счетчик 33 и регистр 7. Элемент НЕ 30, инвентируя этот единичный сигнал, снимает сигнал общей установки в нуль. Начинается работа первого цикла. Номер цикла характеризует состояние триггера 48. Если триггер 48 находится в нулевом состоянии, то единичный сигнал с его инверсного выхода поступает вместе с единичным сигналом на входе 61, на вход элемента И 40 и через элемент ИЛИ 42 на вход элемента И 5. Там этот единичный сигнал разрешает запись информации в последовательном коде в регистр 7 с ее последующим сдвигом синхроимпульсами, а элемент НЕ 3 ин- вентирует этот сигнал и нуль на его выходе, поданный на вход элемента И 4, запрещает организацию режима циклического сдвига для регистра 7. Таким образом, пока триггер 48 находится в нулевом состоянии, регистр 7 записывает информацию из канала.

Счетчики 33,44 и 46 первоначально установлены в нулевое состояние. С приходом каждого синхроимпульса изменяется состояние счетчика 33. С приходом S-ro синхроимпульса единица на S-1-м выходе дешифратора 34 совпадает с единицей на входе элемента

И 37, которая сформирована элемента- ,торая соответствует началу обработки

568

10

ми ИЛИ 49 и НЕ 35, так как дешифратор 45 находится в нулевом состоянии (единица на нулевом выходе) и единичный сигнал, пройдя через элемент ИЛИ 41, разрешает запись S накопившихся в регистре 7 элементов сообщения в регистр 9, изменяет на единицу состояния счетчика 46 и дешифратора 47 и, проходя через элемент ИЛИ 32, устанавливает в нуль счетчик 33.

Код записанной подгруппы вместе с двоичным кодом номера группы составляют адрес блока 10 памяти, который находится в состоянии постоянной выборки. Из блока 10 памяти выбирается дроб. m г ная часть числа tf;j --, где j - номер

подгруппы 1-й группы, и по 1-разряд0

5

0

5

0

5

0

ным шинам подается на все накапливающие сумматоры 11. Тем временем на выходе дешифратора 47 появляется единица, которая, проходя через второй формирователь группы 50, превращается в сигнал такой длительности, которая не позволяет произвести многократной записи информации в накапливающие сумматоры 11. Когда И1; J попадает на все накапливающие сумматоры 11, происходит выборочная запись в данном случае в один из накапливающих сумматоров 11.1

Далее приходят еще А -1 подгруппы первой группы, которые благодаря разным состояниям дешифратора 47 записываются в разные накапливающие сумматоры 11 и, в результате, после прохождения первой группы в каждом накапливающем сумматоре 11 имеется свое число.

Вместе с сигналом записи последней подгруппы в данной группе формируется сигнал изменения на единицу состояния счетчика 44 и дешифратора 45. Так накапливается в накапливающих сумматорах информация по всем рабочим основаниям.

Остатки по контрольным основаниям содержат S+r разрядов и устройство функционирует при обработке этой информации также, только счетчик 33 должен считать до S+r-1, Это организуется следующим образом. При окончании записи последней подгруппы по рабочему основанию на п выходе дешифратора 45 устанавливается единица, ко

S+r-разрядных подгрупп. Эта единица, проходя через элементы ИЛИ 49 и НЕ 35, запрещает появление единицы на выходе элемента И 37 и после накопления S разрядов информации. Сигнал с выхода элемента ИЛИ 49, поданный на .вход элемента И 38, дает возможность счетчику 33 считать до S+r+1, а потом единица, полученная на выходе дешиф- ратора 34, повторяет функции единицы на выходе элемента И 37, но, кроме этого, еще разрешает запись т старших разрядов остатка по контрольному основанию в регистр 8. При этом после такого такта в регистрах 8 и 9 находится остаток по контрольному основанию.

Таким образом, обрабатывается две группы, в результате чего, в накапли- вающих сумматорах 11 к уже полученным

«С- , Ш|„

суммам (. где n число рабо . J г 1 1

чих оснований, добавится по два чис ae4jif

. После

записи в

П

регистры 8 и 9, последней группы обк л на нулевом выходе дешифратора 47 устанавливается единица. Она передается на счетный вход счетчика 44 и единица появляется на (п+2)-м выходе дешифратора 45. Это признак конца формирования Z. Он через элемент ИЛИ 43 устанавливает в нуль счетчик 44, записывает сформированные Z , - Za в соответствующие регистры 14 и устанавливает в единицу триггер 48, переводя устройство во второй цикл.

Так как сигнал на входе 61 продолжается еще столько же, то синхроимпульсы поступают в устройство, однако нулевой сигнал на инверсном выходе триггера 48, поступая на входы элементов И 39 и 40, приводит к появлению нулей на их выходах, которые поступают на входы элемента ИЛИ 42. На выходе последнего устанавливается нуль, который запрещает прием информации из канала, попадая на один из входов элемента И 5 и, инвертируясь элементом НЕ 3, попадает на вход элемента И 4. Таким образом разрешается циклический сдвиг информации в регистре 7. Приходящие синхроимпульсы, циклически сдвигая информацию, имитируют повторное поступление накопленной информации, при этом устройство работает таким же образом, как в предыдущем цикле, однако еди

Q

Q

5

0

нич ный сигнал с выхода триггера 48, поступая на входы коммутатора 13, разрешает передачу подгрупп на входы блока 19 памяти и коммутатор 21. Эти t подгруппы передаются по S-разрядной шине, так как в режиме Декодер на выходе устройства нужны только остатки по рабочим основаниям, а в режиме Кодер, когда надо передавать остатки по контрольным основаниям, они заранее выбираются искаженными (потом исправляются), а значит, их старшие разряды можно не передавать вообще.

Так как все счетчики и дешифраторы работают так же,как и в первом цикле, то с приходом каждой новой подгруппы изменяется состояние счетчика 46. Сигналы с выходов дешифратора 47, по очереди поступая на группу коммутаторов 15, разрешают прохождение записанных в регистрах 14 Z - Z/ через элемент ИЛИ 16, которые по сути объединяют каналов, на вход умножителя 17.

Последний умножает Z на Р (основание, остатком по которому является данная подгруппа), которое выбирается из блока 57 памяти по адресу, формируемому счетчиком 44, так как подгруппы каждой группы - остатки по одному и тому же основанию, В это же время выбирается из блока 58 памяти

Р обратный ход числа --, где

&

В случае если по основанию Pj подгруппе имеется ошибка,

часть числа

ZJP;

к,- j-й то дробная

р;

становится меньше

Li

g

поэтому разность этих чисел вычисляется сравнивающим блоком 18, ив случае появления в знаковом разряде этого блока 18 единицы делается вывод о том, что

Z;P g J

i - tzjp;l

ЈziP-, 1 - целая часть числа,

ошибка находится в j-и подоснованию Р и ее надо исгде

а значит, группе по правлять.

Исправленное значение вычисляется в блоке 19 памяти для каждой подгруппы, однако оно имеет правильное значение только в том случае, если эта подгруппа ошибочна. Таким образом перед коммутаторами 21-23 имеют подгруппу, пришедшую из канала, исправленную подгруппу и сигнал о наличии или отсутствии ошибки в данной подгруппе. Если ошибка есть, то через коммутатор 22 пропущена исправленная подгруппа,а на входе коммутатора 21, .на который подается подгруппа, принятая из канала, подается сигнал ошибки, инвентированный элементом НЕ 20 и запрещающий дальнейшую передачу этой неправильной подгруппы. Таким образом после объединения - группы ИЛИ 24 на вход регистра 25 попадают правильные или исправленные подгруппы. В выходной регистр 25 эта информация записывается по сигналу записи который формируется как задержанный элементом 59 сигнал записей в накапливающие сумматоры 11, объединенные на элементе ИЛИ 56. Величина задержки элемента 59 при этом выбирается такой, чтобы записать информацию в регистр 25 в тот момент, когда она устанавливается на его входе. Из регистра 25 выдается информация. При этом, если необходимо выдавать остатки по рабочим основаниям, т.е. четырехразрядные подгруппы, го используется (5-1)-й выход регистра 25 Единичный сигнал об обработке остатков по контрольным основаниям можно получить на выходе элемента ИЛИ 49. Для получения сигнала об обработке остатков по рабочим основаниям этот сигнал надо пр оинвертировать. Это делается на элементе НЕ 35, На вход логического элемента И 27 подается сигнал с (S-1)-ro выхода регистра 25 и выхода элемента НЕ 35, чем обеспечивают выдачу остатков по контрольным основаниям через элемент ИЛИ 28, выполняющего объединяющие функции в каналах.

В режиме Декодер выдавать остатки по контрольным основаниям нельзя, поэтому после выдачи остатков по рабочим основаниям на вход элемента И-НЕ 51 подается единичный сигнал с элемента ИЛИ 49 и сигнал с входа 61. При совпадении единиц на входах элемента И-НЕ 51 на его выходе устанавливается нуль, который, проходя через элемент ИЛИ 54, запрещает выдачу синхроимпульсов на регистр 25. Элемент 53 задержки обеспечивает возможность пройти последней вьщаваемой подгруппе в канал, после чего подача

0

5

0

5

0

5

0

5

0

5

синхроимпульсов на регистр 25 прекращается.

Второй цикл заканчивается по окончании сигнала на входе 61. В режиме Кодер работа устройства отличается тем, что по сигналу на входе 12 на вход элемента И 52 в первом цикле работы информация записывается в регистр 7 до тех пор, пока не сформируется на выходе элемента НЕ 35 единичный сигнал, т.е. пока накапливаются остатки по рабочим основаниям. Дальше регистр 7 устанавливается в режим циклического сдвига, а так как в старших разрядах регистра 7 записаны нули, то при накоплении суммы вместо остатков по контрольным основаниям записываются нули. В режиме Кодер из блока 57 памяти выбираются не основания Р| , а произведения оснований РЛи Рл+2, которые выбираются когда сформирован адрес п+1 или п+2 на входе этого блока памяти.

Все информационные разряды воспринимаются как правильные, а неправильные контрольные направляются так же как и в режиме Декодер, однако г старших разряда остатка по контрольным основаниям передаются через коммутатор 23 на вход регистра 25, сформированные контрольные разряды выдаются в канал с выхода регистра 25, через элемент И 26 и ИЛИ 28.

В режиме Кодер синхроимпульсы поступают на регистр 25 до выдачи всего сообщения, т.е. на входе элемента И 52 сигнал Кодер и единица с прямого выхода триггера 48 (во втором цикле работы) вызывают появление единицы на его выходе, т.е. на входе элемента ИЛИ 54 установлена единица, которая, передаваясь на вход элемента И 55, разрешает прохождение синхроимпульсов на регистр 25, Работа в режиме Кодер заканчивается с окончанием сигнала на входе 12.

Устройство обеспечивает повышение вероятности обнаружения и исправления ошибок за счет того, что позволяет обнаруживать и исправлять произвольно размещаемые в пределах кодовой комбинации ошибки кратности и менее, в то время как в известном устройстве невозможны обнаружения и коррекция плавающих ошибок кратностью более одного разряда. Расширение функциональных возможностей связано с введенной в уст

ройство, наряду с функцией декодирования, функцией кодирования исходных кодовых комбинаций, в то время как в известном устройстве реализована только функция декодирования.

Формула изобретения

Устройство для обнаружения и исправления ошибок в кодовой последовательности, содержащее первый элемент И, первый вход которого является тактовым входом устройства, а выход соединен с информационным входом перво- го счетчика импульсов, выходы которого подключены к входам первого дешифратора, первый1 вход первого элемента ИЛИ объединен с входом первого элемента задержки, выход которого под- ключей к информационному входу второго счетчика импульсов, выходы которого подключены к входам второго дешифратора, выходы которого подключены соответственно к первым входам коммутаторов группы, выход второго элемента ИЛИ подключен к счетному входу триггера, прямой выход которого соединен с первым входом второго элемента И, первый регистр, выходы первого блока памяти подключены к первым информационным входам накапливающих сумматоров группы, группу регистров, выходы которых подключены к вторым входам коммутаторов группы, выходы первого коммутатора подключены к первым входам второго блока памяти, выходы третьего и четвертого блоков памяти подключены соответственно к первым входам умножителя и блока ера- внения, выход которого подключен к входу первого элемента НЕ, второй и третий элементы задержки, второй - четвертый коммутаторы, третий элемент И, отличающееся тем, что с целью расширения функциональных возможностей устройства за счет обеспечения режима кодирования информации и повышения помехоустойчивости за счет исправления плавающей групповой ошибки, в него введены второй - четвертый элементы НЕ, элемент И-НЕ, второй - четвертый регистры, группа формирователей сигнала, третий счетчик импульсов, третий дешифратор, группа элементов ИЛИ, четвертый - одиннадцатый элементы И, третий - одиннадцатый элементы ИЛИ, первьй вход третьего элемента И является ин

0

5

5 до

0

35

45

50

55

формационным входом устройства, а выход подключен к первому входу четвертого элемента ИЛИ, выход которого подключен к информационному входу первого регистра, первый и вторые информационные выходы которого подключены соответственно к информационным входам второго и третьего регистров, выходы которых подключены к информационным входам первого блока памяти, выход третьего элемента ИЛИ подключен непосредственно к второму входу первого элемента И и через третий элемент НЕ к входам сброса первого - третьего регистров, первому входу второго элемента ИЛИ, второму входу первого элемента ИЛИ, входам сброса накапливающих сумматоров группы и регистров группы, входам сброса второго счетчика и триггера инверсный выход которого подключен к первым входам седьмого и восьмого элементов И, выходы которых подключены к первому и второму входам шестого элемента ИЛИ, выход которого подключен непосредственно к второму входу третьего элемента И и через второй элемент НЕ к первому входу четвертого элемента И, второй вход и выход которого подключены соответственно к выходу старшего разряда первого регистра и второму входу четвертого элемента И, выход первого элемента ИЛИ соединен с входом сброса первого счетчика импульсов, первьй вход девятого элемента И объединен с входом сдвига первого регистра и подключен к выходу первого элемента И, выходы первого дешифратора подключены соответственно к первым входам пятого и шестого элементов И, выходы каждого накапливающего сумматора группы подключены к вторым информационным входам одноименного сумматора и информационным входам соответствующего регистра группы, входы записи всех регистров груп- пы объединены с входом сброса третьего счетчика импульсов и подключены к выходу второго элемента ИЛИ, нулевой выход второго дешифратора соединен с информационным входом третьего счетчика импульсов, выходы которого . подключены к адресным входам первого - четвертого блоков памяти и входам третьего дешифратора, первый, второй и третий выходы которого подключены соответственно к второму входу второго элемента ИЛИ, и первому и

второму входам седьмого элемента ИЛИ, выход которого подключен непосредственно к второму входу шестого элемента И, через второй элемент задержки к первым входам элемента И-НЕ и десятого элемента И, и через четвертый элемент НЕ к вторым входам пятого и седьмого элементов И и первому входу одиннадцатого элемента И, выход пя-. того элемента И подключен к первому входу пятого элемента ИЛИ, выход шестого элемента И подключен к входу записи второго регистра и второму входу пятого элемента ИЛИ, выход которо- го подключен к входу первого элемента задержки и входу записи третьего регистра, входы группы формирователей сигналов подключены к соответствующим выходам второго дешифратора, выходы группы формирователей сигналов подключены к входам записи соответствующих накапливающих сумматоров группы и входам восьмого элемента ИЛИ, выход которого через третий элемент задержки подключен к входу записи четвертого регистра, первый вход первого коммутатора соединен с выходами третьего регистра, второй вход первого коммутатора объединен с вторым входом элемента И-НЕ и подключен к прямому выходу триггера, выходы первого коммутатора подключены к первым входам второго коммутатора и первым информационным входам второго блока памяти, выходы элемента И-НЕ и второго элемента И подключены соответственно к первому и второму входам десятого элемента ИЛИ, выход которого .

5

5

0

5

подключен к второму входу девятого элемента И, выход которого подключен к входу сдвига четвертого регистра, выходы коммутаторов группы подключены к входам девятого элемента ИЛИ, выход которого соединен с вторым входом умножителя, выходы которого подключены к второму входу блока сравнения и к вторым информационным входам второго блока памяти, выходы которого подключены к первым входам четвертого и третьего коммутаторов, вторые входы и выходы второго и третьего коммутаторов подключены соответственно с выходам первого элемента НЕ и блока сравнения и первым и вторым входам элементов ИЛИ группы, выходы которых и выходы четвертого коммутатора подключены соответственно к первым и вторым информационным входам четвертого регистра, первый и второй выходы которого подключены соответственно к вторым входам десятого и одиннадцатого элементов И, выходы которых подключены соответственно к первому и второму входам одиннадцатого элемента ИЛИ, выход которого является выходом устройства, второй вход второго и третий вход седьмого элементов И, четвертого коммутатора и первый вход третьего элемента ИЛИ объединены и являются входом режима кодирования, вторые входы третьего элемента ИЛИ и восьмого элемента И объединены с третьим входом элемента И-НЕ и являются входом режима декодирования устройства,

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-10-21—Подача