-1 Изобретение относится к технике связи и ножет быть использовало как устройство преобразования цифрового сигнала линейного тракта, Известно устройство для записи и воспроизведения цифрового сигнала, содержащее три элемента И, первые входы которых объединены, а вторые входы элементов И являются соответственно первым,вторым и входами устройства, а выходы элементов И подключены ко входам элемента ИЛИ, выход которого непосредственно и через линию задержки подключен ко входам выходного Т-триггера tiL Однако данное устройство для записи и воспроизведения цифрового сиг нала обладает низкой помехоустойчивостью. Наиболее близким к изобретению техническим решением является устрой ство для преобразования кода цифрового сигнала, содержащее ЛК-триггер, 0-вход которого является входом устройства и через инвертор подключен к К-входу К-триггера, С-вход которого явлйется вторым входом устройства а инверсный выход ЭК-триггера подключен к первому входу первого элемента И-НЕ, выход которого подключен к первому входу элемента НБ-ИШ, к второму входу которого подключен выход второго элемента И-НЕ, к перво му входу которого подключен выход тр тьего элемента И-НЕ, а выход элемента НЕ-ШШ подключен к С-Входу выход ного D-триггера, инверсный выход которого подключен к D-входу выходного D-триггера,. а также второй и третий ЗК-триггеры, четвертый и пятый элементы И-НЕ и второй и третий инверто ры, при этом выход второго элемента И-НЕ через второй инвертор подключен к С-входу третьего ЗК-триггера, 3 и К-входы которого объединены, а к R-входу третьего ЗК-триггера подключен выход четвертого элемента И-НЕ, первый вход которого объединен с пер вым входом второго элемента И-НЕ и С-входом второго ОК-триггера и является третьим входом устройства, а выход первого инвертора подкхвочен к второму входу первого элемента И-НЕ и первому входу третьего элемента И-HEs, к второму и третьему входам которого подключены соответственно прямые выходы второго и третьего 0 ЭК-триггеров, при этом выход третьего элемента И-НЕ через третий инверjTop подключен к первому вхрду пятого элемента И-НЕ, к третьему входу торого и третьему вхоДу второго-элеТ ента И подключен прямой выход первого ЗК-триггера, С-вход которого объединен с третьим входом первого элемента И-НЕ и третьим входом пятого элемента И-НЕ, выход которого под ключей к R,-входу второго ЭК-триггера, к 3 и К-входам которого и второму входу четвертого элемента И-НЕ подключен инверсный выход первого ЭКтриггера 23. Однако известное устройство дпя преобразования кода цифрового сигнала обладает низкой помехоустойчивостью. Цель изобретения - повьшение помехоустойчивости. Для достижения цели в устройство для преобразования кода цифрового сигнала, содержащее ЗК-тригге, Э вход которого является входом устройства и через инвертор подключен к К-входу JK-триггера, С-вход которого является вторым входом устройства, а инверсный выход DK-триггера подключен к первому входу первого элемента И-НЕ, выход которого подключен к первому входу элемента НЕ-ИЛИ, к второму входу-которого подключен выход второго элемента И-НЕ, к первому входу которого подключен выход третьего элемента И-НЕ, а выход элемента НЕ-ИЛИ подключен к С-входу выходного D -триггера, инверсный выход которого подключен кГ -входу выходного D -триггера, введены первый, второй и третийD-триггеры, элемент ШШ-НЕ, элемент И, элемент ИЛИ и Т-триггер, к С-входу и 5-входу которого подключены соответственно выход третьего элемента И-НЕ и выход элемента И, к первому входу которого и первому входу элемента ИЛИ-НЕ подключен прямой выход третьего D-триггера, а выход Т-триггера подключен к первому входу элемента ИЛИ, выход которого подключен к вторсжу входу второго элемента И-НЕ, а второй вход элемента ИЛИ объединен с входом инвертора, к Л-входу первого D -триггера и второму входу элемента ИЛИ-НЕ подклаочен прямой выход ЗК-триггера, С-вход которого объединен с С-входом второго B-rTpHr

гера, с третьим входом элемента ИЛИНЕ первым входом третьего элемента И-НЕ и вторым входом элемента И, к третьему входу которого подключен инверсный выход первого Г-триггера, С-вход которого объединен с С-входом третьего D-триггера и является третьим входом устройства, а прямой выход первого)-триггера подключен к второму входу третьего элемента ч И-НЕ Ир-входу второго D-триггера, прямой вькод которого подключен к р-входу третьего В-триггера, третье-т иу входу третьего эпемента ИПИ-НЕ и четвертому входу элемента ИЛИ-НЕ выход которого подключен к вторсжу входу первого элемента И-НЕ.

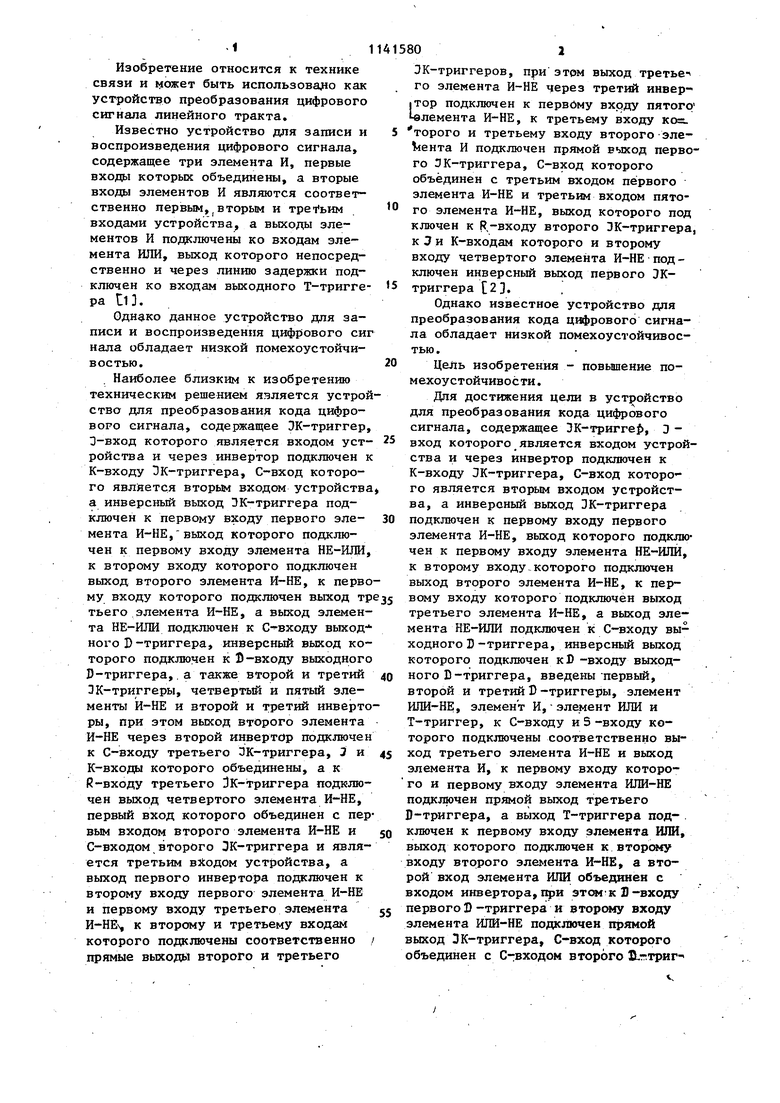

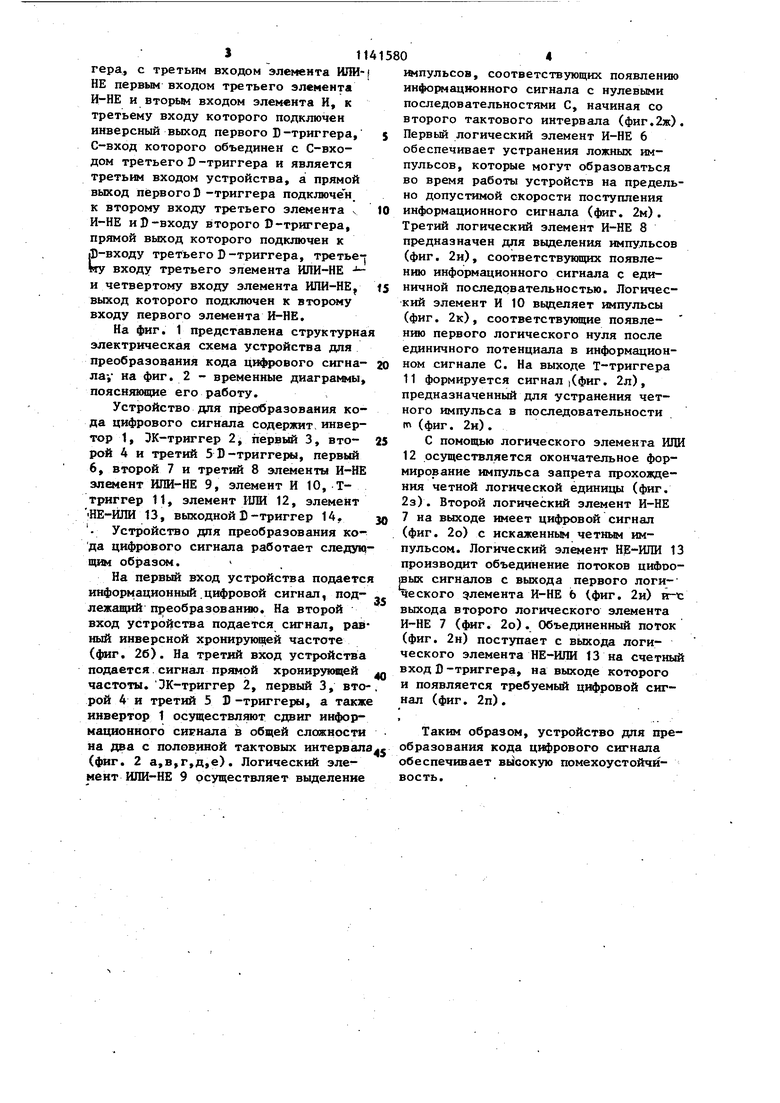

На фиг. 1 представлена структурна электрическая схема устройства для преобразования кода цифрового сигнала-, на фиг. 2 - временные диаграммы, поясняю1цие его работу.

Устройство для преобразования кода цифрового сигнала содержит,инвертор 1, ЭК-триггер 2, первый 3, второй 4 и третий 5 D-тригге1мл, первый 6, второй 7 и третий 8 элементы И-НЕ элемент ИЛИ-НЕ 9, элемент И 10, Ттриггер 11, элемент 1ШИ 12, элемент НЕ-ЙЛИ 13, выходной D-триггер 14, . Устройство дпя преобразования кода цифрового сигнала работает следующим образом.

На первый вход устройства подаетс информационный.цифровой сигнал, подлежащий преобразование. На второй вход устройства подается сигнал, равный инверсной хронирующей частоте (фиг. 26). На третий вход устройства подается.сигнал прямой хронирукщей частоты, ЗК-триггер 2, первый 3, вто рой 4 и третий 5 В -триггеры, а такж инвертор 1 осуществляют сдвиг информационного сигнала в общей сложности на два с половиной тактовых интервал (фиг, 2 а,в,г,д,е). Логический элемент ИЛИ-НЕ 9 осуществляет выделение

№1пульсов, соответствующих появлению информационного сигнала с нулевыми последовательностями С, начиная со второго тактового интервала (фиг.2ж). Первый логический элемент И-НЕ 6 обеспечивает устранения ложных импульсов, которые могут образоваться во время работы устройств на предельно допустимой скорости поступления информационного сигнала (фиг, 2м). Третий логический элемент И-НЕ 8 предназначен для выделения импульсов (фиг. 2и), соответствующих появлению информационного сигнала с единичной последовательностью. Логический элемент И 10 вьщеляет импульсы (фиг. 2к), соответствующие появлению первого логического нуля после единичного потенциала в информационном сигнале С. На выходе Т-триггера

11формируется сигнал |(фиг. 2л), предназначенный для устранения четного импульса в последовательности m (фиг. 2и),

С помощью логического элемента ИЛИ

12осуществляется окончатехшное формирование импульса запрета прохождения четной логической единицы (фиг. 2з). Второй логический элемент И-НЕ 7 на выходе имеет цифровой сигнал (фиг. 2о) с искаженным четным импульсом. Логический элемент НЕ-ИЛИ 13 производит объединение потоков цифоо1ВЫХ сигналов с выхода первого логического элемента И-НЕ 6 (фиг. 2и) и-с выхода второго логического элемента И-НЕ 7 (фиг. 2о). Объединенный поток (фиг. 2н) поступает с выхода логического элемента НЕ-ШШ 13 на счетный вход D-триггера, на выходе которого

и появляется требуемый цифровой сигнал (фиг. 2п),

Таким образом, устройство для преобразования кода цифрового сигнала обеспечивает вЕлсокую помехоустойчивость.

Фиг:1

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Устройство для преобразования цифрового сигнала | 1982 |

|

SU1109925A1 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| Устройство для определения достоверности информации | 1983 |

|

SU1092742A1 |

| Устройство цифрового декодирования информации | 1984 |

|

SU1200427A1 |

| РЕГУЛЯТОР ТЕМПЕРАТУРЫ | 2010 |

|

RU2431177C1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Стартстопное приемное устройство | 1983 |

|

SU1141583A1 |

| Устройство для управления однофазным асинхронным электродвигателем | 1981 |

|

SU1023612A1 |

| Многоканальный преобразователь кода в напряжение | 1983 |

|

SU1163475A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА ЦИФРОВОГО СИГНАЛА, содержащее JK-триггер, 3-вход которого является входом устройства и через инвертор подключен к К-входу,ЗК-триггера, С-вход которого является вторым входом устройства,.а инверсный выход ЗК-триггера подключен к первому входу первого элемента И-НЕ выход которого подключен к первому входу элемента НЕ-ИЛИ, ic второму входу которого подключен выход второго элемента И-НЕ, к первому входу которого подключен выход третьего элемент И-НЕ, а выход элемента НЕИЖ подключен к С-входу выходного , D-триггера, инверсный выход которого подключен к В-входу выходного D-триггера, отличающееся тем, что с целью повышения помехоустойчивости, в него введены первый, второй и третий В-триггеры, элемент ИЛИ-НЕ, элемент И, элемент ИЛИ и Т-триггер, к С-входу и S-входу которого подключены соответственно выход третьего элемента И-НЕ и выход элемента И, fc первому.входу которого и первому входу элемента ИЛИ-НЕ подключен прямой выход третьего D-триггера, а выход Т-триггера подключен к первому входу элемента ИЛИ, выход которого подключен к второму входу второго элемента И-НЕ, а второй вход элемента ИЛИ объединен с входом инвертора, при этом к Г -входу первого D-триггера и второму входу элемента ИЛИ-НЕ подключен прямой выход DKтриггера,С-вход которого объединен с С-входом второго D-триггера, с третьим входом элемента ШШ-НЕ, первым входом третьего элемента И-НЕ и вторым входом элемента И, к третьему входу которого подключен инверсный выход первого Б-триггера, С-вход которого объединен с С-входом третьего D-триггера и является третьим входом устройства, а прямой выход первого 5 -триггера подключен к второму СП входу третьего элемента И-НЕ иС 00 ходу второго D-триггера,.прямой которогоподключен к В-входу третьего D -триггера, третьему входу третьего элемента И-НЕ и четвертому входу элемента ИЛИ-НЕ, выход которого подключен к второму входу первого элемента И-НЕ.

njijijijarurnj

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3414894, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ акустической дефектоскопии изделий | 1987 |

|

SU1578635A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-02-23—Публикация

1983-12-30—Подача