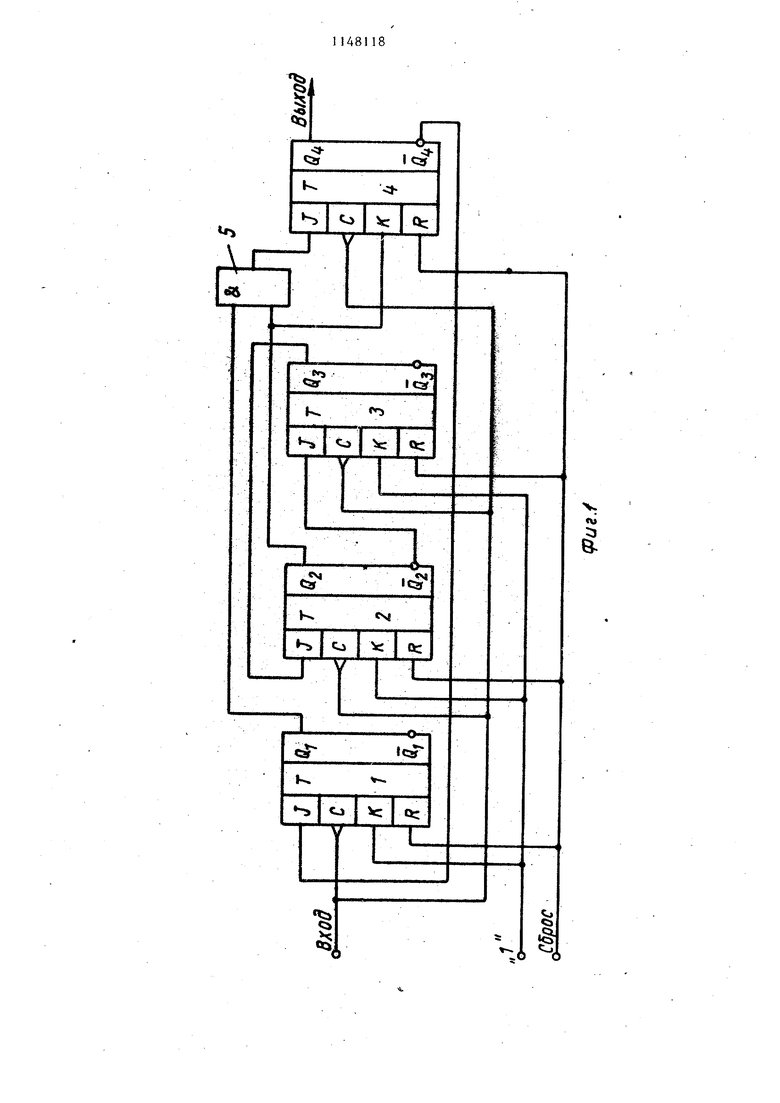

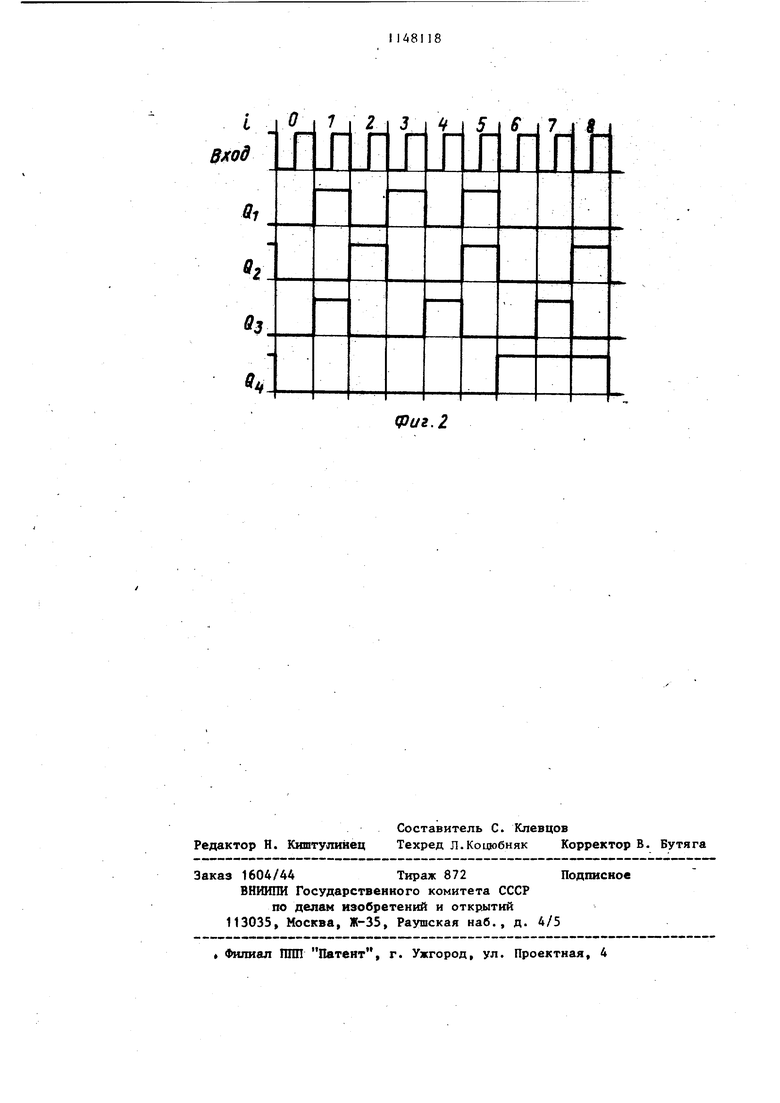

00 1 Изобретение относится к цифрово технике и может .быть использовано в различной цифровой аппаратуре, например, в цифровых синтезаторах частоты. Известен делитель частоты на 9, содержащий пять асинхронных RS-триггеров (бистабильных ячеек), десять многовходовых элементов сов падения и инвертор ГО« Недостатком известного делителя является большое количество элемен тов и цепей. Кроме того, этот дели тель является несинхронным. Наиболее близким к предпагаемому является синхронньй делитель ча тоты на 9 на четырех 3К- триггерах работающий в коде 8-4-2-1, содер.жащий четыре 1К-триггера и элемен И, счетные входы всех ЭК триггеро соединены между собой и образуют . тактовый вход устройства, входы R всех DК-триггеров соединены между собой и- образуют вход Сброс, пер вый и второй входы первого элемента И соединены с прямыми выходами соответственно первого и второго ЭК-триггеров, на вход К первого JK-триггера поступает сигнал логической единицы, вход J JK-триггеров соединен с инверсньАг выходом четвертого JK-триггера, прямой вы ход которого является выходом устройства , входы второго элемента И соединены с прямыми выходами перво го, второго и третьего ЛК -триггеров , а выход - с входом 3 четверто го Л1 -триггера 2. Из схемы получают логические уравнения для D и К входов JK -три геров Лд- Di .1в А; Jc АВ; Jj, AB Кд - Kg Ai KC АВ; Kj Вводят более общие обозначения логических переменных C-Qj, D Л - Q, Тогда JI --AQ4i 2 :б 3ii Ээ Зс Q,Q, i Qi-QzQji К, Кд 1 , У. Kg Qj 1 А ft К, - Ке Q,Qi;.K4 KB 1. Недостатками известного делител являются большое количество элемен топ н цепей, низкая надежность и высокая потребляемая мощность. Цель и:зобрвтения - упрощение стро1 и;тпа. 8 . 1 , Поставленная цель достигается тем, что в синхронном делителе частоты на 9 на ЗК -триггерах, содержащем четыре :Jk -триггера и элемент И, счетные входы всех JK -триггеров соединены с тактовым входом устройства, входы R всех лК -триггеров соединены с входом Сброс устройства, а первый и второй входы элемента И соединены с прямыми выходами соответственно первого и второго ЭК -триггеров, причем вход К первого ЭК -триггера соединен с шиной логической единицы, вход J первого JK -триггера соединен с инверсным выходом четвертого . ЭК-триггера, прямой выход которого является выходом устройства, входы К второго и третьего ЭК -триггеров соединены с входом К первого ЭК-триггера, вход Э второго J -триггера соединен с прямым выходом третьего ЭК-триггера, вход Э третьего ЭК-триггера соединен с инверсным второго Эк -триггера, а выход элемента И соединен с входом Э.четвертого ЗК -триггера, вход К которого соединен с прямым выходом второго ЛК -триггера. При такой схеме соединения элементов логические уравнения для J и К входов всех триггеров следующие:Л Qj -, Л4 Q.a,-, К, К KI На фиг. I представлена функциональ ная схема синхронного делителя частоты на 9 на ЭК-триггерах, на фиг. 2 - диаграммы сигналов на прямых выходах Эк-триггеров синхронного делителя частоты на 9 на ЭК-триггерах. Синхронный делитель частоты на 9 на JK-триггерах содержит ЭК-триггеры 1-4 и элемент 5 И. На входы К первого, второго и третьего JK -триггеров подается потенциал логической единицы. Работа синхронного делителя частоты на 9 на ЭК-триггерах полностью описывается логическими уравне-. ниями для Л и К входов его триггеров, Этими же уравнениями определяется и схема соединения J и К входов с соответствующими выходйми со ткетствующих триггеров. . 3 По сигналу Сброс все 5к -триг геры делителя частоты на 9 устанав ливаются в нулевое состояние. На оснобании логических уравнений для J и К входов триггеров име ют х э j, 4 , К - ч V 1 1г - 1 1 1,Л., |,й., - 1, к, О. Поскольку эк -триггер при 3 и К О по последующему импульсу не изменяет«своего состояния, при Э 1 и К « 1 - пецрключается в противополоаяое состояние, при J 1 и К О - переключается в состояние логической единицы и при 3 О и К « 1 - переключае ся в состояние логического нуля, т по поступлении на вход схемы перво го импулЬса, первый итретий триггеры переключатся в состояние логи ческой единицы, а второй и четвертый триггеры не изменят своего сос тояния . В первом состоянии схемы при состояния выходов триггеров следующие (см. диаграммы на фиг,. 2 при i П„ Q,,- Q О, из - 1. G, « О. Состояния входов при этом изменяются и равны Л« Л« 3, 1 Ч 1 П J4 К, К, ГЧ К, -- Г1 К О. По второму вxoднoм импульсу схема перблодит во второе свое состояние (см. диаграммы на фиг. 2 при i 2), в котором QI Q , Qj ОЧ (L 3, г J, а О, , К, К, rj К, 1, К О. По третьему входному импульсу состояние входов и выходов равны (см. диаграммы на фиг. 2 при i 3) q ГЧ QJ Q, |.«|| Рассматривая и далее работу схемы таким же образом, получают все значения входов и выходов при каждом i (см. диаграммы на фиг. 2). Из сравнения логических уравнений для Э и К входов прототипа и предлагаемого синхронного делителя частоты на 9 на JK-триггерах видно, что предлагаемое устройство имеет меньшее количество элементов и цепей, что положительно сказывается на надежности и потребляемой мощности устройства.

V. (u

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Делитель частоты следования импульсов | 1981 |

|

SU980292A1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Счетчик импульсов | 1977 |

|

SU784003A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ НА 9 НА ЗК -ТРИГГЕРАХ, содержащий четыре ЗК-триггера и элемент И, счетные входы всех ЗК -триггеров , соединены с тактовым входом устройства, входы R всех О К-триггеров соединены с входом Сброс устройст ва, а первый и второй входы элемен:та И соединены с прямыми выходами соответственно первого и второго ЭК-триггеров, причем вход К. первого КК-триггера соединен с шиной логической единицы, вход J первого ЗК-триггера соединен с инверсным выходом четвертого JK -триггера, прямой выход которого является выходом устройства, отличающийся тем, что, с целью упрощения устройства, входы К второго и третьего I7K -триггеров соединены с входом К первого Jk -триггера, вход Э второго 3k -триггера соединен с прямым выходом третьего ЭК-триггера, вход J третьего Jk-триггера соединен с инвepcньiм выходом второго JK -триггера, а выход элемента И соединен с входом J чет(Л вертого 3k -триггера, вход К которого соединен с прямым выходом второго JX -триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Делитель частоты повторения импульсов | 1974 |

|

SU501483A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| Пер | |||

| с чешского | |||

| М., Связь, 1977 (прототир) | |||

Авторы

Даты

1985-03-30—Публикация

1983-09-28—Подача