2. Преобразователь по п.1, о тличающийся тем, что анализатор обработки кода выполнен на Die триггере, четырех ЗЭ - триггерах, двух элементах ИЛИ, элементе И и дешифраторе, первьй вход которого соединен с третьим входом анализатора отработки кода, второй ход - с четвертым входом анализатора отработ ки кода и с С - входом К - триггера, первый выход дешифратора - с первым входом первого элемента ИЛИ и прямым 5 входом JK -триггера, второй выход - с С - входом первого О -триггера и с прямым входом элемента И, инверсный вход которого подключен к выходу первого D -триггера и первому входу второгоэлемента ШШ, а выход - к С - входу второго О - триггера и к второму входу первого элемента ИЛИ, выход которого соединен с С - входами третьего и четвертого D - триггеров, ТЗ-и R входы которых соединены с первым входом анализатора обработки кода, а их выходы - соответственно с вторым и третьим входами второго элемента ИЛИ. выход которого подключен к Д входу CIK - триггера, инверсный вход которого соединен с D - и R - входами первого и второго U - триггеров и вторым входом анализатора отработки кода, R - вход ЗК - трип-ера - с пятым входом анализатора отработки кода, выход Jk- триггера - с первым выходом анализатора отработки кода, вторые выходы которого подключены к выходам D - триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Коммутатор для управления шаговым двигателем | 1990 |

|

SU1784944A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

Изобретение относится к вычисли тельной технике, в частности к преоб-разователям цифровой формы представления информации в аналоговую, и может быть использовано в устройствах 5 вывода электронных вычислительных машин.

Цель изобретения - повышение дос-i товерности отработки входного кода.

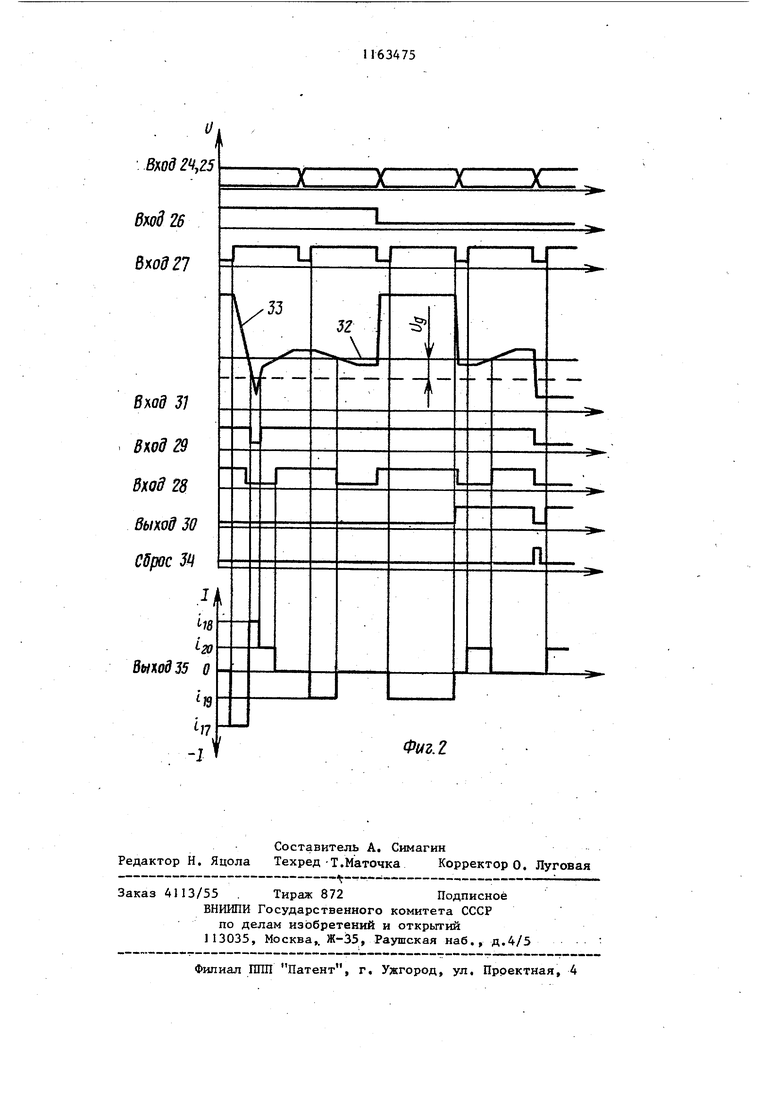

На фиг. 1 представлена с груктур-Ю ная схема преобразователя; на фиг.2 временные диаграммы изменения напряжений и токов в различных точках устройства в режиме отработки входного ,.кода.15

Преобразователь (фиг.1) содержит цифроаналоговый преобразователь 1, вход которого соединен с шиной кода напряжения, а выход соединен с вторым20 входом блока 2 сравнения, первый вход которого соединен с выходом выходного коммутатора 3, вторые входы которого соединены с выходами накопительных элементов А, выходы кото- 25 рых подключены к первым выходным шинам. Входы накопительных элементов 4 соединены с выходами входного коммутатора 5, вторые входы которого соединены с блоком 6 коррекции. Первые Bxor|Q ды входного 5 и выходного 3 коммутаторов подключены к шине кода номера . элемента.

Первый и второй входы анализатора 7 отработки кода (АОК ) подключены к соответствукмцим входам блока 2 сравнения, а третий и четвертьй входы АОК 7 соединены с шинами Запись, Обраш;ение и Сброс. Первый выход АОК 7 соединен с второй выходной шиной индикации, а второй - с входом блока 6 коррекции. Входы управления коммутаторов 3 и 5 соединены с шиной Код номера элемента.

Анал изатор 7 отработки кода содержит стробируемый дешифратор 8, ин-. формационный вход которого соединен с третьим входом АОК 7 и шиной Запись, стробирукхций V - вход дешифратора 8 соединен с четвертым входом АОК 7 и шиной Обращение и инверсным С- входом ЗК - триггера 9.

Первый выход дешифратора 8 соединен с прямым входом 5 - триггера 9 и с первым входом первого элемента ШШ 10. Второй вьпсод дешифратора 8 соединен с С-входом первого О триггера 11 и с прямым входом элемента И 12, инверсный вход которого со-единен. с выходом первого Л -триггера 1, а выход - с С-входом второго о -триггера 13 и с вторым входом первого элемента ИЛИ 10. Выход элемента ИЛИ 10 соединен с входами третьего и четвертого D -триггеров 14 и 15. О -вход и инверсный R вход D -триггера 14 и инверсный D вход и R -вход D -триггера 15 объединены между собой и соединены с первым входом АОК 7. Инверсный 5 вход ЗК -триггера 9, D - вход и инверсный R -вход И -тркггера 11 и инверсный D-вход иК-вход D-триггера 13 объединены и соединены с входньм кодом АОК 7. Первый и второй входы АОК 7 соединены соответственно с первым и вторым входами блока 2 сра нения. Выходы триггеров 11, 14 и 15 через второй элемент ИЛИ 16 соединены с 3 входом триггера 9, выход которого соединен с первым АОК 7 с выходом с шиной индикации. Выходы триггеров 11 - 15 являются вторыми выходами АОК 7 и соединены с входами блока 6 коррекции. R -вход ЗК-триггера 9 соединен с шиной Сброс. Блок 6 коррекции может быть выпо нен, например, на четьфех управляемых генераторах тока, два О 7 и 18) из которых вырабатывают втекающий ток, а другие (19 и 20 вытекающий ток. Блок 2 сравнения, может быть выполнен на компараторах 21 и 22, входы которых соединен с выходом узла 23 вычитания. Накопи тельные элементы содержат конденсатор и буферный усилитель. На фиг. 2 приняты следукщие обозначения: вход 24, 25 - входной код номера накопительного элемента, поступающий на входной и выходной коммутаторы 5 и 3; вход 26 - диагра ма управляющего сигнала на шине За пись, поступакяцего на третий вход АОК 7;вход27 - диаграмма тактового сигнала на шине Обращение, поступающего на четвертый вход АОК 7; вход 28 - диаграмма сигнала, поступ ющего на первьй вход АОК 7 с первог выхода блока 2 сравнения; вход 29 диаграмма сигнала, поступающего на второй вход АОК 7 с второго выхода блока 2 сравнения; выход 30 - диаграмма сигнала с первого выхода АбК индицирующего о наличии неисправнос ти в устройстве; вход 31 - диаграм ма сигналов, поступающих на блок 2 сравнения, в том числе 32 - диаграм ма сигнала с выхода цифроаналогового преобразователя 1, а 33 - диаграмма сигнала с выхода выходного коммутатора 3; сброс 34 - диаграмма сигнала, обеспечивакяцего установку в исходное состояние триггера 9; выход 35 - диаграмма токов, поступающих с блока 6 коррекции на входной коммутатор 5, в том числе символом i, указано значение втекающего тока генератора 17, символом 1 |л - значение вытекающего тока генератора 18, сим- значение втекакщего геволом 1 нератора 19, символом i,. - значение вытекакщего тока генератора 20. АОК 7 при поступлении на его вход сигнала Обращение обеспечивает анализ сигналов, поступающих с блока 2 сравнения, выработку сигналов управления для блока 6 коррекции и регистрацию сбоев устройства с помощью триггера 9. Время записи в накопительный элемент 4 находится в прямой зависимости от напряжения, которое требуется записать в накопительный элемент 4, . т.е., чем больше разность значений напряжений между тем, которое хранится накопительным элементом 4 на момент записи, и значением вновь записываемого напряжения, тем больше время требуется для записи. С целью сокпащения времени записи значение выходного тока одного из управляемых генераторов втекающих токов, например генератора 17,и одного из управляемых генераторов вытекающих токов, например генератора 19 тока, должно быть больше значения токов генераторов 18 и 20. Одновременно для компенсации динамической погрешности от действия ускоренной записи в накопительный элемент 4 порог срабатывания одного из компараторов блока 2 сравнения, например компаратора 21, меньше декодируемого напряжения на величину Vq причем величина Vo тем больше, чем больше ток генератора 1 9 и чем больше величина задержки выключения этого генератора тока, сигнал с выхода компаратора 22 определяет знак рассогласования выходного напряжения. Устройство работает Следующим образом. Режим, работы устройства определяется сигналом, поступающим на его вход по шине Запись. При значении

этого сигнала, соответствующего логическому нулю, устройство работает в режиме регенерации ранее записанных напряжений в накопительные элементы. А при значении этого сигнала логической единицы устройство работает в режиме записи новой информации в накопительные элементы. При работе устройства как в одном, так и в другом режимах на его входы непрерывно поступают код номера накопительного элемента и код выходного напряжения, при этом входная информация сопровождается сигналом, поступающим на вход устройства по шине Обращение. В соответствии с поступившей информацией выходной коммутатор 3 подключает выход соответствукщего накопительного элемента 4 к входу блока 2 сравнения, а вход того же накопительного элемента 4 с помощью входного коммутатора 5 подключается к блоку 6 коррекции.

Поступивщий код напряжения декодируется цифроаналоговым преобразователем 1, с выхода которого сигнал поступает на второй вход блока сравнения.

При нормальной работе устройства в режиме регенерации по фронту сигнала Обращение устанавливается в единичное состояние либо триггер 14 либо триггер 15 и соответственно включается один из управляемых генераторов 18 и 20 блока 6 коррекции. Выходное напряжение при этом начинает изменяться, приближаясь по значению к напряжению, эквивалентному входному коду. При равенстве этих напряжений сигнал на выходе блока 2 сравнения меняется на противоположный, и взведенньй триггер АОК 7 устанавливается в нулевое состояние, отключая тем самым ранее включенный управляемьй генератор тока блока 6 коррекции.

В режиме Запись в случае если напряжение с выхода накопительного элемента 4 меньше напряжения, эквивалентного входному коду, на величину V о по фронту сигнала Обращение устанавливаются в единичное состояние триггеры 13 и 15, включая тем самым управляемые генераторы 18 и 20 вытекакщего тока. При переходе сигнала с выхода компаратора 21 блока 2 сравнения из состояния О в состояние 1 триггер 13 устанавли-

k вается в нулевое состояние, включая тем самым управляемьй генератор 9 тока. После срабатывания компаратора 21 выходное напряжение продолжает ускоренно нарастать за счет инерционности элементной базы, а потом оно

дотягивается до значения, эквивалентного входному коду, за счет действия включенного генератора 20. После перехода сигнала с выхода компаратора 22 из состояния О в состояние 1 триггер 15 устанавливается

в нулевое состояние, выключая тем самым генератор 20. По спаду сигнала Обращение процесс записи в выбранный накопительньй элемент 4 считается законченным. Если в момент

поступления сигнала Обращение на выходе компаратора 21 сигнал соответствует 1, то устанавливается в единичное состояние триггер 11, который в свою очередь включает управляемьш генератор 17 втекающего тока,

При этом выходное напряжение начинает ускоренно уменьшаться, в результате чего через некоторое время на выходе компаратора 21 устанавливается сигнал О, и триггер переходит в нулевое состояние, выключая тем самым генератор 17. Одновременно после перехода триггера 11 в нулевое состояние элемент И 12 выдает сигнал, по

фронту которого устанавливаются в единичное состояние триггеры 13 и 15, и далее процесс записи происходит по описанному алгоритму.

При наличии в устройстве неисправности, когда выходное напряжение выбранного накопительного элемента 4 за интервал времени, равньй длительности сигнала Обращение, не устанавливается по значению равным входовому коду, включенные ранее триггеры 11, 4 и 15 АОК 7 при этом не сбрасываются, и через элемент ИЛИ 16 сигнал с нихnocTjTiaeT на 3 -вход триггера 9, которьй по спаду сигнала Обращение

устанавливается в единичное состояние , индицируя при этом аварийньй режим работы устройства. После устранения неисправности триггер 9 приводится в

исходное состояние подачей импульса шине Сброс на его вход .

| БИБЛИОТЕКА | 0 |

|

SU363201A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ВСЕСОЮЗНАЯ IПАТЕйТ1ш-т?Х[-1г:=;^*ндн|БИьЛИО'"'"КЛ I | 0 |

|

SU340077A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-23—Публикация

1983-03-10—Подача