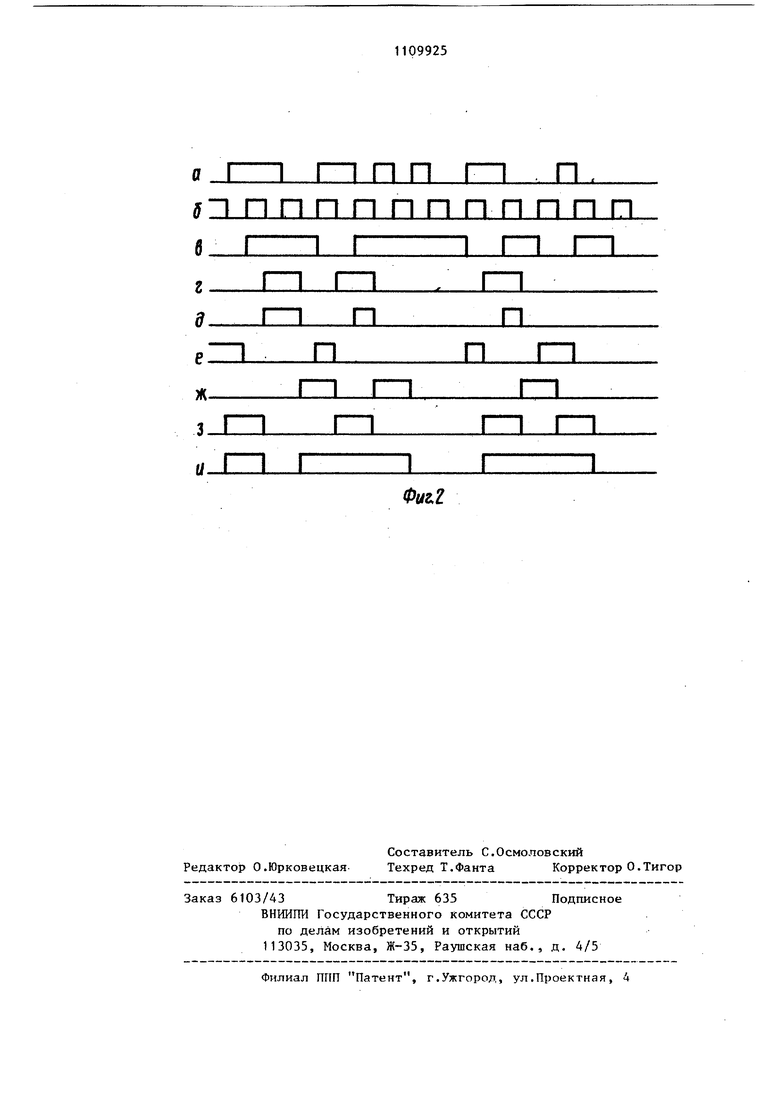

Изобретение относится к технике связи и может быть использовано для преобразования цифрового сигнала CMI (code mark invertion) линейного тракта при передаче информации по волоконно-оптическому кабелю в цифровой информационный сигнал NRZ. Известен преобразователь двоичной информации, содержащий блок стробирования, счетньй триггер, два элемента И, инвертор и элемент ИЛИ tlj. Недостатком устройства является низкая помехоустойчивость из-за появ ления на выходе сложных импульсов, обусловленных разными временами задержки в параллельных цепях. . Наиболее близким к изобретению является устройство для преобразования цифрового сигнала, содержащее последовательно соединенные первый регистр сдвига и дешифратор, а также последовательно соединенные второй регистр сдвига и элемент ИЛИ, второй дешифратор, выходы которого подключены к соответствующим входам второго регистра сдвига, и блок разделени полярности, выходы которого подключе ны к соответствующим входам первого и второго регистров сдвига 21. Однако известное устройство имеет недостаточную помехоустойчивость при высоких скоростях преобразуемых сигналов из-за обратных связей, охватывающих регистры сдвига и дешифратор. Цель изобретения - повьшение поме хоустойчивости. Для достижения поставленная цели в устройство для преобразования цифрового сигнала, содержащее последова тельно соединенные первый регистр сдвига и дешифратор, а также последовательно соединенные второй регист сдвига и элемент ИЛИ, введен В -триг гер, к D -входу которого подключен вьпСод элемента ИЛИ, а С-вход З)-три гера объединен с первьм входом первого регистра сдвига, три этом выходы дешифратора подключены к первому и второму входам второго регистра сдвига, а первый, второй и третий входы первого регистра сдвига являются соответственно первым, вторым и третьим входами устройства, причем третий вход второго регистра сдвига объединен с третьим входом первого регистра сдвига. На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - времен-i ныё диаграммы, иллюстрирующие его работу. Устройство содержит первьй регистр 1 сдвига, дешифратор 2, второй регистр 3 сдвига, элемент ИЛИ 4, li-триггер 5. Устройство работает следующим образом. Сигнал CMI, подлежащий преобразованию (фиг. 2а), поступает на вход W устройства, а на входы Т и И прдается прямая (фиг. 2 J ) и инверсная тактовые частоты соответственно. На прямых выходах первого регистра 1 сдвига появляются сигналы (фиг. 25 и г), соответствующие сдвигу информационного сигнала сигналами прямой и инверсной тактовых частот. На инверсных выходах первого регистра 1 получаются сигналы, обратные сигналам на прямых выходах (фиг. 2Ьиг). Дешифратор 2 необходим для вьщеления импульсов, соответствующих появлению на входе .1 устройства длительных единичных или нулевых импульсов. Для выравнивания фронтов полученных с дешифратора 2 импульсов (фиг.2 ие) служит второй регистр 3 сдвига, на выходах которого получаем импульсы (фиг. 2 ж и 5 ), необходимые для даль нейших преобразований. С выхода второго регистра 3 сдвиГа сигналы (фиг. 2)киз) поступают на элемент ИЛИ 4 и далее на вход Ь-триггера 5. На выходе D-триггера 5 получается требуемый цифровой сигнал в коде (фиг. 2ii). Предлагаемое устройство обладает высокой помехоустойчивостью за счет введения Т) -триггера, а также за счет новых связей между блоками. Изобретение предназначено для работы на городских цифровых световодных системах передачи. Кроме того, предлагаемое устройство обладает более высоким быстродействием, что позволяет использовать его в аппаратуре, работающей как со скоростью 8 Кбит/с, так и 34 Мбит/с.

g I I ГП П П r i П . П П П П П П П П П П П

II

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ КАНАЛЬНОГО КОДА | 2012 |

|

RU2521299C1 |

| Устройство для обнаружения ошибок цифрового сигнала | 1985 |

|

SU1334377A1 |

| Устройство для определения достоверности информации | 1983 |

|

SU1092742A1 |

| Устройство для преобразования кода цифрового сигнала | 1983 |

|

SU1141580A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Устройство для преобразования цифровых сигналов | 1991 |

|

SU1803982A1 |

| Коммутатор | 1988 |

|

SU1520664A1 |

| Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью | 1986 |

|

SU1381703A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА, содержащее последовательно соединенные первый регистр сдвига и дешифратор, а также последовательно соединенные второй регистр сдвига и элемент ИЛИ, отличающееся тем, что, с целью повыпения помехоустойчивости, в него введен J)-триггер, к В -входу которого подключен выход элемента ИЛИ а С-вход Ъ -триггера объединен с первым входом первого регистра сдвига, при этом выходы дещифратора подключены к первому и второму входам второго регистра сдвига, а первый, второй и третий входы первого регистра сдвига являются соответственно первым, вторым и третьим входами устройства, причем третий вход второго регистра сдвига объединен с третьим входом первого регистра сдвига. (Л

я 1-I П П

p lПП

Ж- 3.

I/.

0UtZ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичной последовательности в дуобинарную | 1978 |

|

SU708527A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь кода | 1978 |

|

SU705693A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-23—Публикация

1982-12-21—Подача