четвертого элемента ИЛИ, входы которого соединены с соответствуюпщми входами третьего регистра сдвига, выход последнего разряда которого соединен с вторьм входом четвертого элемента И и первым BXO,J,OM Btoporo элемента И, второй вход которого соединен с входом синхронизации третьего регистра сдвига и выходом первого элемента И, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй вх:од которого соединен с выходом третьег элемента И, выход первого элемента ИЛИ соединен с входами синхронизации D -триггеров первой и второй .групп, выходы D -триггеров второй группы соединены с соответствуюпщми входами первой группы входов первой матрицы элементов И, выходы D -триггеров первой группы соеднены с соответствующими входами второй группы входов первой матрицы элементов И, выходы первой группы которой соединены с соответствующими входами первой группы входов второй матрицы элементов И, выходы второй группы выходов первой матрицы элементов И через вторую группу сумматоров по модулю два соединены с соответствующими входами второй группы входов второй матрицы элементов И, выходы которой соединены с соответствующими входами первой группы входов первой группы сумматоров по модулю два, выходы третьей группы выходов первой матрицы элементов И через третью группу сумматоров по модулю два соединены с соот1зетствуюпц1ми входами второй группы входов первой группы су шаторов по модулю два, четвертьй выход первой матрицы элементов И соединен с третьим входом первой группы сумматоров по модулю два, третья группа входов второй матрицы элементов И соединена с соответствующими выходами блока регистров сдвига, информационные входы которых соединены с соответствующими выходами элементов И третьей группы, вхоДы синхронизации регистров сдвига блока соединен с соответствующими выходами элем нтов И четвертой группы, первые вход элементов И третьей и четвёртой . групп соединены с соответствующими переключателями группы, вторые входы элементов И третьей группы соединены с выходом регистра сдвига с обратными связями, вход которого соединен с выхоДом генератора одиночных импульсов и вторыми входами элементов И четвертой группы, установочные входы регистра сдвига с обратными связями соединены с выходами четвертого блока тумблеров, установочные входы первого, второго и третьего регистров сдвига соединены с выходами первого, второго и третьего блоков тумблеров соответственно, выходы первого и второго регистров сдвига соединены с входам второго и третьего элементов РШИ соответственно, выход третьего элемента ИЛИ соединен с входом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для обучения | 1987 |

|

SU1580423A1 |

| Устройство управления доступом | 1986 |

|

SU1423816A1 |

| Устройство формирования модифицированных М-последовательностей | 2023 |

|

RU2801743C1 |

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| Генератор псевдослучайных последовательностей импульсов | 1981 |

|

SU978147A1 |

ФОРМИРОВАТЕЛЬ КОДОВ, содержащий генератор тактовых импульсов, первую группу сумматоров по модулю два, выходы которых соединены с входами блока индикаторов, регистр сдвига с обратными связями и блок памяти, отличающийсй тем, что, с целью повышения быстродействия формирователя кодов, он дополнительно содержит первьй, второй, третий и четвертый элементы И, вторую и третью группы сумматоров по модулю два, первый, второй и третий регистры сдвига, первый, второй, третий, четвертый, пятый и шестой блоки тумблеров, первьй, второй, третий и четвертый элементы ИЛИ, первую и вторую матрицы элементов И, первую, вторую, третью и четвертую группы элементов И, первую и вторую группы В -триггеров, группу . элементов ИЛИ, блок регистров сдвига, rpjrnny переключателей, генератор одиночных импульсов, элемент , индикации, элемент НЕ, выход которого соединен с первым входом первого элемента И и первьм входом четвертого элемента И, выход которого соединен с первыми входами элементов И второй группы, вторые входы элементов И второй группы соединены с соответствую.щими выходами блока памяти, первая группа входов которого соединена с выходами шестого блока тумблеров, вторая группа входов блока памяти соединена с выходами первой группы сумматоров по модулю два, вторыми входами срответствующих элементов И первой группы и соответствующими информационными входами D -триггеров первой группы, установочные входы J) -триггеров первой группы соединены с выходами (Л пятого блока тумблеров установочными входами D -триггеров второй группы, информационные входы D -триггеров второй группы соединены с соответствующими выходами элементов ИЛИ группы, первые входы элементов ИЛИ группы соединены с соответствующими выходами элеменiu тов И второй группы, вторые входы СП элементов ИЛИ группы соединены с 4 соответствующими выходами элеменО5 тов И первой группы, вторые входы СО элементов И первой группы соецинецы с выходом второго элемента РШИ и первым входом третьего элемента И, второй вход которого соединен с входом синхронизации блока памяти, вторым входом первого элемента И, входом синхронизации второго регистра сдвига, входом синхронизации первого регистра сдвига и выходом генератора тактовых импульсов, вход которого соединен с входом элемента ивдикации и выходом

Изобретение относится к импульсной тех1шке.

Известен генератор псевдослучайHbix чисел,, содержащий m-разрядньй регистр сдвига с сумматором по модулю два в цепи обратной связи регистра сдвига и группу многовходовых .сумматоров по модулю два, соединенных с выходами триггеров регистра сдвига LI 3.

Указанньм генератор не позволяет определить коды, обусловливающие

топологию связей h -входового сумматора по модулю два, на выходе которого получается копия исходной псевдослучайной последовательности, сдвинутая на требуемое количество тактов.

Наиболее близким к предлагаемому является устройство для формирования сдвинутых копий псевдослучайного сигнала, состоящее из генератора тактовых импульсов, первого элемента Запрет, регистра сдвига с

3

обратной связью, дешифратора, второго элемента Запрет, счетчика, блоков памяти, сумматоров по модулю и индикаторов 2 ,

Используя данное устройство,можно определять коды топологии связей m -входового сумматора по модулю два, на выходе которого получается копия исходной псевдослучайной последовательности, сдвинутая на требуемое количество тактов, когда в цепи обратной связи регистра сдвига включен многовходовой сумматор по модулю два. Однако устройство имеет низкое быстродействие, так как для определения кодов, определяющих топологию связей многовходового сумматора по модулю два, необходимо выполнить 2 элементарных тактов работы, (где - требуемый сдвиг псевдослучайной последовательности),

Цель изобретения - повышение быстродействия устройства,

Прставленная цель достигается тем, что фор1 шрователь кодов, содержащий генератор тактовых импульсов, первую группу сумматоров по модулю два, выходы которых соединены с входами блока индикаторов, регистр сдвига с обратными связями и блок памяти, дополнительно содержит первый, второй, третий и четвертый . элементы И, вторую и третью группы сумматоров по модулю два, первый, второй и третий регистры сдвига,первьй, второй, третий, четвертьш,пятый и шестой блоки тумблеров,первый второй, третий и четвертый элементы ИЛИ, первую и вторую матрицы элементов И, первую, вторую, третью и чётвертзпо группы элементов И,первую и вторую группы D -триггеров,групп элементов ШШ, блок регистров сдвига, группу переключателей, генератор одиночных импульсов, элемент индикации, элемент НЕ, выход которого соединен с первым входом первого элемента Ни первым входом четвертого элемента И, выход которого соединен с первыми входами элементов И второй группы, вторые входы элементов И вторбй группы соединены с соответствующими выходами блока памяти, первая группа входов которого соединена с выходами шестого блока тумблеров, вторая группа входов блока памяти соединена с выходами первой группы сумма-

5469 4

торов по модулю два, вторыми входами соответствующих элементов И первой группы и соответствуюп5ими информационными входами D -триггеров, первой группы, установочные входы Л -триггеров первой группы соединены с выходами пятого блока тумблеров и установочными входами D -триггеров второй группы,

JQ информационные входы Р -триггеров второй группы соединены с соответствующими выходами элементов ИЛИ группы, первые входы элементов ИЛИ 1 руппы соединены с соответствующими выходами элементов И второй группы, вторые входы элементов ИЛИ группы соединены с соответствующими выходами элементов И первой группы, вторые входы элементов И первой группы соединены с выходом второго элемента ШШ и первым входом третьего элемента И, второй вход которого соединен с входом синхронизации блока памяти, вторым входом первого элемента И, входом синхронизации второго регистра сдвига, входом синхронизации первого регистра сдвига и выходом генератора тактовых импульсов, вход которого соединен с . входом элемента индикации и выходом четвертого элемента ИЛИ, входы которого соединены с соответствующими выходами третьего регистра сдвига, выход последнего разряда которого соединен с вторым входом четвертого элемента И и первым входом второго элемента И, второй вход которого соединен с входом синхронизации третьего регистра сдвига и выходом первого элемента И, выход

второго элемента И соединен с

первьм входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход первого элемента ИЛИ соединен с

5 входами синхронизации К -триггеров первой и второй групп, выходы D-триггеров второй группы соединены с соответствующими входами первой группы входов первой матрицы эле50 ментов И, выходы Г -триггеров первой группы соединены с соответствующими входами второй группы входов первой матрицы элементов И, выходы первой группы которой соединены

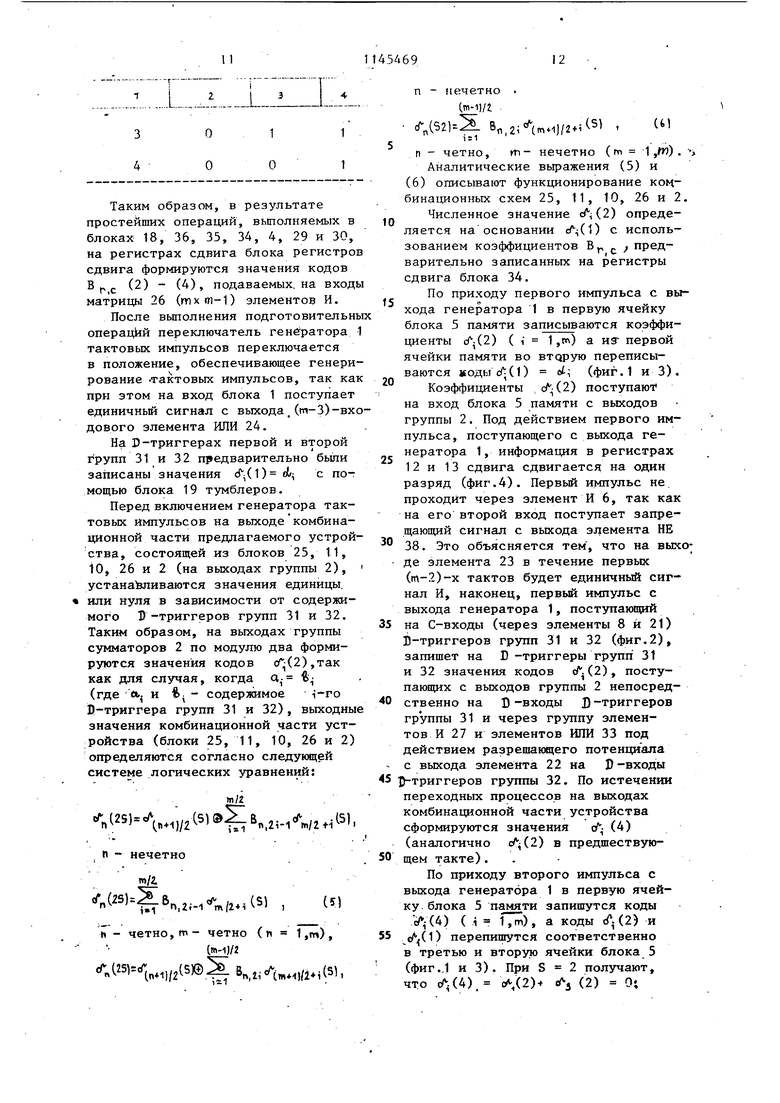

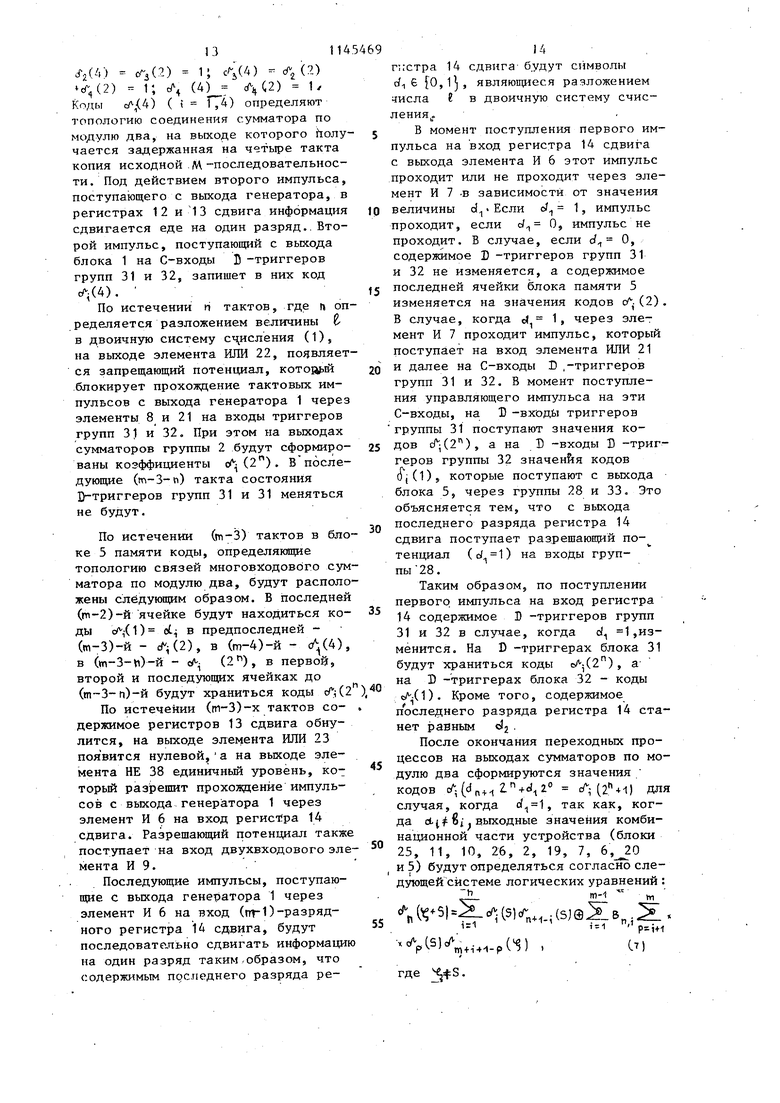

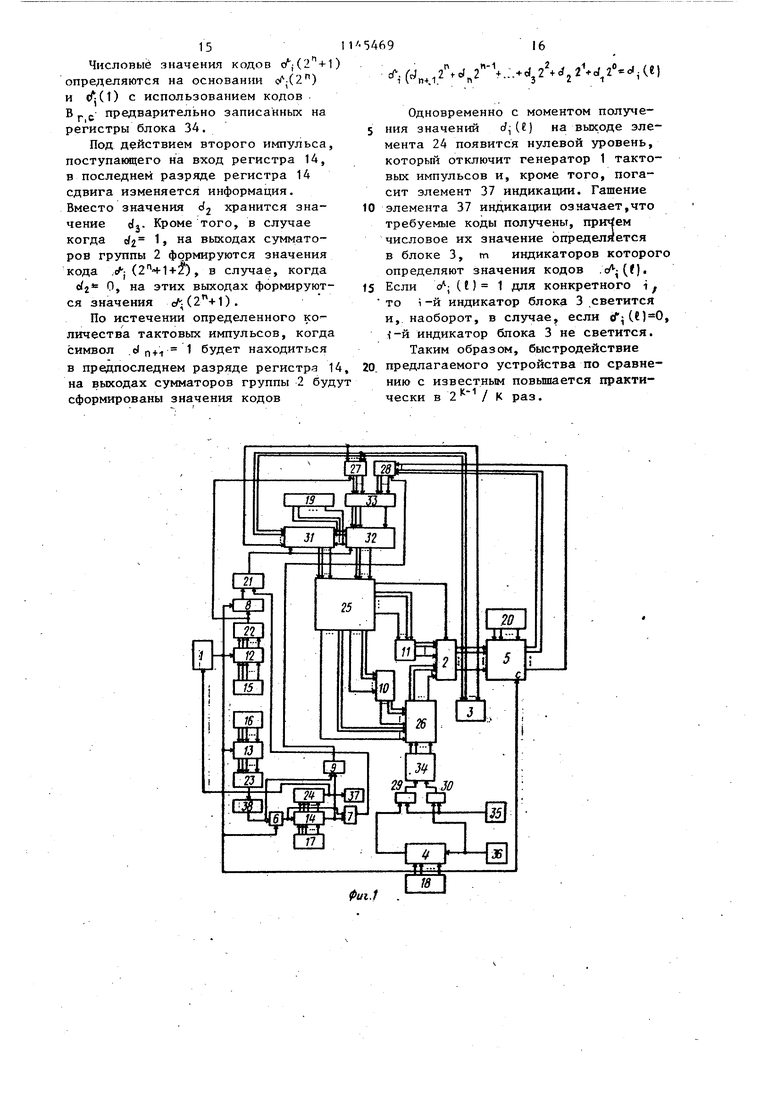

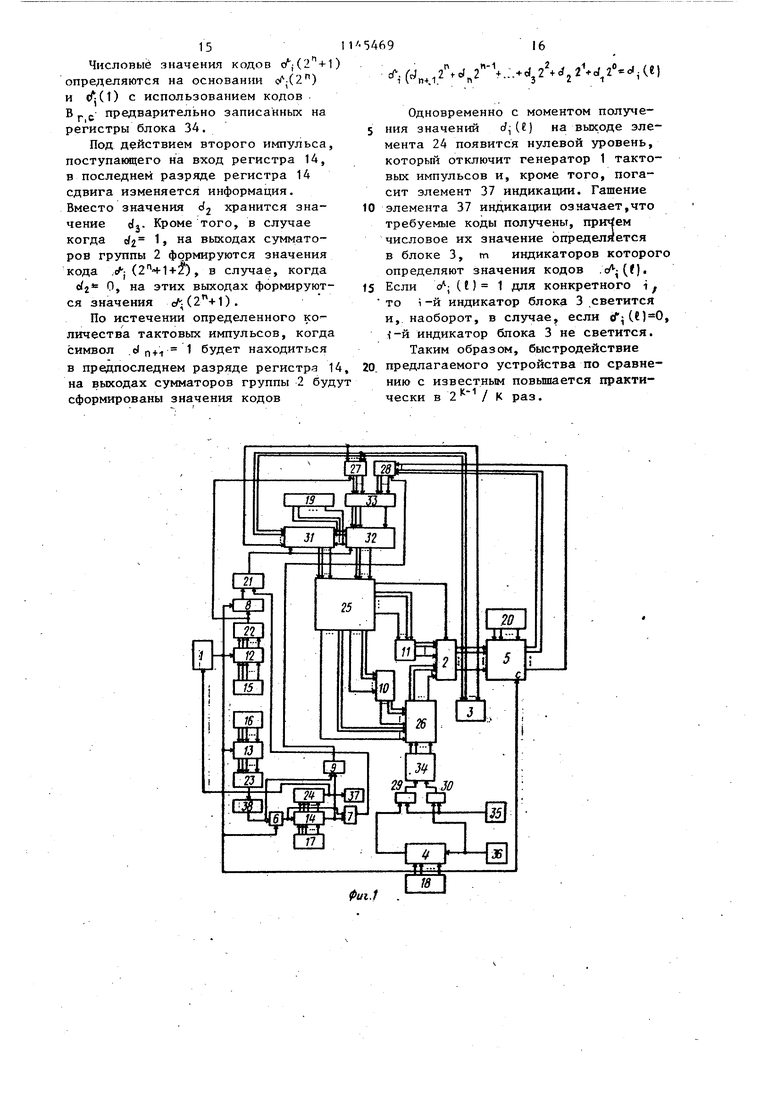

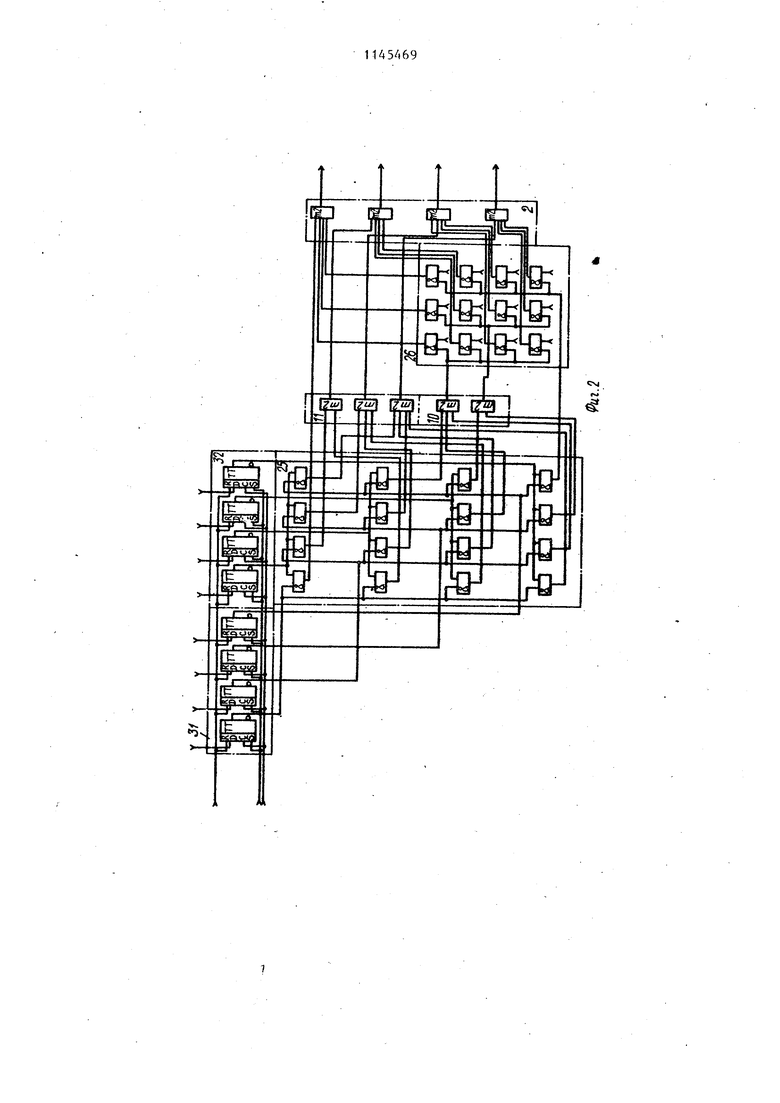

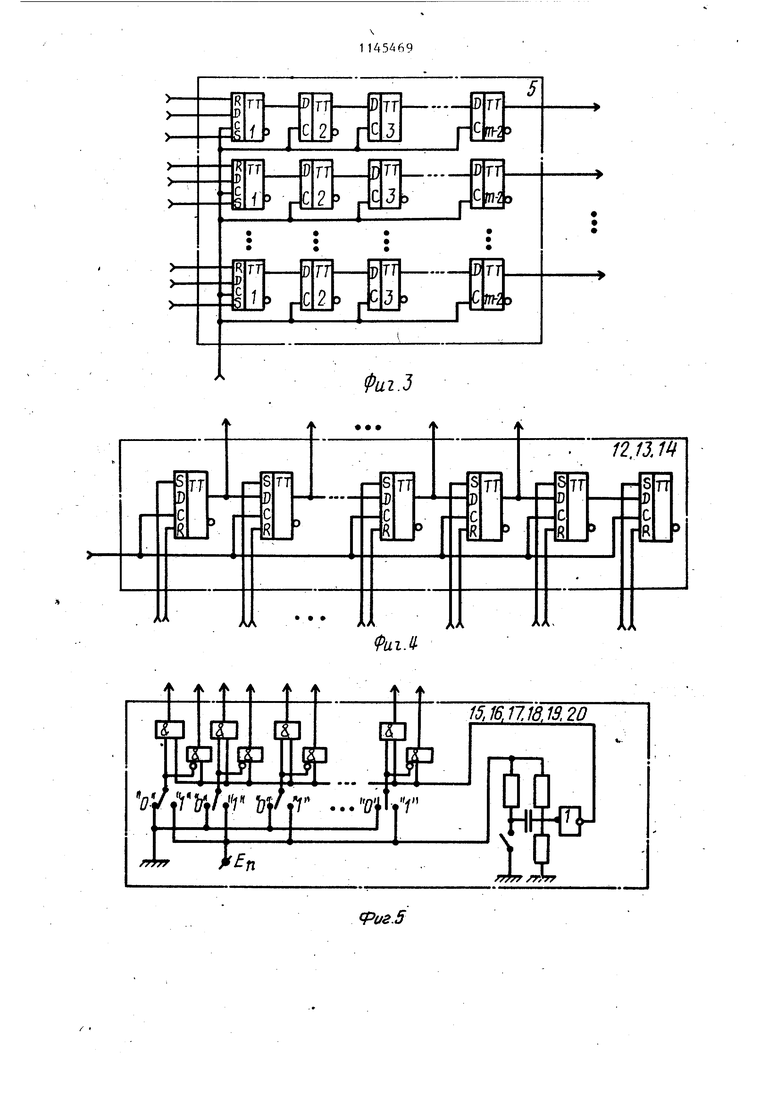

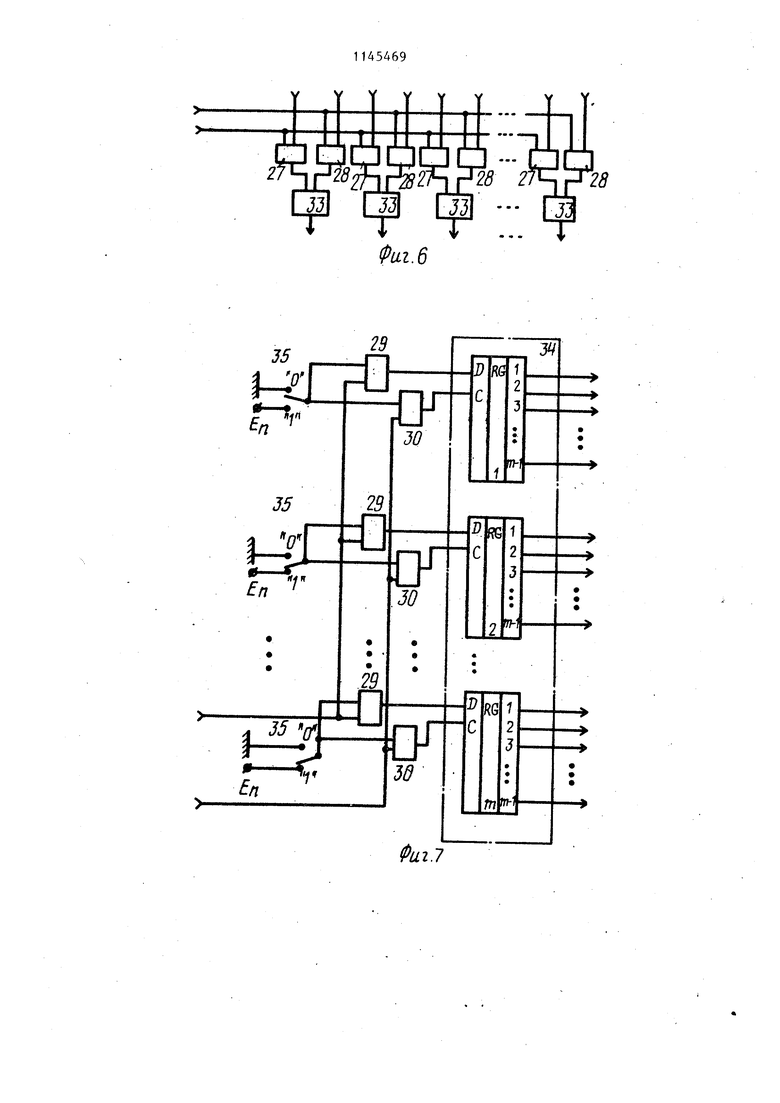

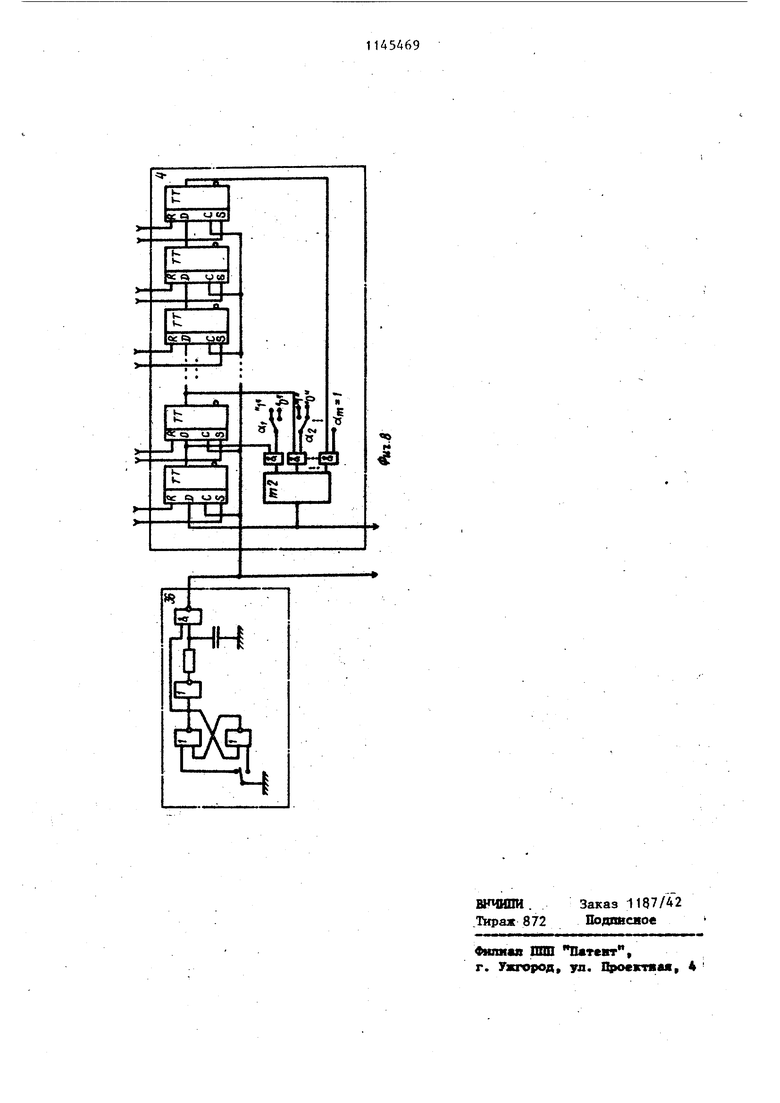

55 с соответствующими входами первой группы входов второй матрицы элементов И, выходы второй группы выходов первой матрицы элементов И S1U через вторую группу сумматооов.ро модулю два соединены с соответствую щими входами второй группы входов второй матрицы элементов И, выходы которой соединены с соответствуто дими входами первой группы входов первой группы сумматоров по модулю два, выходы третьей группы выходов первой матрицы элементов И через третью группу сумматоров по модулю два соединены с соот1ветствую щими входами второй группы входов первой группы сумматоров по модулю два, четвертый выход первой матрицы элементов И соединен с третьим входом первой группы сумматоров по модулю два, третья группа входов второй матрицы элементов И соединена с соответствующими выходами блока регистров сдвига, информационные входы которьпс соединены с соответствующими выходами элементов И третьей группы, входы синхронизации регистров сдвига блока соединены с соответствующими в.ыходами элементов И четвертой группы, первые входы элементов И третьей и четвертой групп соединены с соот. ветствующими переключателями группы, вторые входы элементов И третьей группы соединены с выходом регистра сдвига с обратными связями, вход которого соединён с выходом . генератора одиночных импульсов и вторыми входами элементом И четвертой группы, установочные входы регистра сдвига с обратными связями соединены с выходами четвертого блока тумблеров, установочные входы первого, второго и третьего р-егистров сдвига соединены с выходами первого, второго -и третьего блоков тумблеров соответственно, выходы первого и второго регистров сдвига соединены с входами второго и третьего элементов ИЛИ соответственно, выход третьего элемента ИЛИ соединен с входом элемента НЕ. На фиг.1 приведена структурная схема устройства; на фиг.2 - перва и вторая группы D -триггеров, перв и вторая матрицы элементов И, первая, вторая и третья группы сум маторов по модулю два и два формир вателя кодов; на фиг.З - блок памя ти формирования кодов; на фиг.4 регистр сдвига формирователя кодов на фиг.З - блок тумблеров формирователя кодов; на фиг.6 - первая и вторая группы элементов И и группа элементов -ШИ формирователя кодов-, на фиг.7 - группа переключателей, третья и четвертая группы элементов И и блок рехистров сдвига формирователя кодов;на фиг. 8 - регистр сдвига и генератор одиночт1ых импульсов формирователя кодов. I Формирователь кодов (фиг.1) содержит генератор 1 тактовых импульсов, первую группу 2 сумматоров по модулю два, выходы которых соединены с входами блока 3 индикаторов, регистр 4 сдвига с обратными связями, блок 5 памяти, первьш 6, второй7, третш 8 и четвертый 9 элементы И, вторую 10 и-третью 11 группы сумматоров по модулю два, первьш 12, второй 13 и третий 14 регистры сдвига, nepBbrfi 15, второй 16, третий 17, четвертьй 18, пятый 19 и шестой 20блоки тумблеров, первый 21, второй 22,третий 23 и четвертый 24 элементы ИЛИ, первую 25 и вторую 26 матрицы элементов И, первую 27, вторую 28, третью 29 и четвертую 30 группы элементов И, первую 31 и вторую 32 группы D -триггеров, группу 33 элементов ИЛИ, блок 34 регистров сдвига, группу 35 переключателей, генератор 36 одиночных импульсов, элемент 37 индикации, элемент НЕ 38, выход которого соединен с первым входом первого элемента И 6 и первым входом четвертого элемента-И 9,выход которого соединен с первыми входами элементов И второй грзттпы 28, вторые входы элементов И второй группы 28 соединены с соответствующими выходами блока 5.памяти, первая группа входов которого соединена с выходами,шестого блока 20 тумблеров, вторая группа входов блока 5 памяти соединена с выходами первой группы 2 сумматоров по модулю два, вторыми входами соответствующих элементов И первой группы 27 и соответствующими информационнь ми входами 1)-триггеров первой группы 31, установочные входы В -триггеров первой группы 31 соединены с выходами пятого блока 19 тумблеров и установочньнчи входами D -триггеров второй группы 32, информационные входы D-триггеров второй группы 32 соединены с соответствующими выходами элементов ИЛИ группы 33, первые

7

входы элементов ИЛИ группы 33 соединены с соответствующими выходами элементов И,второй группы 28, вторые входы элементов ИЛИ группы 33 соединены с соответствующим выходами элементов И первой группы 27, вторые входы элементов И первой группы 27 соединены с вьосодом второго элемента ИЛИ 22 и первым входом третьего элемента И 8, второй вход которого соединен с входом синхронизации блока 5 памяти, вторым входом первого, элемента И 6,входом синхронизации второго регистра 13 сдвига входом синхронизации первого регистра 12 сдвига и выходом генератора 1 тактовых импульсов, вход которого соединен с входом элемента 37 индикации и выходом четвертого элемента ИЛИ 24, входы которого соединены с соответствующими выходами третьего регистра 14 сдвига, выход последнего разряда KOTOjioro соединен с вторым входом четвертого элемента И 9 и первь1М входом второго элемента И 7, второй вход которого соединен с входом синхронизации третьего регистра 14 сдвига с выходом первого элемента И 6, выход второго элемента И 7 соединен с первым входом первого элемента ИЛИ 21, второй вход которрго соединен с выходом третьего элемента И 8, выход первого элемента ИЛИ 21 соединен с входами синхронизации В -триггеров первой 31 и второй 32 групп, выходы D -триггеров второй группы 32 соединены с соответствующими входами первой группы входов первой матрицы 25 элементов И, выходы D -триггеров первой группы 31 соединены с соответствующими входами второй группы входов первой матрицы 25 элементов И, выходы первой группы которой соединены с соответствующими входами первой группы входов второй матрицы 26 элементов И, выходы второй группы вькодов первой матрицы 25 элементов И через вторую группу 10 сумматоров по модулю два соединены с,соответствующими входами второй группы входов второй матрицы 26 элементов И, выходы которой сЬединены с соответствующими входами первой группы входов первой группы 2 сумматоров по модулю два, выходы третьей группы выходов первой матрицы 25 элементов И через третью

5/4698

группу 11 сумматоров по модулю два соединены с соответствующими входами второй группы входов первой группы 2 сумматоров по модулю два, 5 четвертый выход первой матрицы 25 элементов И соединен с третьим входом первой группы 2 сумматоров по модулю два,, третья группа входов второй матрицы 26 элементов И соеfO динена с. соответствующими выходами блока 34 регистров сдвига, информационные входы которых соединены с соответствующими выходами элементов И третьей группы 29, входы синхронизации регистров сдвига блока / 34 соединены с соответствующими выходами элементов И четвертой группы 3Q, первые входы элементов И третьей 29 и четвертой 30 групп

20 соединены с соответствующими пере- ключа телями группы 35, вторые входы элементов И третьей группы 29 соединены с выходом регистра 4 сдвига с обратными связями, вход

5 которого соединен с выходом генератора 36 одиночных импульсов и вторыми входами элементов И четвертой группы 30, установочные входы регистра 4 сдвига с обратными

0 связями соединены с выходами четвертого блока 18 тумблеров, установочные входы первого 12, второго 13 и третьего 14 регистров сдвига соединены с выходами перрого 15, второго 16 и Tpetbero 17 блоков тумблеров соответственно, выходы первого 12 и второго 13 регистров сдвига соединены с входами второго 22 и третьего 23 элементов ИЛИ соотд ветственно, выход третьего элемента ИЛИ 23 соединен с входом элемента НЕ 38.

Формирователь кодов работает еле- . дующим образом.

Исходной информацией для получения кодов, определяю1цих топологию связей многовходового cjn« aTopa по модулю два, является величинд сдвига I , представленная в двоичной системе исчисления:

П . 11-1

.. (1)

где с 1} d,.,ii(l7n ) - двоич5 ные цифры числа С и, кроме тогб, -последовательность в виде значакия m и коэффициентов d б , i fi 1, пп определяющих вид полинома,для 911 которой необходимо сформировать сдв нутую копию. Используя блоки 15, 17, 16, 19, 20, 18, 36, 29, 30, 35 и 34, устрой ство подготавливают к работе. Еря этом выполняется следующие операции. Код числа (двоичньш) с помйщью блоков 15 и 17 из (tn-1) тумблеров записывается на (m-l)-e разрядные регистры 12 и 14 (фиг.4). Аналогичным образом с помощью блока 16 из (т-2) тумблеров код 100..000 записывается на (т-2)-й разрядный регистр 13 сдвига. Запись кода на регистр осуществляется в два этапа: набор кода на тумблерном наборе и непосредственно запись кода под управлением генератора одиночных импульсов, входящего всостав блоков 15, 17, 16, 19,. 20 и 1-8 (фиг.5Ь Значение коэффициента o(,j (i 1,m) записьшается на D -триггеры двух групп 31 и 32 по m I) -триггеров с помоп1ью тумблерного набора блока 19 из тумблеров аналогично записи значения величины ; Коэффициенты cL (i 1 ,m) записьшаются в блок 5 памяти как первое из (tn-2)-x m-раз рядньк слов, хранимых в блоке 5. Запись осуществляется с помощью блока 20 аналогично записи величины . При этом учитывается, что оС и. сА (1) (ч 1,tn) равны между собой и составляют коды, определяющие топологию соединейия сумматора по модулю два с разрядами сдвига, на выходе которого получается задержанная на одрн такт М-последовательность. С помощью блока 18 из m тумблеров на регистр 4 сдвига с обратными связями записывается код 000...001, а первьй переключатель из группы 35 (фиг.7) устанавливается в единичное положение, разрешая прохождение информации через первый элемент И группы 29 наD-вх первого регистра блока 34, а также прохождение управляющих импульсов через первый элемент И группы 30 на С-вход первого регистра блока 34. Все остальные переключатели группы 35 устанавливаются в нулево положение.. .

После нажатия кнопки генератора 36 одиночных импульсов с выхода регистра 4 (фиг. 8) значение В 1 записывается в ()-й разряд первого регистра блока 34. Кроме того, под действием этого импульса состояние регистра 4 сдвига изменяется и становится равным 100.,.00. По приходу следующего импульса с выхода генератора 36 одиночных импульсов на первом регистре блока 34 будет записан код 000. .,ОВ , на регистре 4 - В « 00. По истечении (m-l)-ro такта под дейтвием управляющих импульсов с выода генератора 36 на первом регисте блока 34 сформируется вектор коов В Bi2 Bi3 -.В.. . Формиование кодов в регистре 4 можно писать системой уравнений: 1 С-1 Чс .. (М Для формирования кодов В {. (г 2,т ) на регистр 4 сдвига с обратными связями записывается начальный код, как и в случае, когда h 1, и под управлением генератора 36 одиночных импульсов и группы 35 переключателей на г-и регистр сдвига блока 34 записывается вектбр кодов , б Ч -- Аналитически формирование коэффициентов описьгаается уравнениями (3) и (4) Q -cL ,1 Г-1 С-1 ,c , г-1 В .,B ., -, (5) м id С-1 В, . В., (, ,m-«)-, t t л m,i°ni-i « m-iBr,,iвт. Например, для случая, когда т 4, о1, 1, ol2 О, 3 0i 064 t, получают (.i ПЛ, г 1,4, С 1,3) значения В рд.

Таким образом, в результате простейших операций, вьтолняемых в блоках 18, 36, 35, 34, 4, 29 и 30, на регистрах сдвига блока регистров сдвига формируются значения кодов г,с подаваемых, на входы матрицы 26 (mxm-1) элементов И.

После вьшолнения подготовительны операций переключатель генератора 1 тактовых импульсов переключается в положение, обеспечивающее генерирование Тактовых импульсов, так как при этом на вход блока 1 поступает единичньй сигнал с выхода,(т-3)-входоврго элемента ИЛИ 24.

На D-триггерах первой и второй групп 31 и 32 предварительно были записаны значения сГ-(1)Л с по-: мощью блока 19 тумблеров.

Перед включением генератора тактовых импульсов на выходе комбинационной части предлагаемого устройства, состоящей из блоков 25, 11, 10, 26 и 2 (на выходах группы 2), устана пиваются значения единицы, или нуля в зависимости от содержимого D -триггеров групп 31 и 32. Таким образом, на выходах труппы сумматоров 2 по модулю два формируются значения кодов сЛ(2),так как для случая, когда а,- ft.; (где л. и %. - содержимое i-ro D-триггера групп 31 и 32), выходные значения комбинационной части устройства (блоки 25, 11, 10, 26 и 2) определяются согласно следующей системе логических уравнений:

mlz

..),

.. .

n - нечетно

п(25)6,,2,.,./гмС5) , (П

h - четно, m- четно (п 1 ,in),

(ти)/2

« Vil/2 5®. (Sb

n - нечетно .

(m-i)/i )--X Bo,)/2.) , (И

n - четно, iTi- нечетно (m 1 ,fr)) .

Аналитические выражения (5) и (6) описывают функционирование комбинационных схем 25, 11, 10, 26 и 2. Численное значение сЛ.((2) определяется на основании сЛ.;(1) с использованием коэффициентов В предварительно записанных на регистры сдвига блока 34.

По приходу первого импульса с выхода генератора 1 в первую ячейку блока 5 памяти записываются коэффициенты сЛ(2) ( 1 1 ,т) а из- первой ячейки памяти во вторую переписываются (1) (фиг.1 и 3).

Коэффициенты cf(2} поступают на вход блока 5 памяти с выходов группы 2, Под действием первого импульса, поступающего с выхода генератора 1, информация в регистрах 12 и 13 сдвига сдвигается на один разряд (фиг.4). Первьй импульс не проходит через элемент И 6, так как на его второй вход поступает запрещающий сигнал с выхода элемента НЕ

5 на С-входы (через элементы 8 и 21) Б-триггеров групп 31 и 32 (фиг.2), запишет на D -триггеры групп 31 и 32 значения кодов сЛ-(2), поступакмцих с выходов группы 2 непосред-

0 ственно на D -входы D-триггеров группы 31 и через группу элементов И 27 и элементов ИЛИ 33 под действием разрешающего потенциала с выхода элемента 22 на В-входы

5 триггеров группы 32. По истечении переходных процессов на выходах комбинационной части устройства сформируются значения о (4) (аналогично сЛ((2) в предшествующем такте). .

По приходу второго импульса с выхода генератора 1 в первую ячейку, блока 5 памяти запишутся коды i(4) ( i 1,m), а коды e (2) и

сА(1) перепишутся соответственно в третью и вторую ячейки блока 5 (фиг.,1 и 3). При получают, что сЛ.(4). сА,(2)+ сЛд (2) 0;

13114

) 0-5(2) l; (4) - cf ) f(2) - (4) ) 1/ Коды сЛ,4) ( t 1,4) определяют топологию соединения сумматора по мс)дулю два, на выходе которого иолу чается задержанная на четыре такта копия исходной .М-последовательности. Под действием второго импульса, поступающего с выхода генератора, в регистрах 12 и 13 сдвига информация сдвигается еде на один разряд.. Второй импульс, поступающий с выхода блока 1 на С-входы Б -триггеров групп 31 и 32, запишет в них код (4). .

По истечении ri тактов, где и определяется разложением величины 6в двоичную систему с исления (1), на выходе элемента ИЛИ 22, появляется запрещающий потенциал, котой й .блокирует прохождение тактовых импулБсов с выхода генератора 1 через элементы 8 и 21 на входы триггеров групп 31 и 32. При этом на выходах сумматоров группы 2 будут сформированы коэффициенты сА(2). В последующие (m-3-fi) такта состояния D-триггеров групп 31 и 31 меняться не будут.

По истечении (tn-3) тактов в блоке 5 памяти коды, определякшще топологию связей многовходовЬго сумматора по модулю два, будут расположены следующим образом. В последней (т-2)-и ячейке будут находиться коды сЛ,( 1) ot.) в предпоследней (т-З)-й - с(2), в (т-4)-й - (А(4), в (т-З-Ь)-й - ( (2), в первой, второй и последующих ячейках до ()-й будут храниться коды сЛ(2

По истечении (т-З)-х тактов содержимое регистров 13 сдвига обнулится, на выходе элемента ИЛИ 23 появится нулевой,а на выходе элемента НЕ 38 единичный уровень, который разрешит прохождение импульсов с выхода генератора 1 через элемент И 6 на вход регистра 14 сдвига. Разрешающий потенциал также поступает на вход двухвходового элемента И 9.

Последующие импульсы, поступающие с выхода генератора 1 через элемент И 6 на вход (nfl)-разрядного регистра 14 сдвига, будут последовательно сдвигать информацию на один разряд таким-образом, что содержимым прс.педнего разряда рег;:стра 14 сдвига- будут стЫволы с/1 6 0,1 являющиеся ра.зложением числа в двоичную систему счисления,,

В момент поступления первого импульса на вход регистра 14 сдвига с выхода элемента И 6 этот импульс проходит или не проходит через элемент И 7 .в зависимости от значения величины d., Если о 1, импульс проходит, если с/ О, импульс не проходит. В случае, если с О, содержимое D -триггеров групп 31 и 32 не изменяется, а содержимое последней ячейки блока памяти 5 изменяется на значения кодов сЛ(2). В случае, когда d 1, через элемент И 7 проходит импульс, который поступает на вход элемента ИЛИ 21 и далее на С-входы Г ,-триггеров групп 31 и 32. В момент поступления управляющего импульса на эти С-входы, на D -входы триггеров группы 31 поступают значения кодов с(2), а на Б -входы Ц -триггеров группы 32 значения кодов Ojd), которые поступают с выхода блока 5, через группы 28 и 33. Это объясняется тем, что с выхода последнего разряда регистра 14 сдвига поступает разрешающий потенциал (о(1) на входы группы 28.

Таким образом, по поступлении первого импульса на вход регистра 14 содержимое В -триггеров групп 31 и 32 в случае, когда d 1,изменится. На D -триггерах блока 31 будут храниться коды е/-(2), а на D -триггерах блока 32 - коды сД(1). Кроме того, содержимое последнего разряда регистра 14 станет равным о .

После окончания переходных процессов на выходах сумматоров по модулю два сформируются значения кодов cA(d. ., сЛ-() для случая, когда , так как, когда лJ, Bj выходные значения комбинационной части устройства (блоки 25, 11, 10, 26, 2, 19, 7, 6,0 и 5) будут определяться согласно следующей теме логических уравнений :

с,(.(.,..(5 ®ХБ„Д. 1 .

)/,,,,.р() ,

С7 где 4S.

isп

Числовые значения кодов c/j(2 + l) определяются на основании /;(2) и (Aj(1) с использованием кодов В р (. предварительно записанных на регистры блока 34.

Под действием второго импульса, поступающего на вход регистра 14, в последнем разряде регистра 14 сдвига изменяется информация. Вместо значения 2 хранится значение dj. Кроме того, в случае когда ijl2 i нз выходах сумматоров группы 2 формируются значения кода .c-j (2Vl+f), в случае, когда

of2 О, на этих выходах формируются значения V().

По истечении определенного ко личества тактовых импульсов, когда символ .dп+1 1 будет находиться в предпоследнем разряде регистр-з 14, на выходах сумматоров группы 2 будут сформированы значения кодов

5469

16

-П-1

,-(п./ --- з2 22Ч2Одновременно с моментом получения значений (} на выходе элемента 24 появится нулевой уровень, которьй отключит генератор 1 тактовых импульсов и, кроме того, погасит элемент 37 индикации. Гашение элемента 37 инДикации означает,что требуемые коды получены, примем числовое их значение определяется в блоке 3, т индикаторов которого определяют значения кодов .(/(). Если (/;() 1 для конкретного i, то i-и индикатор блока 3 светится и, наоборот, в случае, если cf(e)0, д-й индикатор блока 3 не светится.

Таким образом, быстродействие предлагаемого устройства по сравнению с известным повьшается практически в / К раз.

(

Фаг.6

Фиг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Яковлев В.В., Федоров Р.Ф | |||

| Вероятностные вычислительные машины | |||

| Л., Машиностроение, 1974, с | |||

| Гонок для ткацкого станка | 1923 |

|

SU254A1 |

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования сдвинутых копий псевдослучайного сигнала | 1974 |

|

SU527012A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-15—Публикация

1983-03-09—Подача