to

15

20

25

Изобретение относится к вычисли- тельной технике и предназначено для поиска неисправностей в аппаратурных средствах цифровой вычислительной техники, в том числе для анализа выходных последовательностей при тестовом контроле многовы- ходных цифровых узл6в ЭВМ.

Цель изобретения - повьююние быстродействия анализатора.

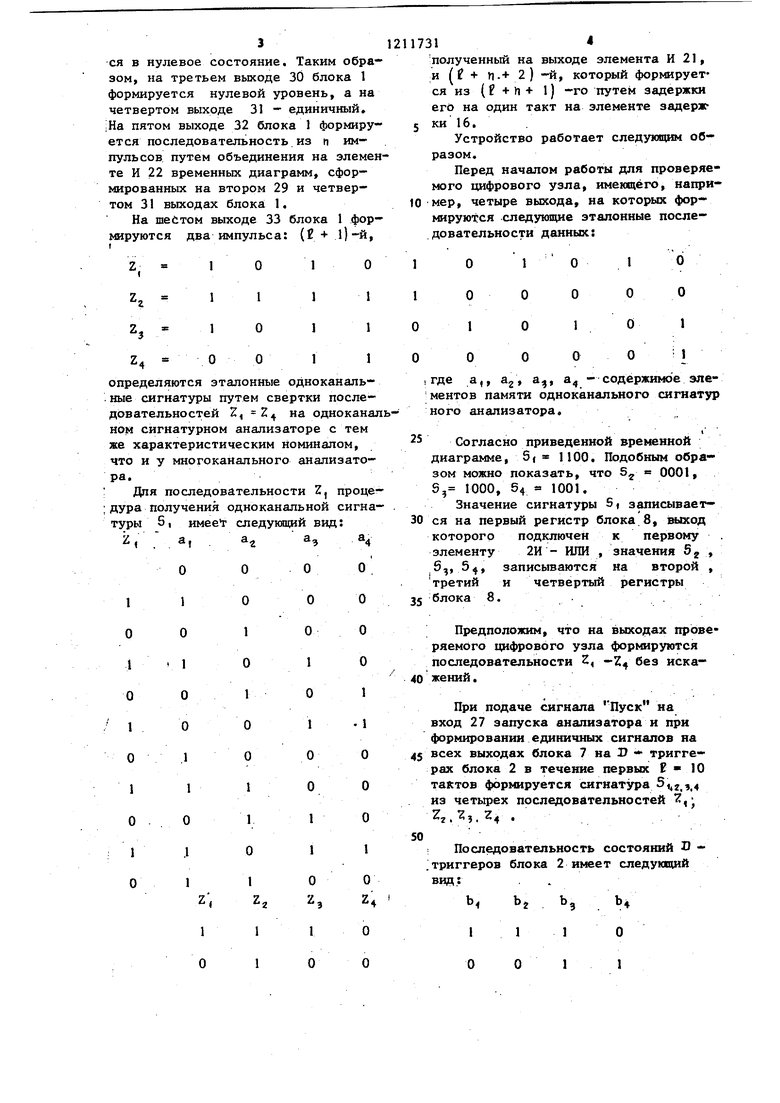

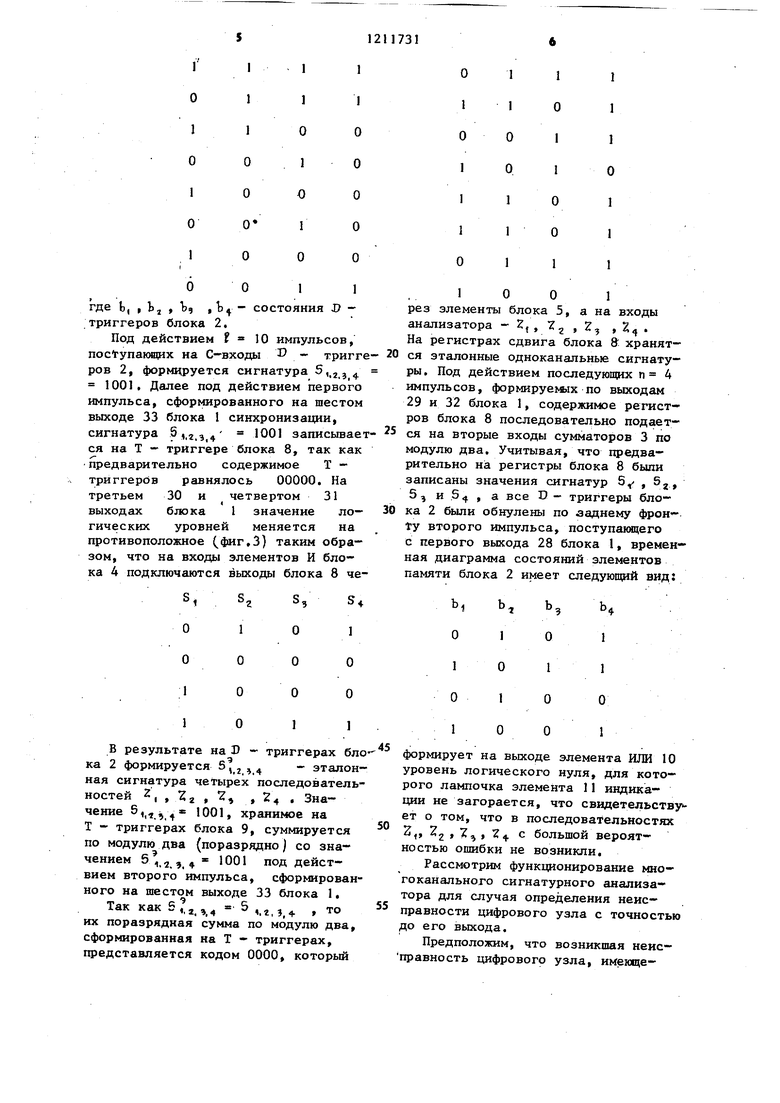

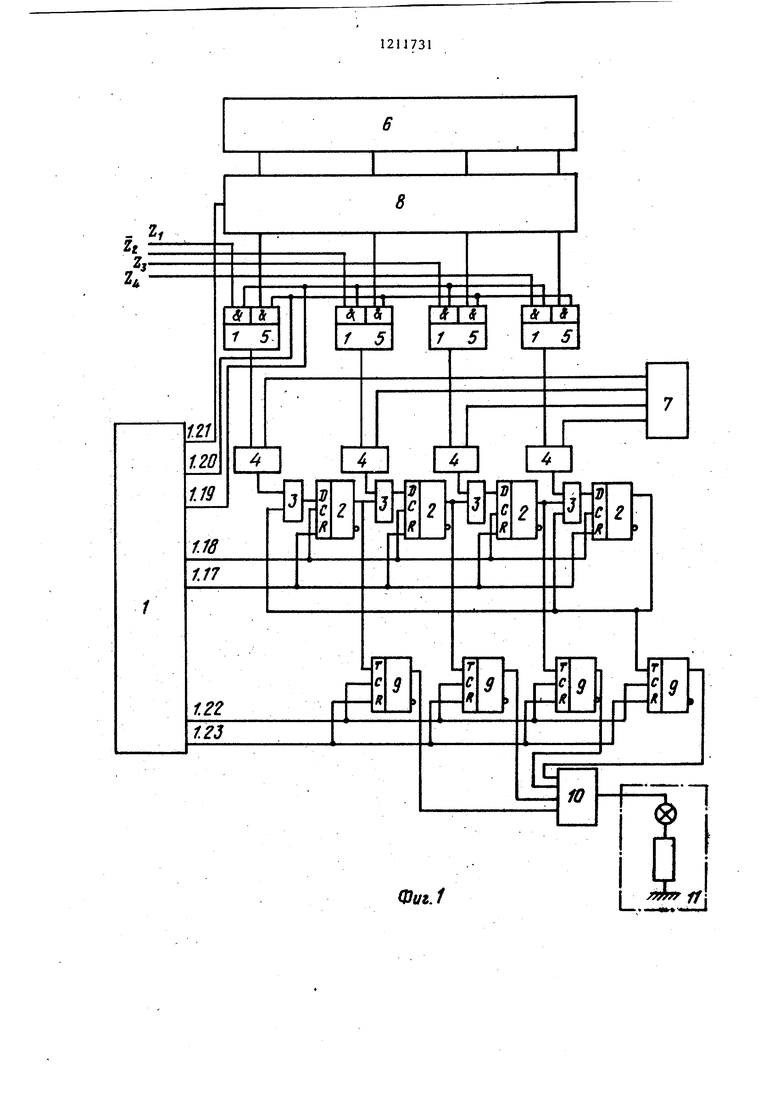

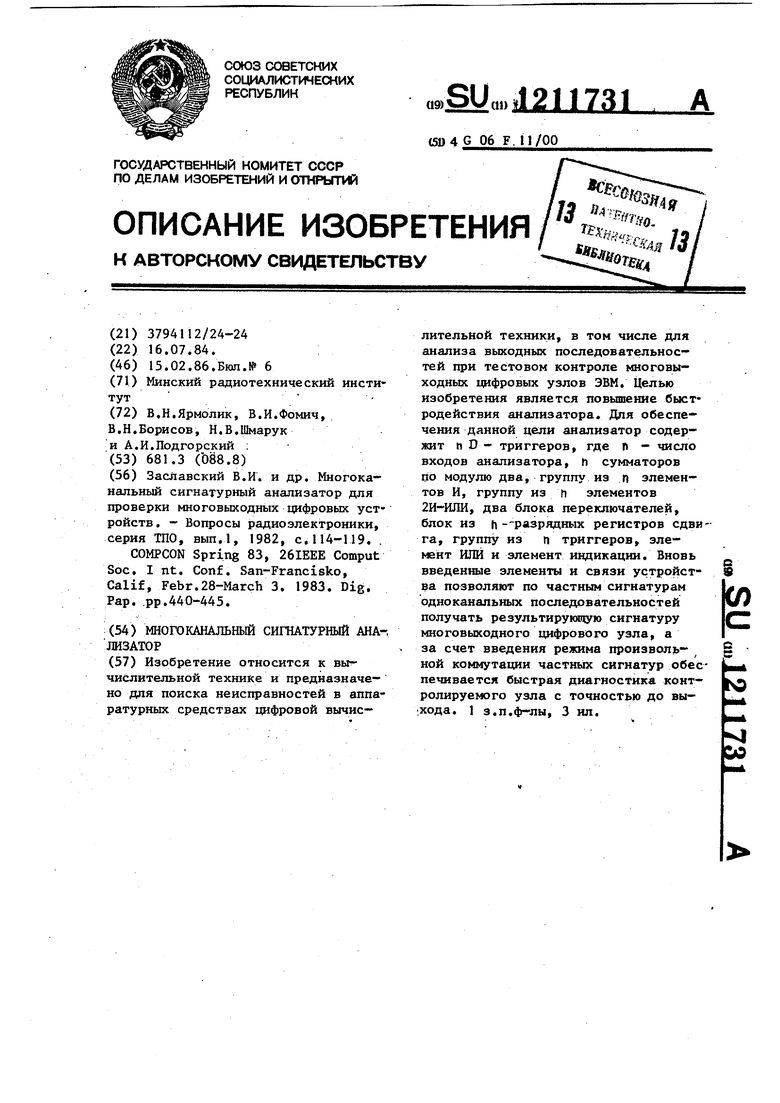

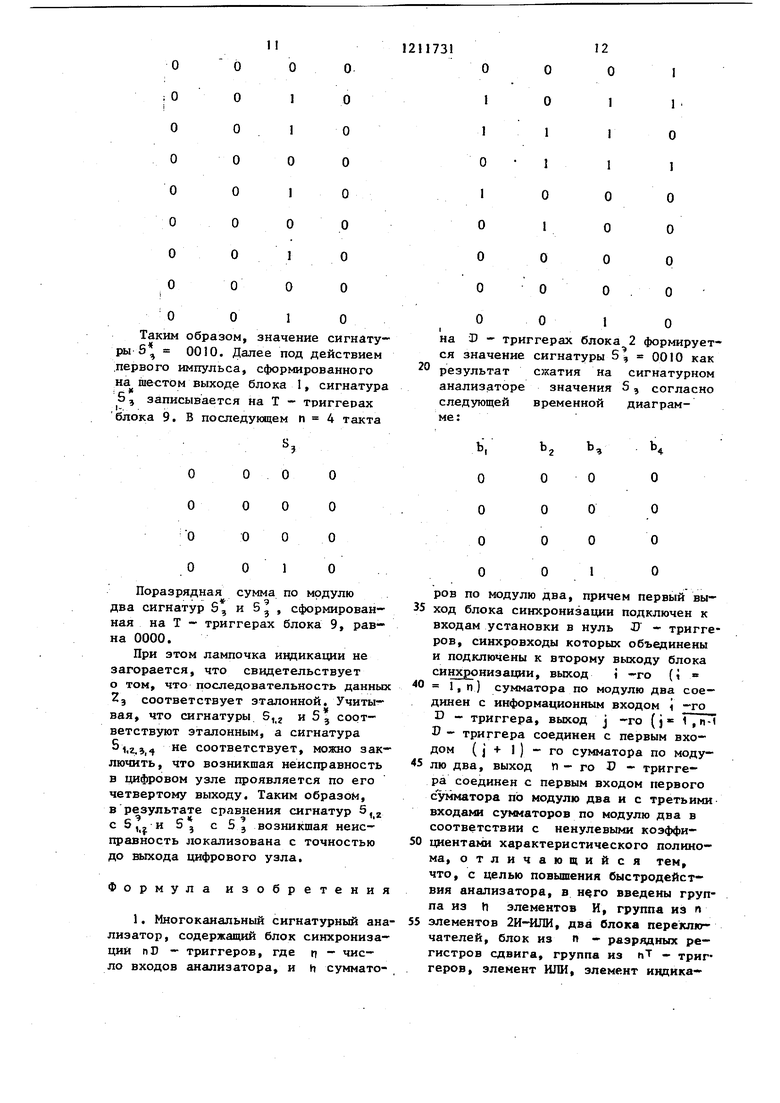

На фиг.1 изображена функциональ- на,я бхема предлагаемого многоканаль- ногб сигнатурного анализатора для П 4; на фиг,2 - функциональная схе- tia 0лока синхронизации многоканаль- ного сигнатурного анализатора; на фиг.З - временная диаграмма функционирования блока синхронизации.

Многоканальный сигнатурный анализатор содержит блок 1 синхронизации, nD - триггеров 2, п сумматоров 3 по модулю два, группу из п элементов И 4, группу из h элементов 2И-ИЛИ 5, блоки 6, 7 переключателей, блок 8 И - разрядных регистров сдвига, группу из п Т - триггер1ов 9, элемент ИЛИ 10 и элемент 11 индикации.

Блок синхронизации содержит генератор 12 тактовых импульсов, счетчик 13, три элемента 14,15,16 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17, пять элементов И ia-22, элемент И-НЕ 23, R8 - триггер 24, два элемента ИЛИ 25, 26, вход 27 запуска анализатора, а также семь выходов 28-34.

Количество D - триггеров 2 определяется максимальным количеством входов сигнатурного анализатора, т.е. величиной П . Количество элементов И 4, элементов 2И-ИЛИ 5, тумблеров блоков 6 и 7, регистров сдвига блока В, Т - триггеров 9, а также количество входов элемента ШШ 10 равняется п . Элемент 11 индикации состоит из лампочки индикации и ограничительного сопротивления, причем лампочка загорается при подаче на нее высокого потенциала,эквивалентного ЛО-; 50 гической единице. ,

На г.2 приведена функциональная схема блока 1 синхронизации, позволяющего организовать анализ последовательностей данных, состоящих из t 10 символов на сигнатурном; анализаторе, для которого deg(f t) « 4, т.е.и 4. Для других значе30

35

40

45

55

НИИ f и п блок 1 синхронизации отличается только количеством разрядов счетчика 14 и связями элементов 23 и 18, которые определяются кодами величин f и К) . Так, для 10 и П 4 связи элемента 23 с разрядами счетчика 13 определяются двоичным

5

0

5

0

0

5

0

5

5

кодом величины 10

дом 10 10

(|0)

т.е. ко(г)

Таким образом, для кода Е 10 10 на входы элемента 23 заводятся единичные выходы второго и четвертого разрядов счетчика 13 и нулевые выходы первого и третьего разрядов. Связи элемента 18 определяются двоичным кодом величины +п+1, для 2 10 и п 4 получаем код 1111, т,е. на входы элемента И 18 подключены единичные выходы всех четырех разрядов счетчика 13.

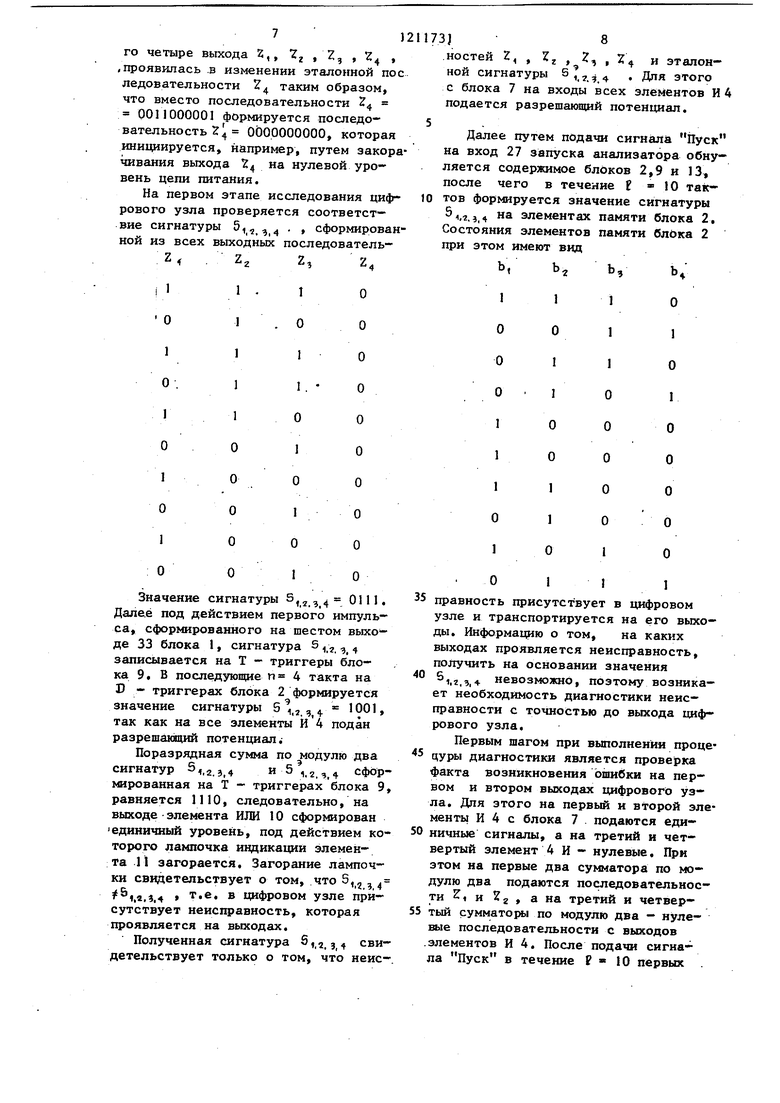

Блок 1 синхронизации формирует временную диаграмму на выходах 28-34 (фиг.З).

При подаче сигнала Пуск на вход 27 анализатора на выходе элемента .ИСКЛЮЧАЩЕЕ ШШ 17 формируется еди- ничный импульс, длительность которого определяется временем Cj задержки элемента 15 задержки. Через время С, Og на втором входе выходного-элемента ИЛИ-НЕ генератора 12 тактовых импульсов формируется нулевой сигнал, который инициирует его работу. Под действием единичного импульса, сформированного на выходе 34 блока синхронизации, счетчик 13 устанавливается в нулевое состояние, а R5 - триггер 24 устанавливается в единичное состояние. На втором .выходе 29 блока формируется последовательность из п + импульсов, причем на выходе генератора 12 тактовых импульсов формируется (h + t + 1)-й импульс. (е+ 1) -и импульс блокируется на элементе И 20 за счет нулевого уровня, сформированного на выходе элемента 23 под действием Е тактовых импульсов.

На третьем 30 и четвертом 31.выход ах блока 1 синхронизации формируются логические уровни соответственно единицы и нуля под действием одиночного импульса, сформированного на выходе элемента 17 ИСКЛЮЧАЮЩЕЕ ШШ 17. Под действием (f + l)-ro импульса, вьщеляемого на элементе 21, R5 - триггер 24 устанавливает

ся в нулевое состояние. Таким образом, на третьем выходе 30 блока 1 формируется нулевой уровень, а на четвертом выходе 31 - единичный, jHa пятом выходе 32 блока 1 формиру ется последовательность из п импульсов путем объединения на элементе И 22 временных диаграмм, сформированных на втором 29 и четвертом 31 выходах блока: 1.

На шейтом выходе 33 блока 1 формируются два импульса: (И+ ,

1

О

о

о

определяются эталонные одноканаль- ные сигнатуры путем свертки последовательностей Z, 2 на одноканал ном сигнатурном анализаторе с тем же характеристическим номиналом, что и у многоканального аналиэато- ра,

Для последовательности Z, проде- ; дура получения одноканальной сигна- туры 5, следующий вид:

о о 1 о 1

о о 1 1 о

Z,

2117314

полученный на выходе элемента И 21, и ( + Ц.+ 2) -и, который формируется из (f + И + 1) -го путем задержки его на один такт на элементе задерж- 5 ки 16,

Устройство работает следующим образом.

Перед началом работы для проверяемого цифрового узла, именадёго, напри- 10 мер, четыре выхода, на которых формируются следующие эталонные последовательности данных:

О

1

1

о

1

о

о

где а,, aj, а, а - содержимо е элементов памяти одноканального сигнатур ного анализатора,

Согласно приведенной временной

диаграмме, 5( 1100, Подобным образом можно показать, что 5 0001, S, 1000, 64 1001,

Значение сигнатуры S, записывает-

де- на- .

о 1

1 о о о 1

30

35

ся на первый регистр блока.8, выход которого подключен к первому элементу 2И - ИПИ , значения 5 записьгааются на второй третий и четвертый регистры блока 8. . .

Предположим, что на выходах прозе ряемого цифрового узла формируются последовательности 2, -Z без иска- 40 жений.

При подаче сигнала Пуск на вход 27 запуска анализатора и при формировании единичных сигналов на 45 всех выходах блока 7 на U - триггерах блока 2 в течение первых Е 10 тактов формируется сигнатура S,, из четырех последовательностей ,j

г. . 4

50

; Последовательность состояний - iтриггеров блока 2 имеет спедукщий вид:

О

О

1

О

О

триггеров блока 2. Под действием f

ОО11

где Ь, , bj , Ь, . Ь - состояния J3 -

10 импульсов,

D триггепос упающих на С-входы ров 2, формируется сигнатура S,j , 1001. Далее под действием первого импульса, сформированного на шестом выходе 33 блока 1 синхронизации, сигнатура 5,,2,3,4 1001 записьшает ся на Т - триггере блока 8, так как предварительно содержимое Т - триггеров равнялось 00000. На третьем 30 и четвертом 31 выходах блока 1 значение логических уровней меняется на противоположное (фиг.З) таким образом, что на вхо,цы элементов И блока 4 подключаются выходы блока 8 чеS, г 3 О 1 О 1

1

о

в результате на D - триггерах блока 2 формируется 5, j , - эталонная сигнатура четырех последовательностей 1,2, 4 . Значение 1,9,4 1001, хранимое на Т - триггерах блока 9, суммируется по модулю два (поразрядно) со значением 5 12 9 1001 под действием второго импульса, сформированного на шестом выходе 33 блока 1.

Так как 5,, 5 ,,г,, , то их поразрядная сумма по модулю два, сформированная на Т - триггерах, представляется кодом 0000, который

О

о

1

1

1 о о 1 рез элементы блока 5, а на входы анализатора -2,.Z,, ,2. На регистрах сдвига блока 8 хранят-

0 ся эталонные одноканальные сигнатуры. Под действием последующих п 4 импульсов, формируеьых по выходам 29 и 32 блока 1, содержимое регистров блока 8 последовательно подает5 ся на вторые входы сумматоров 3 по модулю два. Учитывая, что предварительно на регистры блока 8 были записаны значения сигнатур 5 . 5.

и

4

а все D - триггеры бло г

ка 2 были обнулены по заднему фрои-. ty второго импульса, поступающего с первого выхода 28 блока 1, временная диаграмма состояний элементов памяти блока 2 имеет следуюш;ий вид:

1

ь. ь.

О

1

1

О

О

формирует на выходе элемента ИЛИ 10 уровень логического нуля, для которого лампочка элемента 11 индикации не загорается, что свидетельству - ет о том, что в последовательностях И,, 2 , 7 , 4. с большой вероятностью ошибки не возникли.

Рассмотрим функционирование многоканального сигнатурного анализатора для случая определения неисправности цифрового узла с точностью до его выхода.

Предположим, что возникшая неис- правность цифрового узла, имеюще7)2

го четыре выхода 2,, Z ,Z, , Z , .проявилась .в изменении эталонной пос ледовательности таким образом, что вместо последовательности 4 0011000001 формируется последовательность 2 0000000000, которая инициируется, например, путем закорачивания выхода 4 S нулевой уровень цепи питания.

На первом этапе исследования цифрового узла проверяется соответствие сигнатуры 5,, .,ц . , сформированной из всех вькодных последователь- 2 . Z-, Z-i 2л

о

о

Значение сигнатуры S,j,4 0111. Далее под действием первого импульса, сформированного на шестом выходе 33 блока 1, сигнатура S i., , 4 записывается на Т - триггеры блока 9, В последующие п 4 такта на D - триггерах блока 2 формируется значение сигнатуры 5 у 94° 1001, так как на все элементы И 4 подан разрешающий потенциал.

Поразрядная сумма по модулю два сигнатур .3,4 и 5 ,.2,,4 сформированная на Т - триггерах блока 9, равняется 1110, следовательно, на выходе элемента ИЛИ 10 сформирован единичный уровень, под действием которого лампочка индикации элемента 11 загорается. Загорание лампочки свидетельствует о том, что 5«,2,э,4 ,4,.4 цифровом узле присутствует неисхфавность, которая проявляется на выходах.

Полученная сигнатура S ,,2. з, 4 свидетельствует только о том, что неис173J8

ностей Z, , Zj , , , Z и эталонной сигнатуры з г.4 « этого с блока 7 на входы всех элементов И 4 подается разрешающий потенциал.

5.

Далее путем подачи сигнала Пуск

на вход 27 запуска анализатора обнуляется содержимое блоков 2,9 и 13, после чего в течение Е 10 так- 10 тов формируется значение сигнатуры 5,,, на элементах памяти блока 2, Состояния элементов памяти блока 2 при этом имеют вид

Ь,

1

о

.

О 11 1

35 правность присутствует в цифровом узле и транспортируется на его выходы. Информацию о том, на каких выходах проявляется неисправность, получить на основании значения

40

1.г,з,4 невозможно, поэтому возникает необходимость диагностики неисправности с точностью до выхода цифрового узла.

Первым шагом при выполнении проце 5 цуры диагностики является проверка факта возникновения ошибки на первом и втором выходах цифрового узла. Для зтого на первый и второй элементы И 4 с блока 7 . подаются еди50 ничные сигналы, а на третий и четвертый элемент 4 И - нулевые. При этом на первые два сумматора по модулю два подаются последовательности 1 и г t а на третий и четвер55 тый сумматоры по модулю два - нулевые последовательности с выходов .элементов И 4. После подачи сигнала Пуск в течение Р « 10 первых .

тактов на элементах пямяти блока 2 формируются значения сигнатуры S, Z, Z,

100

1о о

100

1о о

1о о

о О о о

1 о 00

о

о

о

о

1

о

о -о

0000

Значение сигнатуры S, 0101. Далее под д ействием первого импульса, сформированного на шестом выходе блока 1, сигнатура 5, записывается на Т - триггеры блока 9. В последующие п 4 такта на 3 1 О О О Поразрядная сумма по модулю два сигнатур S,2 и сформированная на Т - триггерах блока 9, равна 0000, При этом лампочка индикации 11 не загорается, что свидетельствует о том, что последовательности данных 2, и %2 большой вероятностью соответствуют эталонным. Другими словами, неисправность, возникшая в цифровом узле по первым двум его выходам Z, к 1. , не выявляется. Учитывая тот факт, что сигнатура 5,, ие соответствует эталонной, а S, соответствует, можно заключить, что последовательность 3 и вместе отличны от эталонных.

Z,

О

о

1

о

1211731 О

Состояния элементов памяти при этом имеют вид

Ь, . Ь,Ь,

11ОО

0о1о

11о1

1о11

0000

0о00

1ооо о 1 о о

1-О -10

о1о1

триггерах блока 2 формируется значение сигнатуры 0101 как результат сжатия на сигнатурном , анализаторе значений S, и Sg согласно следукицей временной диаграмме:

п

ь, ь Ц ь,

0100 о 01 о

1

о

о

о 1 о 1

Для проверки соответствия последо вательиости Kj эталонной только не третьем выходе блока 7 формируется разрешакяций единичный потенциал. При этом на первый, второй и четвертый элементы блока 3 подаются нулевые последовательности, а на тре тий вход -. последовательность 2 .

После подачи сигнала .Пуск в течение Е 10 первых тактов на элемен- 50 тах памяти блока 2 формируется значение сигнатуры S 3 . При этом в общем случае 5,- / Sjji.J, и соответственно 5, 5j. Состояния элементов памяти блока 2 для случая получения 55 5, имеют следующие значения:

Ь, Ь, Ь, Ц

о

о

о

о

о

о

001О

О01О

00ОО

ОО1О

Таким образом, значение сигнату ры S 0010. Далее под действием первого импульса, сформированного на шестом выходе блока 1, сигнатура 5, записывается на Т - триггерах

блока 9. В последующем п

S,

4 такта

О

о

о

О

о

о

о

1

о

Поразрядная сумма по модулю два сигнатур S, и 5 , сформированная на Т - триггерах блока 9, равна 0000.

При этом лампочка индикации не загорается, что свидетельствует о том, что последовательность данных 2з соответствует эталонной. Учитывая, что сигнатуры 5,г и 5, соответствуют эталонным, а сигнатура i.z.j, ие соответствует, можно заключить, что возникшая неисправность в цифровом узле проявляется по его четвертому выходу. Таким образом, в результате сравнения сигнатур 5,j, cS,, и Sj с БЗ возникшая неисправность локализована с точностью до выхода цифрового узла.

Формула изобретения

1. Многоканальный сигнатурный анализатор, содержащий блок синхронизации nD - триггеров, где о число входов анализатора, и h сумматоО О 1 О I на И триггерах блока 2 формирует

ся значение сигнатуры 5 0010 как результат сжатия на анализаторе значения следующей временной

сигнатурном S, согласно диаграмме:

Ь,

О

0

О

I

О

ров по модулю два, причем первый вы35 ход блока синхронизации подключен к входам установки в нуль D - триггеров, синхровходы которых объединены и подключены к второму выходу блока синхронизации, выход i -го (

, п) сумматора по модулю два соединен с информационным входом j -го D - триггера, выход j -го (j « 1 , п-1 D - триггера соединен с первым входом (j + 1) - го сумматора по моду45 лю два, выход ч - го О - триггера соединен с первым входом первого с умматора по модулю два и с третьими входами сумматоров по модулю два в соответствии с ненулевыми коэффи50 циентами характеристического полиио- ма, отличающийся тем, что, с целью повышения быстродействия анализатора, в введены группа из h элементов И, группа из п

55 элементов 2И-ИЛИ, два блока переключателей, блок из п - разрядных регистров сдвига, группа из пТ - триггеров, элемент ШШ, элемент ичдика-

13

ции, причем первые входы первых и вторых элементов И всех элементов 2И-ИЛИ подключены соответственно к третьему и четвертому выходам блока управления, вторые входы,первых;эле ментов И элементов являются информационными входами аналиэато ра, а вторые входы вторых элементов И элементов 2И-ИЛИ соединены с соответствуюпщми выходами блока из п - разрядных регистров сдвига, информационные входы которого соединены с соответствукйдимн выходами первого блока переключателей, а управляющий вход блока из п - разрядных регистров сдвига соединен с пятым выходом блока синхрониза- . ции, выходы элементов 2И-ИЛИ сое- динены с первыми входами соответ т- вую1цих элементов И, .вторые входы которых подключены к соответствующим выходам второго блока переключателей, выход I - го элемента И подключен к второму входу - г сумматора по модулю два выходы D триггеров соединены с информационными входами, соотве т ствукпщх Т - триггеров, выходы которых сое- динены с входами элемента ИЛИ, выход которого подключен к входу элемента индикации синхровходы и входы .установки;

Т триггеров coes-

динены соответственно с шестым и седьмым выходами блока синхронизации,

2. Анализатор по п.1, о т л и - чающийся тем что блок сикх ронизащш срдержит генератор тактовых импульсов, счётчик, три элемента задержки, элемент ИСКЛЮЧАКН. ЩЕЕ ИЛИ, пять элементов И, элемент , R5 - триггер и два элемента ИЛИ, причем вход запуска анализатора соединен с первым входом зле ыекта ИСКЛЮЧАЮЩЕЕ ИЛИ, через первый элемент задержки с первым управляю

21173114

щим входом генератора тактовых импульсов и через второй элемент задержки с вторым входом элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход элемента.

5 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом сброса счетчика, S - входом RS - триггера, первым входом первого элемента ИЛИ и является сдвиговым выходом блока, прямые и инверсные .

10 разрядные выходы счетчика соединены с входами элемента И-НЕ в соответствии с двоичной записью числа 8 , где 6 - длина анализируемой последовательности, и с входами пер15 вого элемента И в соответствии с двоичной записью числа (+ h + 1) , где п - число входов анализатора, выход первого элемента И соединен с первым, входом второго элемента И

20 и с вторым управляющим входом генератора тактовых импульсов, выход . которого соединен с первыми входами третьего и четвертого эле 1ентов И и со счетным входом счетчика, вы25 ход элемента И-НЕ связан с вторым инверсным входом четвертого элемента И и вторым входом третьего элемента И, выход которого подключен к первому входу пятого элемента И,

30 через третий элемент задержки к второму входу вто.рого элемента И и является вторым выходом блока, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ,

35 R входом RS - триггера и первым входом второго элемента И, а выход второго элемента ИЛИ является шестым выходом блока, выход первого элемента ИЛИ является первым выхо-

40 дом блока, прямой выход RS - триггера является третьим выходом блока, инверсный выход R5 - триггера соединен с вторым входом пятого элемента И и является четвертым выхо4 дом блока, выход пятого элемента И является пятым выходом блока.

Фиг.1

Фп.г

«7 2В

|

29

JO

Jf

Редактор .Н.Швцдкая

Составитель С.Старшхин

Техред Т.Тулик Корректор М.Самборская

Заказ 641/53Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал 111Ш Патент, г.Ужгород, ул Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1283772A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор | 1985 |

|

SU1381510A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор с перестраиваемой структурой | 1983 |

|

SU1120334A1 |

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

Изобретение относится к вы числительной технике и предназначено для поиска неисправностей в аппаратурных, средствах цифровой вычислительной техники, в том числе для анализа выходных последовательностей при тестовом контроле многовы- ходньк цифровых узлов ЭВМ. Целью изобретения является повышение быстродействия анализатора. Для обеспечения данной цели анализатор содержит и D - триггеров, где п - число входов анализатора, п сумматоров по модулю два, группу из п элементов И, группу из fi элементов 2И-ИЛИ, два блока переключателей, блок из h - разрядных регистров сдвига, группу из п триггеров, элемент ШШ и элемент индикации. Вновь введенные элементы и связи устройства позволяют по частным сигнатурам одноканальных последовательностей получать результирукщуп снгнатуру многовыходного цифрового узла, a за счет введения режима произвольной коммутации частных сигнатур обеспечивается быстрая диагностика контролируемого узла с точностью до вы- ;хода. 1 з.п.ф-лы, 3 ил. СО

| Заславский В.И | |||

| и др | |||

| Многоканальный сигнатурный анализатор для проверки многовькодных цифровых устройств | |||

| - Вопросы радиоэлектроники, серия ТПО, ВЫП.1, 1982, с.114-119 | |||

| Пуговица | 0 |

|

SU83A1 |

| I nt | |||

| Conf | |||

| San-Francisko, Calif, Febr.28-March 3 | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Dig, Pap | |||

| Способ обогащения руд | 1915 |

|

SU440A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-16—Подача