(цих элементов, третий и четвертьй выходы которого соединены соответственно с первым и вторым входами второго блока согласующих элементов первый выход которого соединен с первым входом селектора длительности импульсов, с первым входом второго блока сравнения и с первым входо третьего регистра, вьосод которого соединен с первым входом второго элемента И, выход которого соединен с третьим входом второго блока согласующих элементов, второй выход которого соединен с вторым входом третьего регистра, с первым входом третьего элемента И, с вторым входом селектора длительности импульсо с первым входом второго счетчика, с первым входом шифратора адреса, выход которого соединен с вторьот входом второго блока сравнения, выход которого соединен с первым входом третьего триггера, выход которого соединен с первым входом четвертого триггера, выход которого соединен с вторыми входами второго и третьего элементов И, с первым входом второго блока памяти, входы группы которого соединены с выходами группы третьего регистра, первый выход

селектора длительности импульсов соединен с вторым входом шифратора адреса, с вторым входом третьего триггера, с вторым входом второго счетчика и с вторым входом четвертого триггера, третий вход которого соединен с выходом второго счетчика, второй выход селектора длительности импульсов соединен с вторым входом второго блока памяти, выходы которого соединены с входами третьего блока согласующих элементов, выход третьего элемента И соединен с вторым входом второго блока согласующих элементов, третий и четвертый выходы которого соединены соответственно с третьим и четвертым входами первого блока согласующих элементов, выходы третьего блока согласукяцих элементов являются выходами группы устройства, выход втор.ого триггера является первым выходом устройства, третий и четвертый выходы первого блока согласующих элементов являются соответственно вторым и третьим выходами устройства, третий и четвертый входы первого блока согласующих эле ментов являются соответственно вторым и третьим входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для автоматической регистрации радиотелеграфных сигналов | 1983 |

|

SU1092747A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

УСТРОЙСТВО-7ЩЯ ВЫВОДА ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее первый блок памяти, первый регистр, формирователь импульсов, первый, второй, третий элементы И и первый блок согласующих элементов, выходы первого блока памяти соединены с входами группы первого регистра, вход которого соединен с первым выходом формирователя импульсов, второй выход которого соединен с первьм входом первого элемента И, входы группы первого блока памяти являются входами группы устройства, вход блока памяти является первым входом устройства, отличающееся тем, что, с целью повьшения его надежности путем увеличения достоверности передаваемой информации, в него введены второй и третий, зегистры, первый и второй счетчики, первьй и второй блоки в сравнении, щифра;тор адреса, селектор длительности импульсов, второй блок памяти, второй и третий блоки согласукяшх элементов, первый, второй, третий и четвертый триггеры, первый, второй и третий элементы ИЛИ, вьсходы первого блока памяти соедине ны с входами группы второго регистра, выход которого соединен с первым входом первого блока сравнения, выход которого соединен с первьп- входом первого триггера, выход которого соединен с вторым входом первого элемента И и с первым входом первого счетчика, первый выход которого соединен с первым входом второго триггера, второй вход которого соединен с входом первого блока памяти, с вторым входом первого счетчика и с первым входом первого элемента ИЛИ, выход которого соединен с вхо(Л дом формирователя импульсов, выход первого регистра соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго регистра, с первым входом треО1 тьего элемента ИЛИ и с вторым входом первого триггера, третий вход кото рого соединен с первым выходом первого блока, согласующргх элементов «|аь и вторым входом второго регистра, 4 второй выход первого счетчика соединен с вторым входом первого элемента ИЛИ, выход второго элемента ИЖ соединен с первым входом первого блока согласующих элементов, второй вход которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с первым выходом формирователя импульсов, второй вход первого блока сравнения соединен с вторым выходом первого блока согласую

I

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления для вьщачи цифровых управляющих сигналов.

. Известно устройство для вывода данньк из процессора, содержащее блоки сопряжения, управления, согласования регистр обмена, генератор тактовой частоты, блок задания режима вьюода, причем входы устройства связаны с первь1ми входами блока управления и регистра обмена, выход которого подключен к входам блока сопряжения и первому вхбяу блока задания режима вывода, выход генератора тактовой частоты соединен с вторым входом блока управления, выход которого подключён к вторым входам регистра обмена и блоку задания режима вьгоода,

вькод блока режима вьшода соединен с третьим входом блока управления, выходы блоков сопряжения подключены к входам блока согласования, выходы которого являются выходами устройства Ci.

Недостатком устройства является низкая достоверность передаваемой информация .

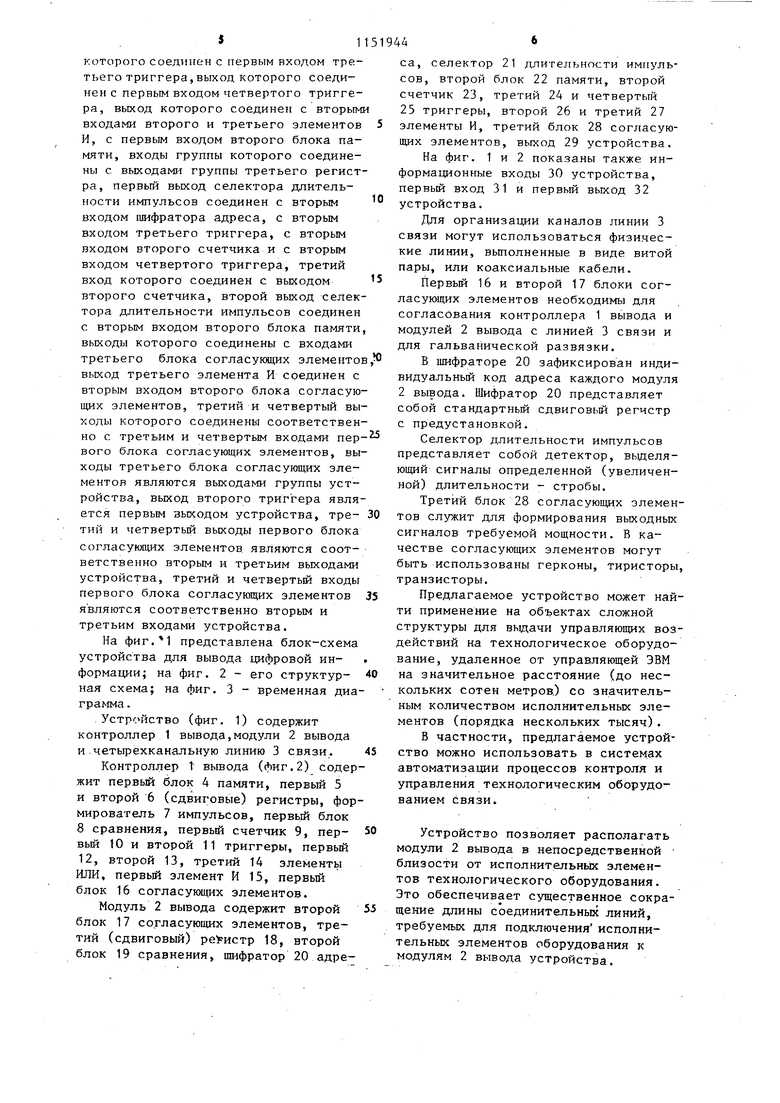

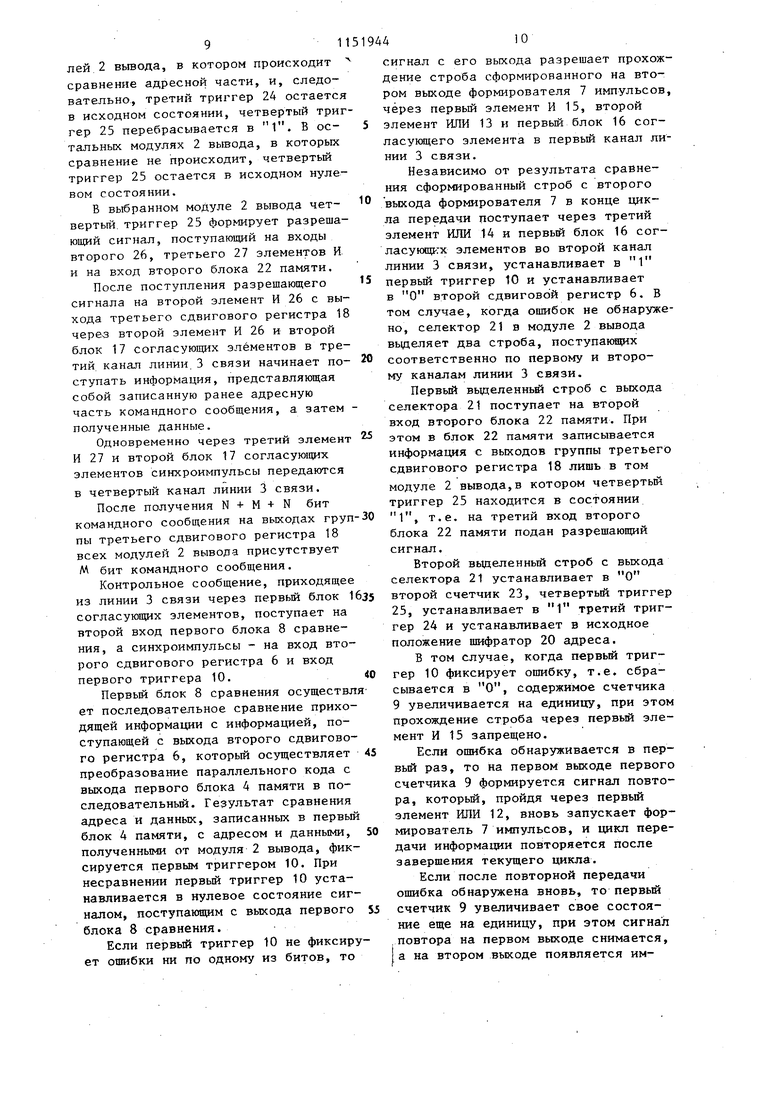

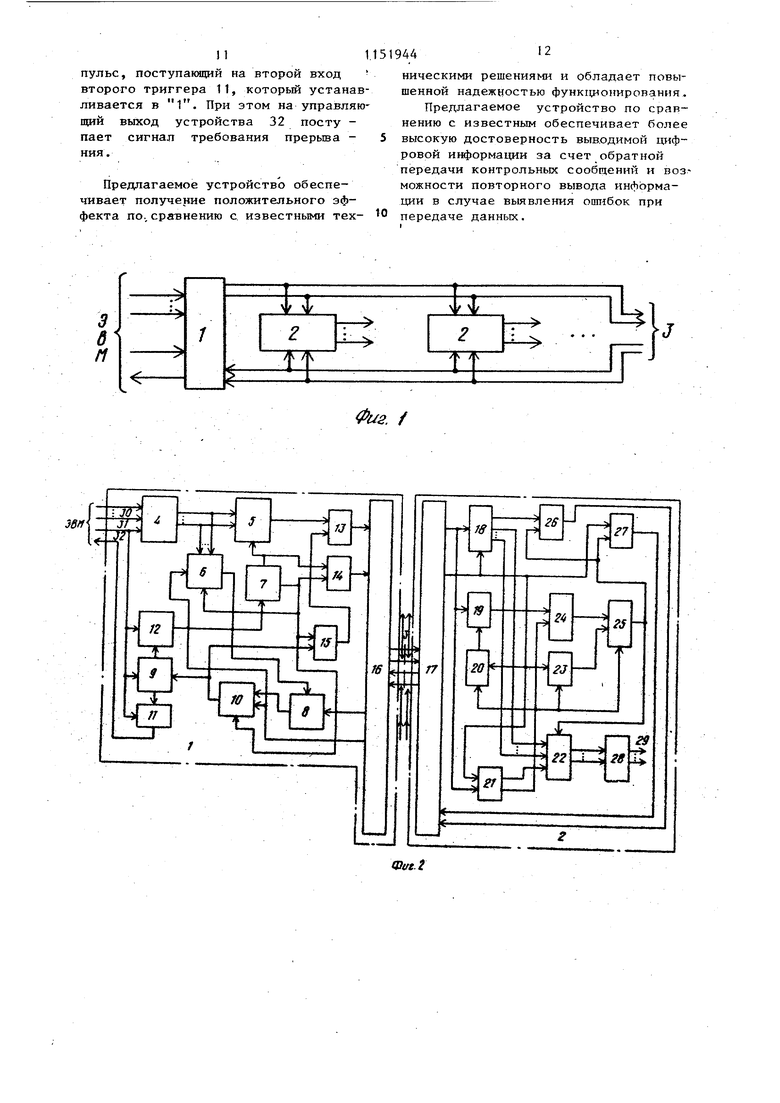

Наиболее близким по технической сущности к предлагаемому является устройство для вьгаода информации, 00 держащее буферную память, информационный вход которой является входом устройства, а информационные выходы соединены с соответствующими информахщонными входами регистра, формирователь импульсов, блок согласования, выход которого является выходом устройства, блок памяти управления, три 31 элемента И и труппу элементон И, при чем первые вькоды формирователя импульсов и блока памяти управления подключены к соответствующим входам первого элемента И, выходом соединен ного с управляющим входом буферной памяти, вторые выходы - к соответствующим входам второго элемента И, выходом соединенного с управляющим входом блока памяти управления, а третьим выходы - к соответствуюпщм входам третьего элемента И, выходом соединенного с первым управляющим вхо дом регистра, выходы которого подклю чены к первым входам соответствующих элементов И группы, а второй управля ющий вход - к четвертому выходу блок памяти управления, информационный вход которой соединен с входом устройства, пятый выход - с вторыми входами элементов И группы, а выходы группы - с выходами группы блока сог ласования, соответствующие входы которого подключены к выходам элементов И группы . Недостатками известного устройства являются низкая достоверность передаваемой информации и отсутствие программно-аппаратных средств контро ля работоспособности устройства. . Цель иизобретения - повышение наj дежности устройства путем повьшения 1 достоверности передаваемой информации. Поставленная цель достигается тем, что в устройство для вывода цифровой информации, содержащее первый блок памяти, первый регистр, формирователь импульсов, первый, второй, третий элементы И и первый блок согласугадих элементов, выходы первого блока памяти соединены с входами группы первого регистра, вход которого соединен с первым выходом формирователя импульсов, второй выход которого соединен с первым входом первого элемента И, входы группы первого блока памяти являются входами группы устройства, вход блока памяти является первым входом устройства, введены второй и третий регистры, первый и .второй счетчики, первый и второй блоки сравнения, шифратор адреса, селектор длительности импульсов, второй блок а памяти, второй и третий блоки согласующих элементов, первый, второй, третий и четвертый триггеры первый, второй и третий элементы ИЛИ 44 выходы первого блока памяти соедпиепы с входами группы второго рогчетра, вьгход которого соединен с nopi3,iM входом .первого блока сравнентя, выхол которого соединен с первым входом первого триггера, выход которого соединен с вторым входом первого элемента И и с первым входом первого сметчика, первый выход которого соединен с первым входом второго трипсрл, второй вход которого соединен с входом первого блока памяти, с. вторым входом первого счетчика и с перным входом первого элемента ИЛИ, выход которого coeди eн с вх-одом форт трователя импульсов, выход первого регистра соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго регистра, с первым входом третьего элемента ИЛИ и с- вторым входом первого триггера, третий вход которого соединен с первым выходом первого блока согласующих элементов и вторым входом второго регистра, второй выход первого счетчика соединен с вторым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом первого блока согласующих элементов, второй вход которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с первым выходом формирователя импульсов, второй вход первого блока сравнения соединен с вторым выходом первого блока согласующих элементов, третий и четвертый выходы которого соединены соответственно с первым и вторым входами второго блока согласую1Щ1х элементов, первый выход которого соединен с первым входом селектора длительности импульсов, с первым входом второго блока сравнения и с первым входом третьего регистра, выход которого соединен с первым входом второго элемента И, выход которого соединен с третьим входом второго блока согласующих элементов, второй выход которого соединен с вторым входом третьего регистра, с первым входом третьего элемента И, с вторым входом селектора длительности импульсов, с первым входом второго счетчика, с первым входом шифратора адреса, выход которого соединен с вторым входом второго блока сравнения, выход которого соединен с первым входом третьего триггера,выход которого соединен с первым входом четвертого триггера, выход которого соединен с вторым входами второго и третьего элементов И, с первым входом второго блока памяти, входы группы которого соединены с выходами группы третьего регист ра, первый выход селектора длитель(юсти импульсов соединен с вторым входом (цифратора адреса, с вторым входом третьего триггера, с вторым входом второго счетчика и с вторым входом четвертого триггера, третий вход которого соединен с выходом второго счетчика, второй выход селек тора длительности импульсов соединен с вторым входом второго блока памяти выходы которого соединены с входами третьего блока согласукщих элементо выход третьего элемента И соединен с вторым входом второго блока согласую щих элементов, третий и четвертый вы ходы которого соединены соответствен но с третьим и четвертым входами пер вого блока согласующих элементов, вы ходы третьего блока согласующих элементов являются выходами группы устройства, выход второго триггера явля ется первым выходом устройства, третий и четвертый выходы первого блока согласующих элементов являются соответственно вторым и третьим выходами устройства, третий и четвертьй входы первого блока согласующих элементов являются соответственно вторым и третьим входами устройства. На фиг.1 представлена блок-схема устройства для вывода цифровой информации; на фиг. 2 - его структурная схема; на фиг. 3 - временная диа грамма . Устройство (фиг. 1) содержит контроллер 1 вывода,модули 2 вывода и.четырехканальную линию 3 связи. Контроллер 1 вывода (Лиг.2) содер жит первьй блок 4 памяти, первый 5 и второй 6 (сдвиговые) регистры, фор мирователь 7 импульсов, первьй блок 8 сравнения, первый счетчик 9, первый 10 и второй 11 триггеры, первый 12, второй 13, третий 14 элементы ИЛИ, первьй элемент И 15, первьй блок 16 согласующих элементов. Модуль 2 вывода содержит второй блок 17 согласующих элементов, третий (сдвиговый) pelFHCTp 18, второй блок 19 сравнения, шифратор 20 адреселектор 21 длительности импуль., второй блок 22 памяти, второй счетчик 23, третий 24 и четвертый 25 триггеры, второй 26 и третий 27 элементы И, третий блок 28 согласующих элементов, выход 29 устройства. На фиг. 1 и 2 показаны также информационные входы 30 устройства, первьй вход 31 и первый выход 32 устройства. Для организации каналов линии 3 связи могут использоваться физические линии, вьтолненные в виде витой пары, или коаксиальные кабели. Первьй 16 и второй 17 блоки согласующих элементов необходимы для согласования контроллера 1 вывода и модулей 2 вывода с линией 3 связи и для гальванической развязки. В шифраторе 20 зафиксирован индивидуальньй код адреса каждого модуля 2 вывода. Шифратор 20 представляет собой стандартньй сдвиговьй регистр с предустановкой. Селектор длительности импульсов представляет собой детектор, вьщеляюш;ий сигналы определенной (увеличенной) длительности - стробы. Третий блок 28 согласующих элементов служит для формирования выходных сигналов требуемой мощности. В качестве согласующих элементов могут быть использованы герконы, тиристоры, транзисторы. Предлагаемое устройство может найти применение на объектах сложной структуры для вьщачи управляющих воздействий на технологическое оборудование, удаленное от управляющей ЭВМ на значительное расстояние (до нескольких сотен метров.) со значительным количеством исполнительных элементов (порядка нескольких тысяч). В частности, предлагаемое устройство можно использовать в системах автоматизации процессов контроля и управления технологическим оборудованием связи. Устройство позволяет располагать модули 2 вывода в непосредственной близости от исполнительньЬс элементов технологического оборудования. Это обеспечивает существенное сокращение длины соединительных линий, требуемых для подключения исполнительных элементов оборудования к модулям 2 вывода устройства.

7

Контроллер 1 вывода устройства соединяется с помощью единой четьгр-ехканальнойлинии 3 связи с модулями 2 вывода, располагаемыми в местах,требуемых для целей контроля и управления .

Устройство взаимодействует с ЭВМ в асинхронном режиме, что достигается применением первого блока А памяти.

Устройство осуществляет аппаратный контроль передаваемой информации путем анализа контрольных сообщений, формируемых адресованным модулем 2 вывода, и повторной передачей командного сообщения в линию связи в случае несоответствия контрольного сообщения требуемому. Выдача повторного командного сообщения осуществляется без участия ЭВМ. При вторичном поступлении некорректного сообщения устройство формирует требование прерывания ЭВМ и дальнейший алгоритм взаимодействия устройства с ЭВМ-определяется последней.

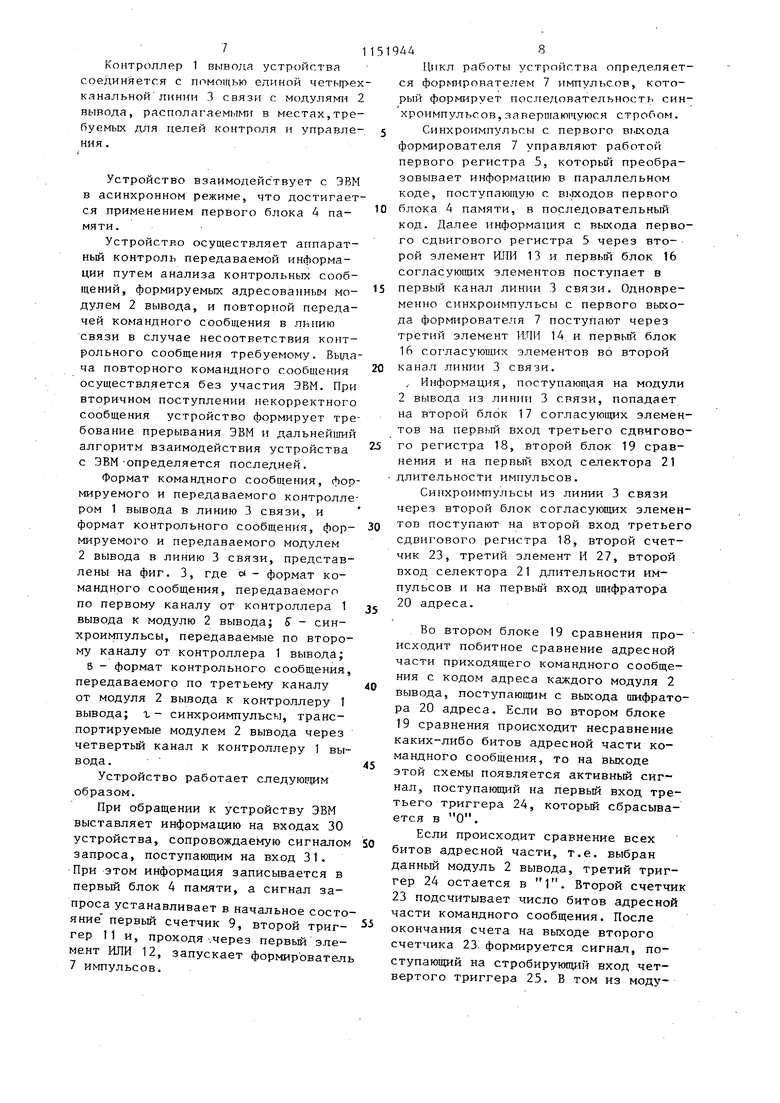

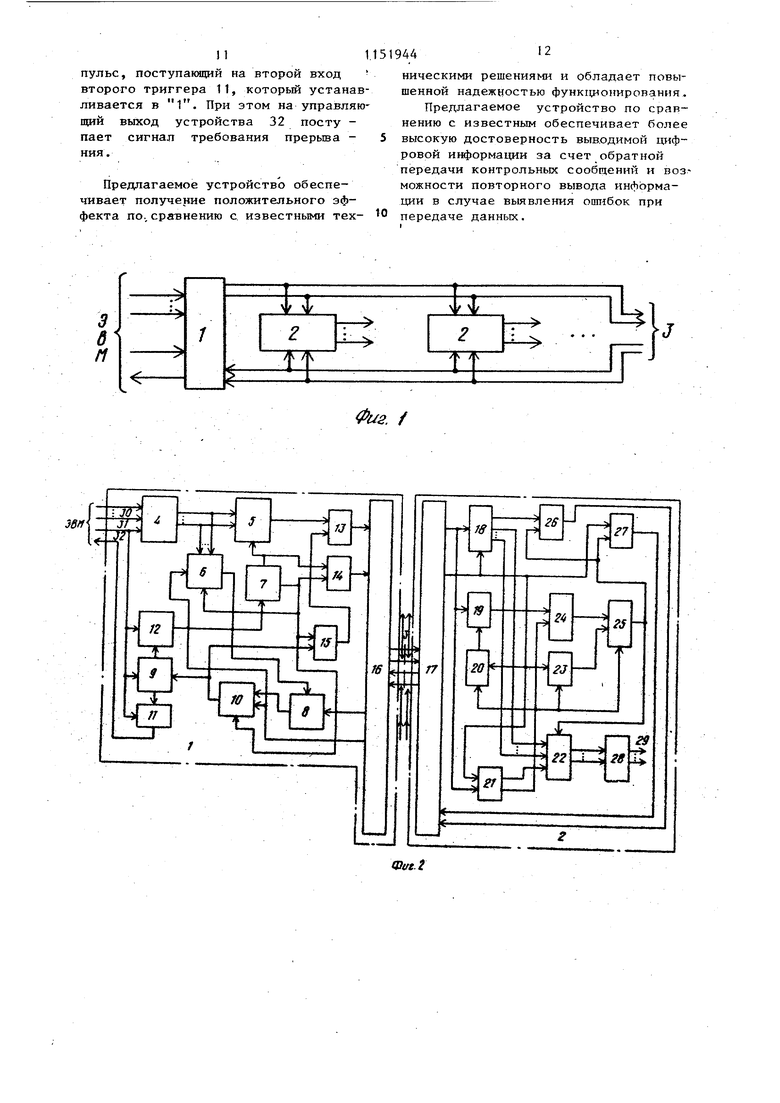

Формат командного сообщения, формируемого и передаваемого контроллером 1 вывода в линию 3 связи, и формат контрольного сообщения, формируемого и передаваемого модулем 2 вывода в линию 3 связи, представлены на фиг. 3, где oi - формат командного сообщения, передаваемого по первому каналу от контроллера 1 вывода к модулю 2 вывода; 5 - синхроимпульсы, передаваемые по второму каналу от контроллера 1 вывода;

6 - формат контрольного сообщения, передаваемого по третьему каналу от модуля 2 вывода к контроллеру 1 вывода; г- синхроимпульсы, транспортируемые модулем 2 вывода через четвертый канал к контроллеру 1 вывода.

Устройство работает следующим образом.

При обращении к устройству ЭВМ выставляет информацию на входах 30 устройства, сопровождаемую сигналом запроса, поступающим на вход 31. При этом информация записывается в первый блок 4 памяти, а сигнал запрос а устанавливает в начальное состояние первый счетчик 9, второй триггер 11 и, проходя-.через первьй элемент ИЛИ 12, запускает формирователь 7 импульсов.

519Д48

Цикл работы устройства определяется формирователем 7 импульсов, который формирует последовательность синхроимпульсов,завершающуюся стробом. 5 Синхроимпульсы с первого В1.кода формирователя 7 управляют работой первого регистра 5, которьй преобразовывает информацию в параллельном коде, поступающую с В1.гходов первого

10 блока 4 памяти, в последовательный код. Далее информация с выхода первого сдвигового регистра 5 через второй элемент ИЛИ 13 и первый блок 16 согласую цих элементов поступает в

5 первый канал линии 3 связи. Одновременно синхроимпульсы с первого выхода формирователя 7 поступают через третий элемент ИЛИ 14 и первый блок 16 сотласующих элементов во второй

0 канал линии 3 связи.

, Информация, поступающая на модули 2 вывода из линии 3 связи, попадает на второй блок 17 согласующих элементов на первьй вход третьего сдвчгово5 го регистра 18, второй блок 19 сравнения и на первьй вход селектора 21 . длительности импульсов.

Синхроимпульсы из линии 3 связи через второй блок согласующих элеменд тов поступают на второй вход третьего сдвигового регистра 18, второй счетчик 23, третий элемент И 27, второй вход селектора 21 длительности импульсов и на первьй вход ишфратора 20 адреса.

Во втором блоке 19 сравнения происходит побитное сравнение адресной части приходящего командного сообщения с кодом адреса каждого модуля 2 вывода, поступающим с выхода шифратора 20 адреса. Если во втором блоке 19 сравнения происходит несравнение каких-либо битов адресной части командного сообщения, то на выходе этой схемы появляется активньй сигнал, поступающий на первьй вход третьего триггера 24, которьй сбрасывается в О.

Если происходит сравнение всех битов адресной части, т.е. выбран данньй модуль 2 вывода, третий триггер 24 остается в 1. Второй счетчи 23 подсчитывает число битов адресной части командного сообщения. После окончания счета на выходе второго счетчика 23. формируется сигнап, поступающий на стробирующий вход четвертого триггера 25. В том из моду91пей 2 вьгеода, в котором происходит сравнение адресной части, и, следовательно, третий триггер 24 остается в исходном состоянии, четвертый триг гер 25 перебрасывается в 1. В остальных модулях 2 вывода, в которых сравнение не происходит, четвертый триггер 25 остается в исходном нулевом состоянии. В выбранном модуле 2 вывода четвертый триггер 25 формирует разрешающий сигнал, поступающий на входы второго 26, третьего 27 элементов И и на вход второго блока 22 памяти. После поступления разрешающего сигнала на второй элемент И 26 с выхода третьего сдвигового регистра 18 чере-з второй элемент И 26 и второй блок 17 согласующих элементов в третий канал линии 3 связи начинает поступать информация, представляющая собой записанную ранее адресную часть командного сообщения, а затем полученные данные. Одновременно через третий элемент И 27 и второй блок 17 согласующих элементов синхроимпульсы передаются в четвертый канал линии 3 связи. После получения N + М + N бит командного сообщения на выходах груп пы третьего сдвигового регистра 18 всех модулей 2 вывода присутствует М бит командного сообщения. Контрольное сообщение, приходящее из линии 3 связи через первый блок согласующих элементов, поступает на второй вход первого блока 8 сравнения, а синхроимпульсы - на вход второго сдвигового регистра 6 и вход первого триггера 10. Первьй блок 8 сравнения осуществл ет последовательное сравнение приходящей информации с информацией, поступающей с выхода второго сдвигового регистра 6, который осуществляет преобразование параллельного кода с выхода первого блока 4 памяти в последовательный. Результат сравнения адреса и данных, записанных в первый блок 4 памяти, с адресом и данными, полученными от модуля 2 вывода, фиксируется первьм триггером 10. При несравнении первьш триггер 10 устанавливается в нулевое состояние сигналом, поступающим с выхода первого блока 8 сравнения. Если первый триггер 10 не фиксиру ет ошибки ни по одному из битов, то 4 сигнал с его выхода разрешает прохождение строба сформированного на втором выходе формирователя 7 импульсов, через первый элемент И 15, второй элемент ИЛИ 13 и первьш блок 16 согласующего элемента в первый канал линии 3 связи. Независимо от результата сравнения сформированный строб с второго выхода формирователя 7 в конце цикла передачи поступает через третий элемент Ш1И 14 и первый блок 16 согласуняцргх элементов во второй канал линии 3 связи, устанавливает в 1 первый триггер 10 и устанавливает в О второй сдвиговой регистр 6. В том случае, когда ошибок не обнаружено, селектор 21 в модуле 2 вывода вьщеляет два строба, поступающих соответственно по первому и второму каналам линии 3 связи. Первый выделенньй строб с выхода селектора 21 поступает на второй вход второго блока 22 памяти. При этом в блок 22 памяти записывается информация с вькодов группы третьего сдвигового регистра 18 лишь в том модуле 2 вывода,в котором четвертый триггер 25 находится в состоянии 1, т.е. на третий вход второго блока 22 памяти подан разрешающий сигнал. Второй выделенный строб с выхода селектора 21 устанавливает в О второй счетчик 23, четвертый триггер 25, устанавливает в 1 третий триггер 24 и устанавливает в исходное положение шифратор 20 адреса. В том случае, когда первый триггер 10 фиксирует ошибку, т.е. сбрасывается в О, содержимое счетчика 9 увеличивается на единицу, при этом прохождение строба через первый элемент И 15 запрещено. Если ошибка обнаруживается в первый раз, то на первом выходе первого счетчика 9 формируется сигнал повтора, который, пройдя через первый элемент ИЛИ 12, вновь запускает формирователь 7 импульсов, и цикл передачи информации повторяется после завершения текущего цикла. Если после повторной передачи ошибка обнаружена вновь, то первьй счетчик 9 увеличивает свое состояние еще на единицу, при этом сигнал повтора на первом выходе снимается, а на втором выходе появляется имnпульс, поступакиций на второй вход второго триггера 11, который устана ливается в 1. При этом на управля щий выход устройства 32 посту пает сигнал требования прерьша кия. Предлагаемое устройство обеспечивает получение положительного эффекта по., сравнению с известными тех

US. / 44 ническими решениями и обладает повышенной надежностью функционирования. Предлагаемое устройство по сравнению с известным обеспечивает более высокую достоверность выводимой цифровой информации за счет обратной передачи контрольных сообщений и возможности повторного вывода информации в случае выявления опшбок при передаче данных.

.Проил ллнь№

Affflee affffAffЛгммь/е CmpoS

1 I I---I I I--TTT

a

Г...| ртгп

./v - , л- V- - -V

I ; { i i

NH

Фаг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-03—Подача