Изобретение относится к вычислительной технике, в частности - к системе программного контроля и может быть использовано для тестовой проверки цифровьгх блоков.

Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования тестов для контроля блоков различной структурной организации.

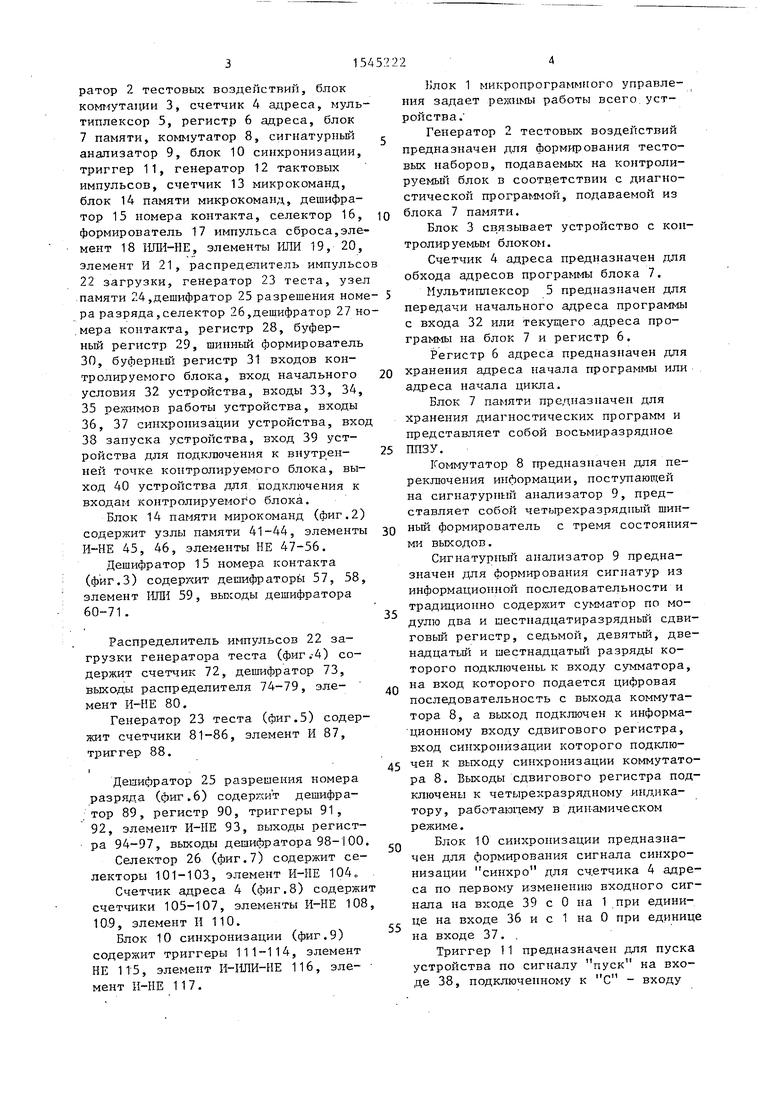

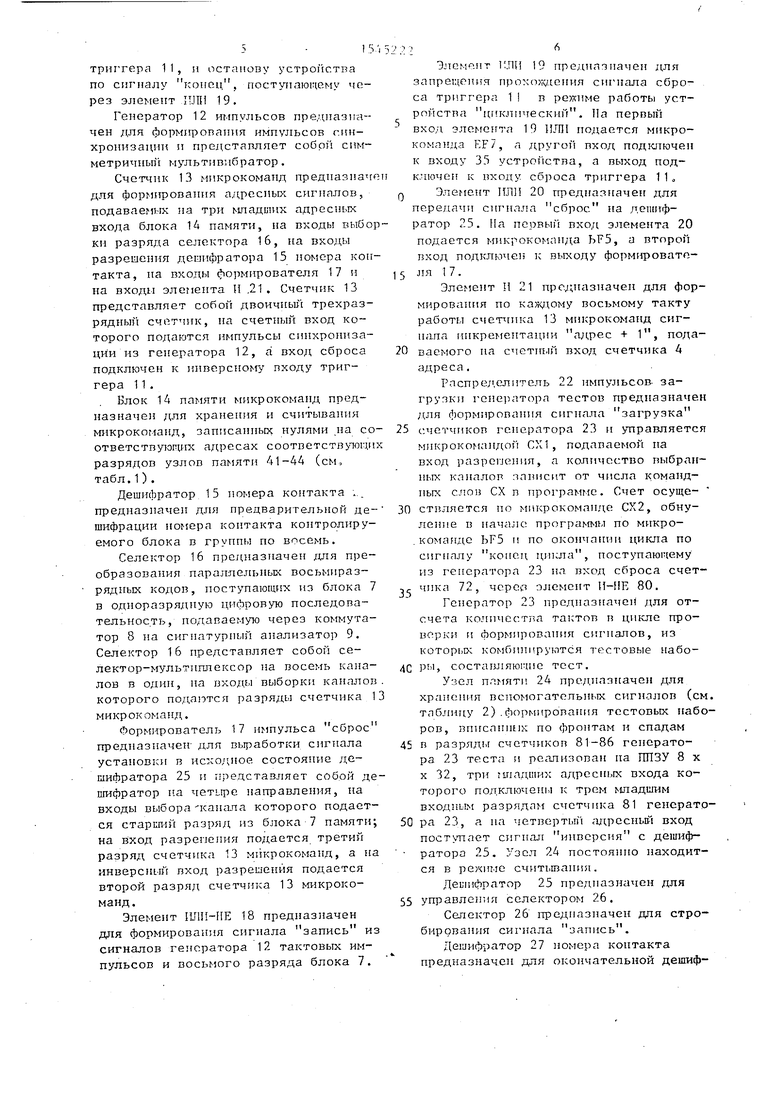

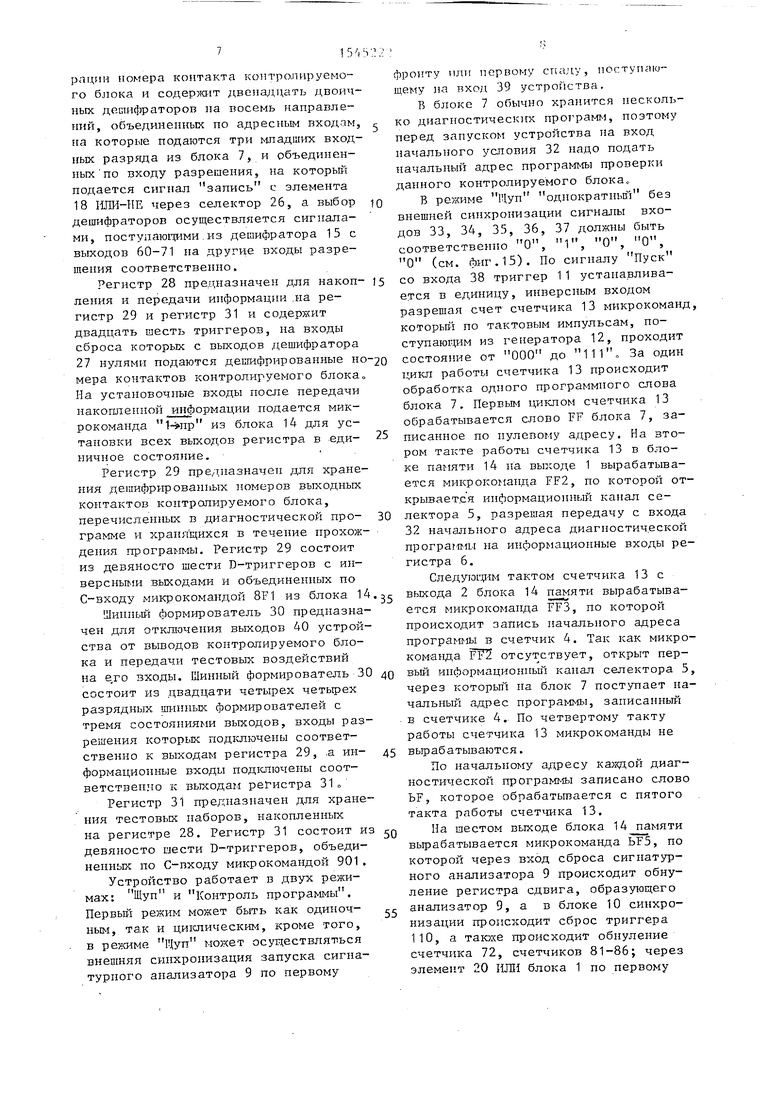

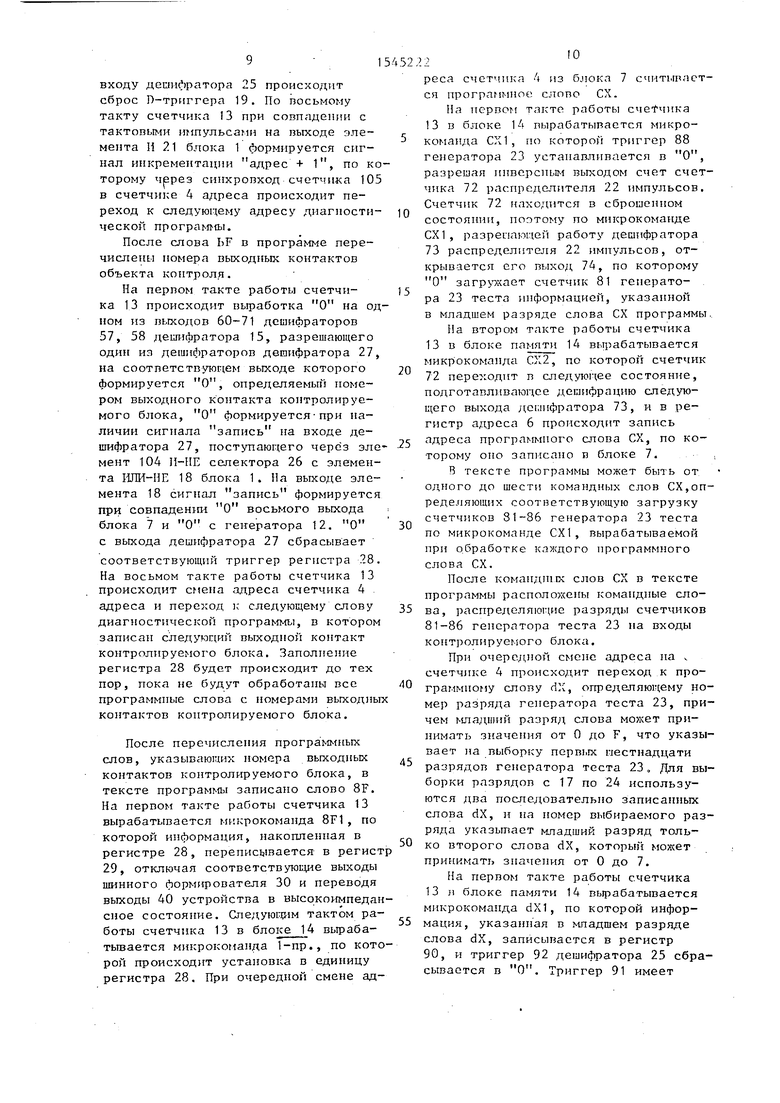

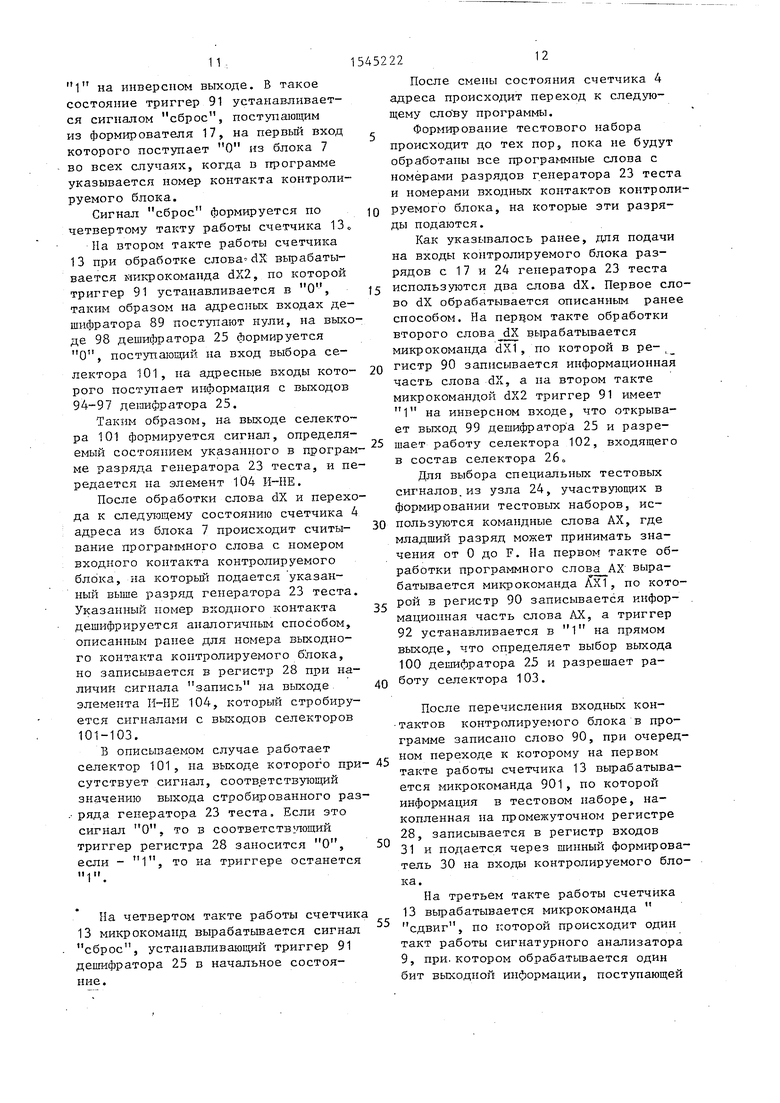

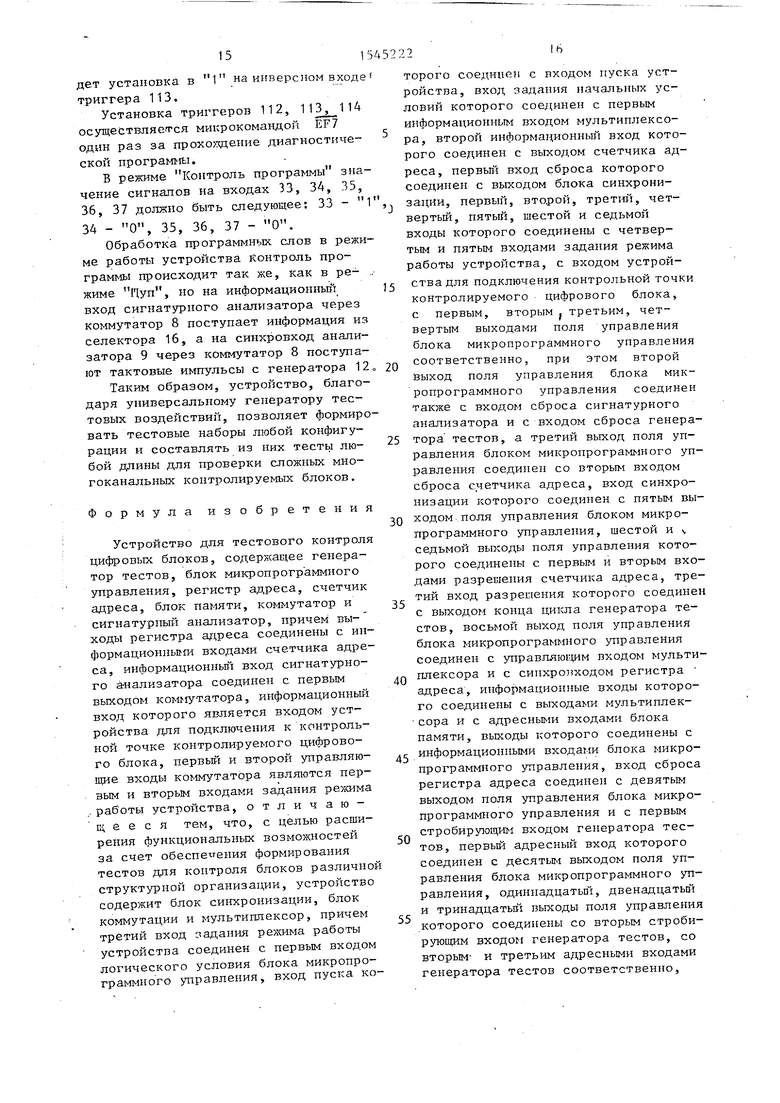

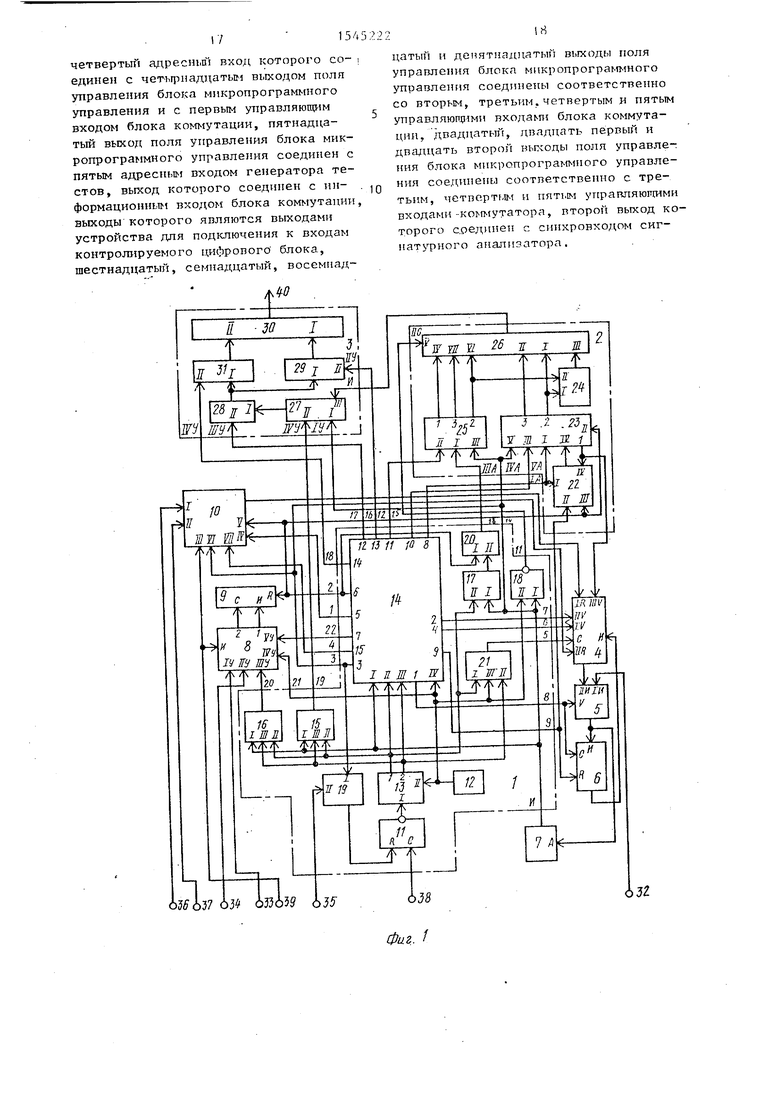

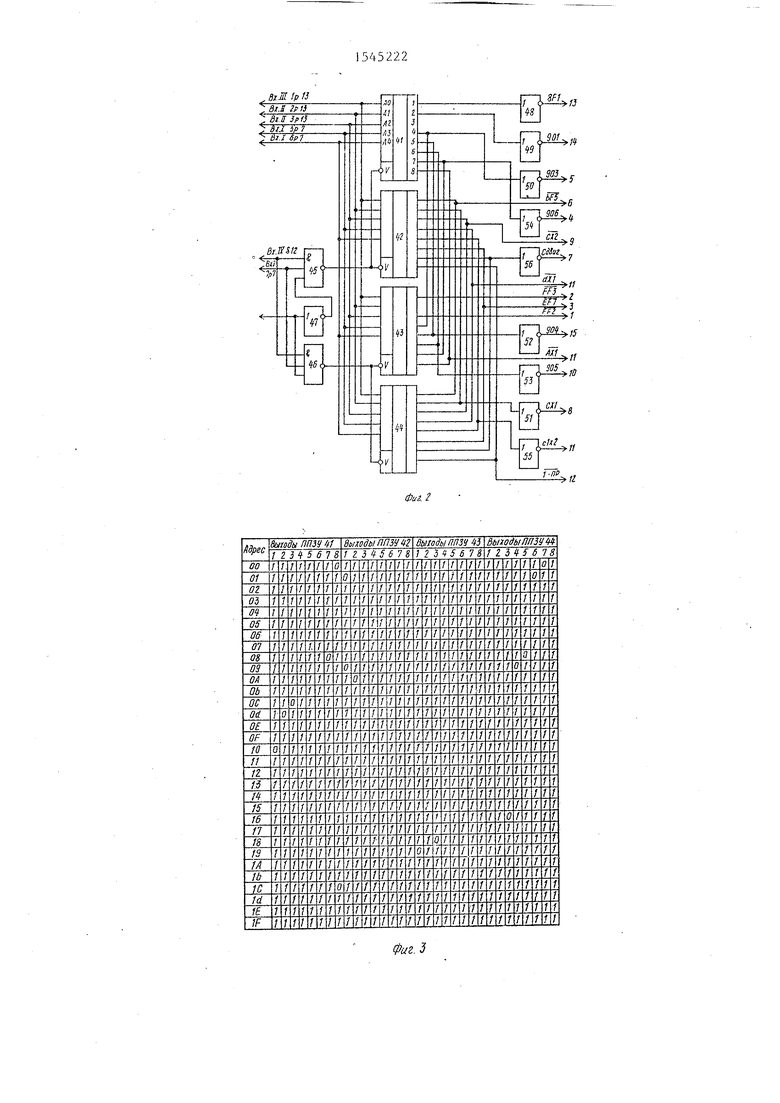

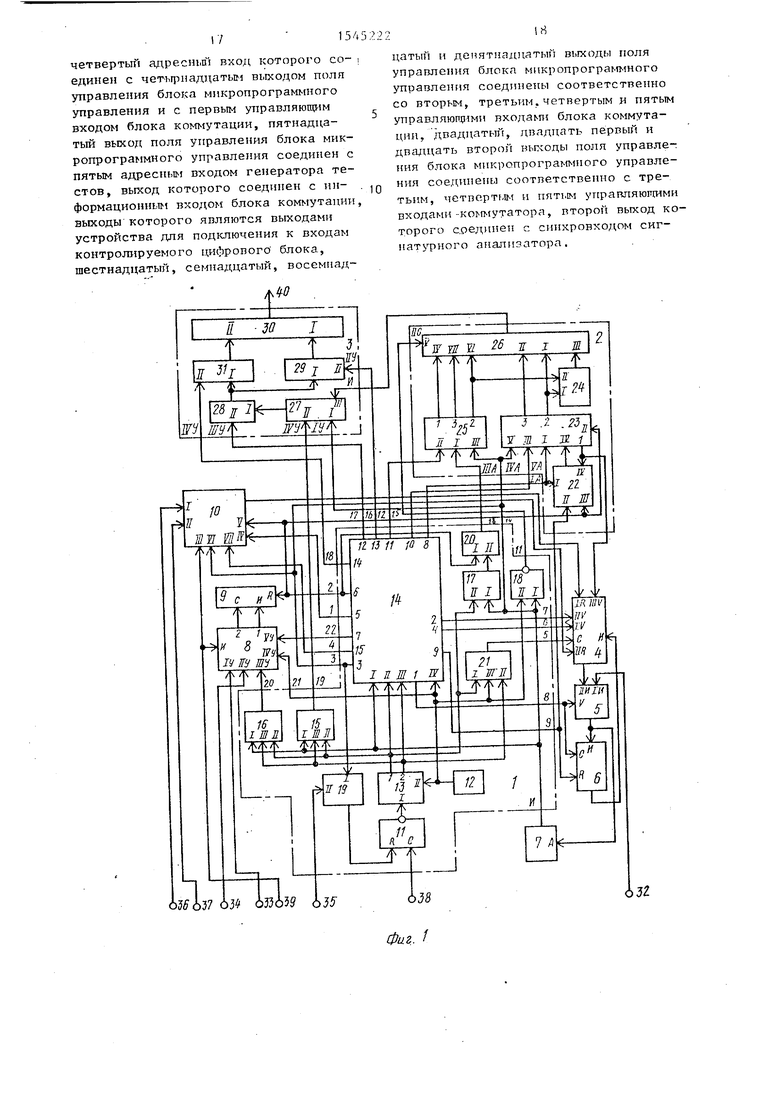

На фиг.1 представлена структурная схема устройства; ;;а фиг. 2 - функциональная схема блока памяти микрокоманд; на фиг.З - функциональная схема дешифратора номера контакта; на фиг.4- Функциональная схема распределителя импульсов загрузки; на фиг.З - функциональная схема генератора тесто- зых воздействий; на фиг.6 - схема

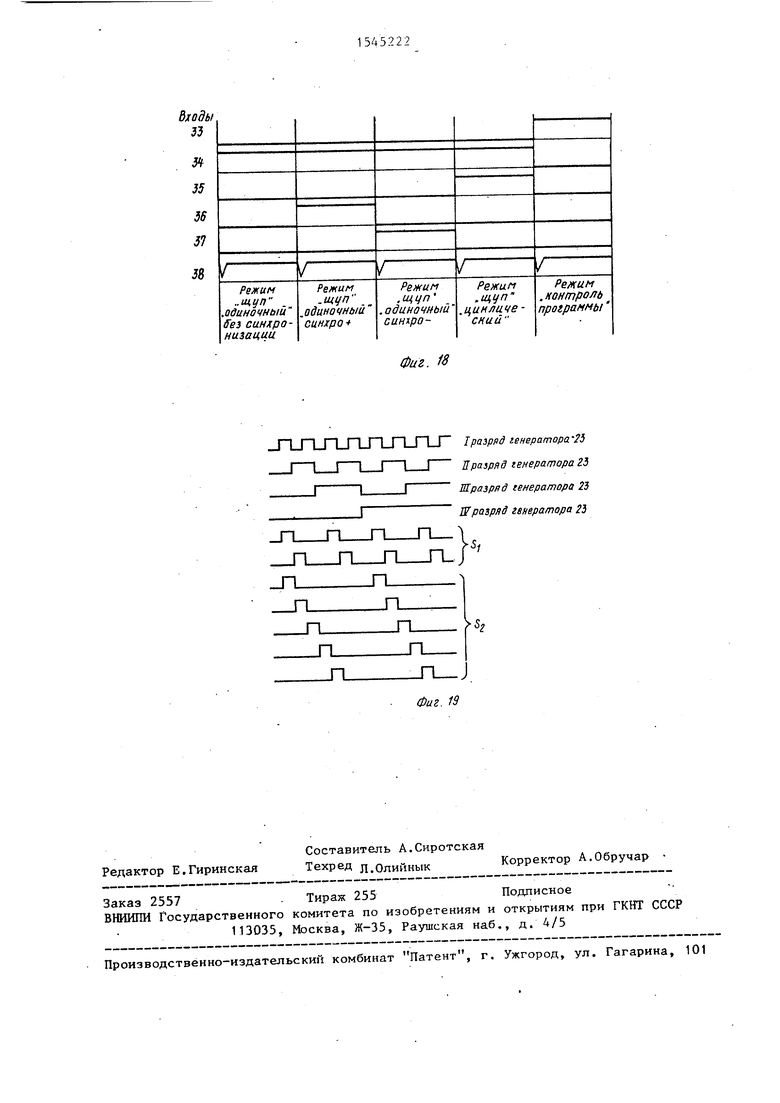

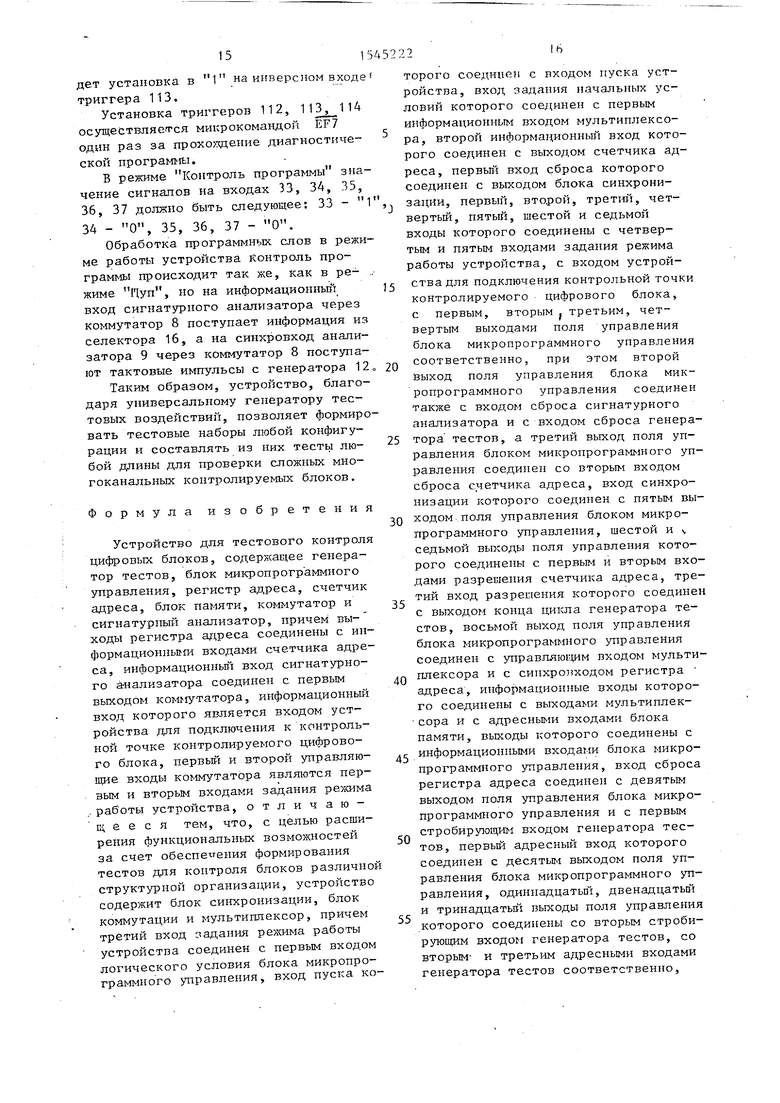

дешифратора разрешения номера разряда; на фиг„7 - функциональная схема селектора; на фиг.8 - функциональная схема счетчика адреса; на фиг.9 - функциональная схема блока синхронизации; на фиг.10 - схема сигнатурного анализатора; на фиг.11 показан пример выполнения буферного регистра в блоке коммутации; на фиг, 12 - пример выполнения буферного регистра входов в блоке коммутации; на фиг. 13 - схема коммутатора ; на ) иг . 1 4 - схема мультиплексора 5; на фиг.15 - диаграммы состояния сигналов па выходах для различных режимов работы уст- ромстра; на фиг.16 - диаграмма работы генератора тестов.

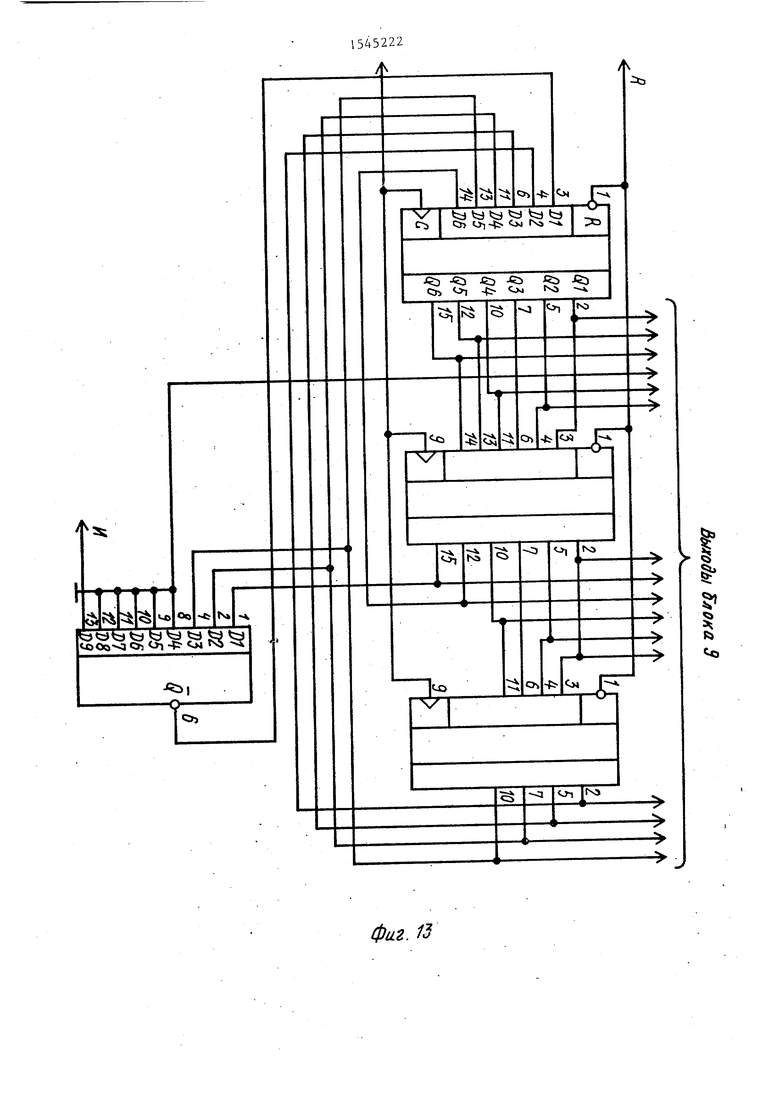

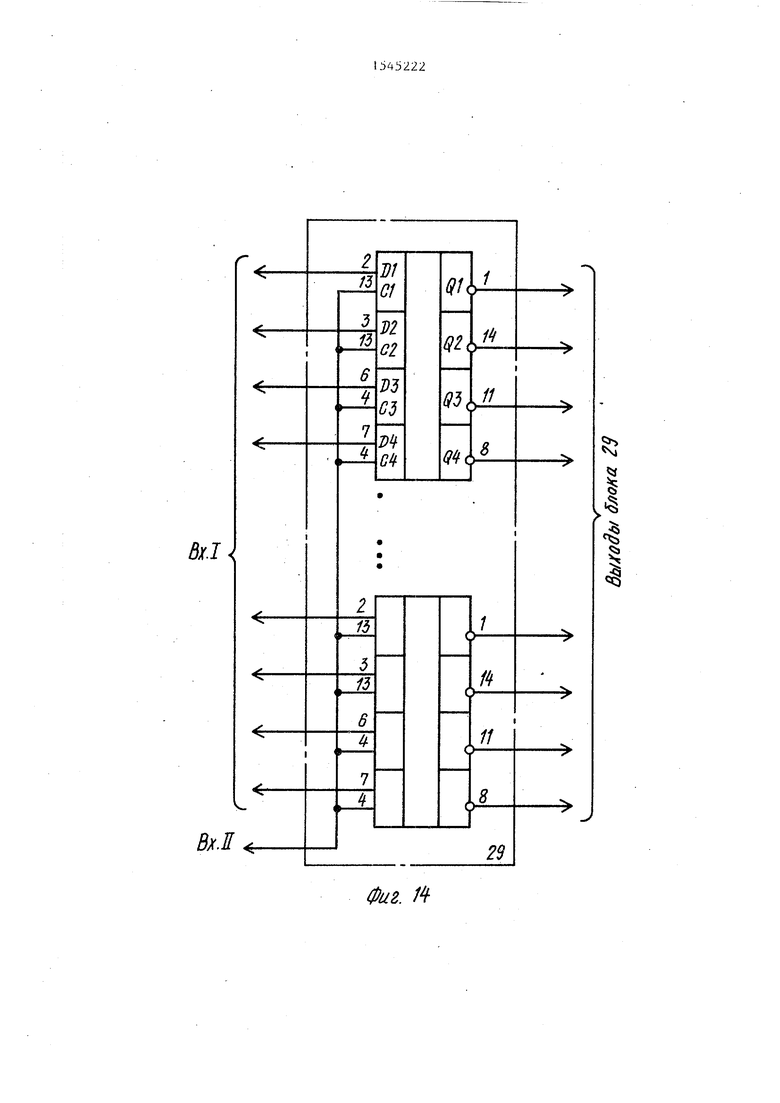

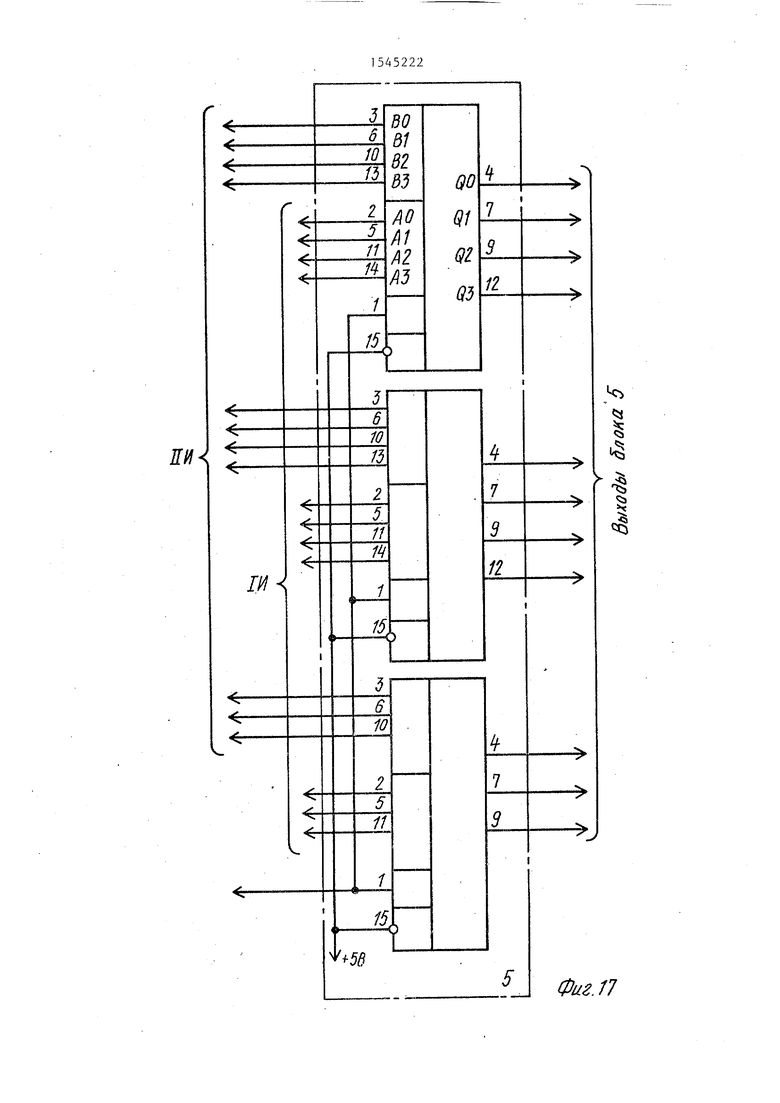

Устройство (фиг.1) содерхшт блок 1 микропрограммного управления, генератор 2 тестовых воздействий, блок коммутации 3, счетчик 4 адреса, мультиплексор 5, регистр 6 адреса, блок 7 памяти, коммутатор 8, сигнатурный анализатор 9, блок 10 синхронизации, триггер 11, генератор 12 тактовых импульсов, счетчик 13 микрокоманд, блок 14 памяти микрокоманд, дешифратор 15 номера контакта, селектор 16, формирователь 17 импульса сброса,элемент 18 ИЛИ-НЕ, элементы ИЛИ 19, 20, элемент И 21, распределитель импульсо 22 загрузки, генератор 23 теста, узел памяти 24,дешифратор 25 разрешения номе ра разряда,селектор 26,дешифратор 27 номера контакта, регистр 28, буферный регистр 29, шинный формирователь 30, буферный регистр 31 входов контролируемого блока, вход начального условия 32 устройства, входы 33, 34, 35 режимов работы устройства, входы 36, 37 синхронизации устройства, вход 38 запуска устройства, вход 39 устройства для подключения к внутрен- ней точке контролируемого блока, выход 40 устройства для подключения к входам контролируемого блока.

Блок 14 памяти мирокоманд (фиг.2) содержит узлы памяти 41-44, элементы И-НЕ 45, 46, элементы НЕ 47-56.

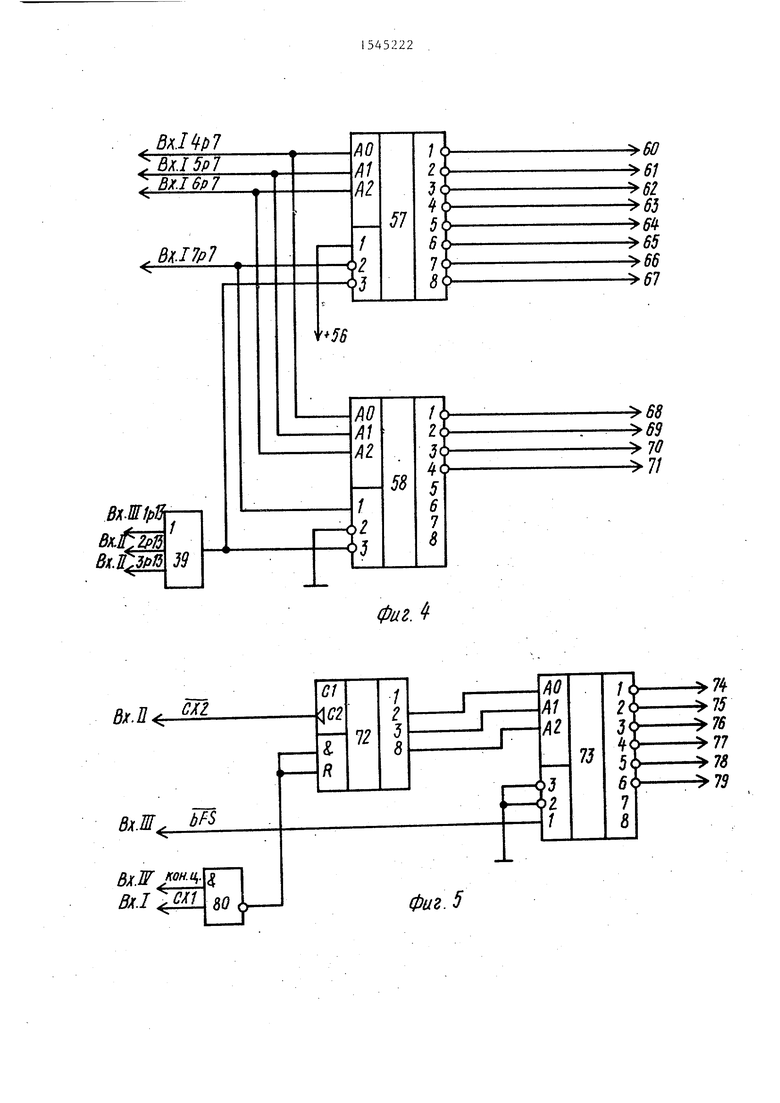

Дешифратор 15 номера контакта (фиг.З) содержит дешифраторы 57, 58, элемент ИЛИ 59, выходы дешифратора 60-71.

Распределитель импульсов 22 загрузки генератора теста (фиг.4) содержит счетчик 72, дешифратор 73, выходы распределителя 74-79, эле- мент И-НЕ 80.

Генератор 23 теста (фиг.5) содержит счетчики 81-86, элемент И 87, триггер 88.

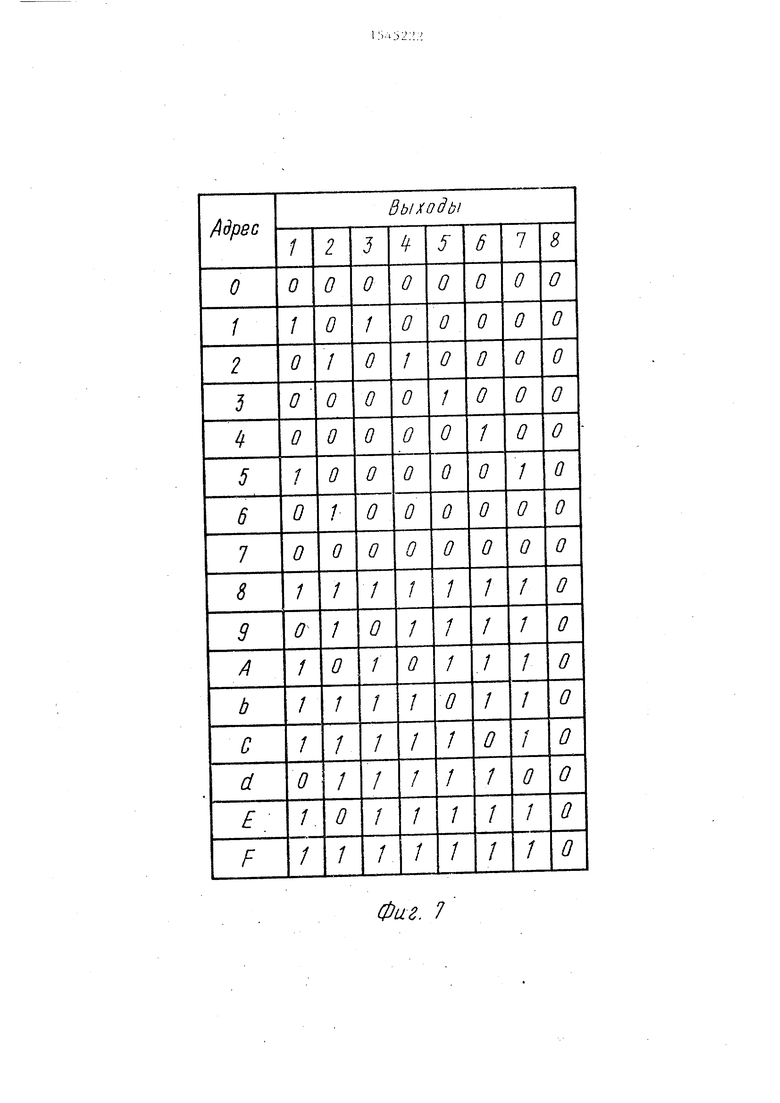

Дешифратор 25 разрешения номера

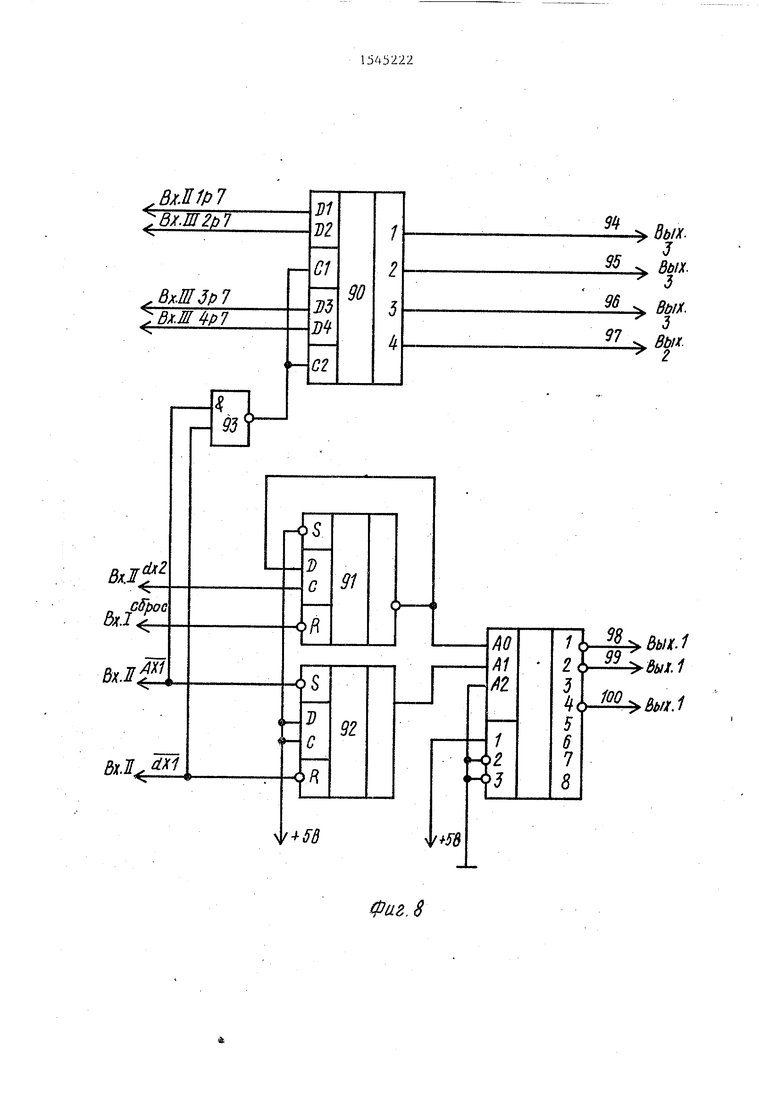

разряда (фиг.6) содержит дешифратор 89, регистр 90, триггеры 91, 92, элемент И-НЕ 93, выходы регистра 94-97, выходы дешифратора 98-100.

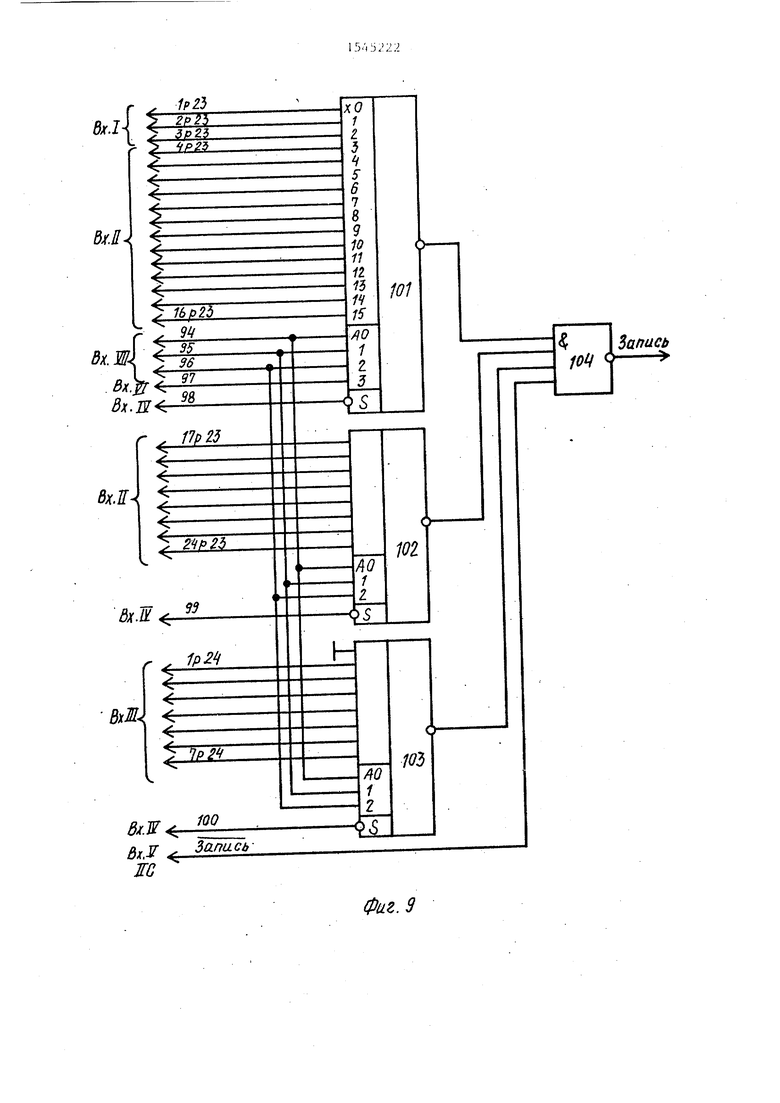

Селектор 26 (фиг.7) содержит селекторы 101-103, элемент И-НЕ 104„

Счетчик адреса 4 (фиг.8) содержит счетчики 105-107, элементы И-НЕ 108, 109, элемент И 110.

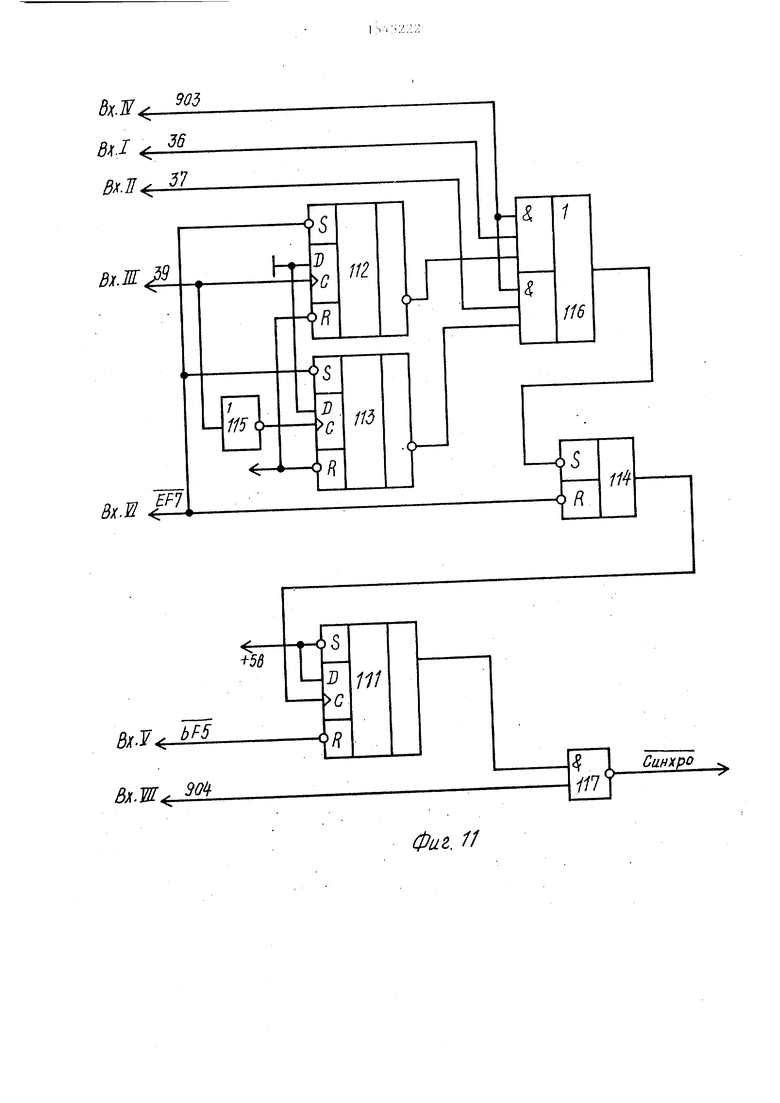

Блок 10 синхронизации (фиг.9) содержит триггеры 111-114, элемент НЕ 115, элемент И-ИЛИ-НЕ 116, элемент И-НЕ 117.

Илок 1 микропрограммного управления задает режимы работы всего устройства.

Генератор 2 тестовых воздействий предназначен для формирования тестовых наборов, подаваемых на контролируемый блок в соответствии с диагностической программой, подаваемой из блока 7 памяти.

Блок 3 связывает устройство с контролируемым блоком.

Счетчик 4 адреса предназначен для обхода адресов программы блока 7.

Мультиплексор 5 предназначен для передачи начального адреса программы с входа 32 или текущего адреса программы на блок 7 и регистр 6.

Регистр 6 адреса предназначен для хранения адреса начала программы или адреса начала цикла.

Блок 7 памяти предназначен для хранения диагностических программ и представляет собой восьмиразрядное ППЗУ.

Коммутатор 8 предназначен для переключения информации, поступающей на сигнатурный анализатор 9, представляет собой четырехразрядный шинный формирователь с тремя состояниями выходов.

Сигнатурный анализатор 9 предназначен для формирования сигнатур из информационной последовательности и традиционно содержит сумматор по модулю два и шестнадцатиразрядный сдвиговый регистр, седьмой, девятый, двенадцатый и шестнадцатый разряды которого подключены, к входу сумматора, на вход которого подается цифровая последовательность с выхода коммутатора 8, а выход подключен к информационному входу сдвигового регистра, вход синхронизации которого подключен к выходу синхронизации коммутатора 8. Выходы сдвигового регистра подключены к четырехразрядному индикатору, работающему в динамическом режиме.

Блок 10 синхронизации предназначен для формирования сигнала синхронизации синхро для счетчика 4 адреса по первому изменению входного сигнала на входе 39 с 0 на 1 при единице на входе 36 и с 1 на 0 при единиц на входе 37.

Триггер 11 предназначен для пуска устройства по сигналу пуск на входе 38, подключенному к С - входу

триггера II, к останова устройст ч по curn-mv гонец. nocTvnamneMv через злемонт Г П 19 .

Генератор 12 ИМПУНЬСОН пр«- чназпа чен дня Формирования ИМПУЛЬСОВ гин- хроничацпи п представляет гобои симметричный мультивибратор .

Счетчик 13 микрокоманд предпа°нач для Формирования ллреепы/ сигналом, подаваемых па три младынх адресны: входа Плокл 14 памяти, на входы ьыОо кп разряда селектора 16, на входы разрешения до итератора 15 неуюта контакта, на входы Формирователя 17 и на ПХС1ДМ элемента И 2. Счегчпк 13 предстапляет собой двоичный трехргз- рлдный счетчик, на счетный иход которого подаптгя пмпульсп сннхронрза- ции из генератора 12, а вход сброс подключен к инверсному входу триггера 1 1 .

Блок 1 памяти микрокоманд предназначен дня храненчя п считывания микрокоманд, записанных нулями на соответствующих адресах соответотм;. им ш разрядом узчоп памяти И-44 (см, табл.I).

Дешифратор 15 номера контакта . предназначен для пре. шари i елыюй дешифрации номера контакта контролируемого блока п группы по ьтсмь.

Селектор 16 предназначен для преобразования парачпепьпых восьмиразрядных кодоп, ноггупапних из блока 7 в одноразрядную циЛгюлч ю последонч- тельчость, подаг,ае;1ую через коммутатор 8 на сигнатх-рнып аначизатор Ч. Селсм;тор 1о прсдстанчяет собой се- лектор-мультпилексор на посемь канл- лол п один, па пу.оды н. к шалот которого подаптсч разряди счетчика 1

МИКрО 1МТНД.

( О м; ропател1. 17 импульса сброс гфедназпачсн для шгработкп сигнала устаноп; и и iicxr j or состояние ,,е- шифратора 25 и i аччягл coooi i че иифратор па четыре направления, па входы ш:оора каната которого подается старший разряд и) пчока 7 памяти; на вход 1азреыепия подается третий разряд счетчика М мпгрохомсШд, л на инверсный пход рачре ения подастся второй разряд счетчика 13 микрокоманд.

Элсмен 18 предназначен для формиронания сигнала из сигналов генератора 1. тактовых им- пульсов и восьмого разря;;а блока 7.

) ГЧЦ Г пре 1нач плчен для ч.трогеннч прохоууимшя CHI нала сбро- ( а трпгг-ера 1 I n режиме работы устройства цикчпческий. Па первый 0X01 -.лемечта Ч ИЛИ подлетел микро- ьоми п ГР/, ,, дрчгой вход подключен к входу 35 устройства, а пыход под- кчмчеп к вх(Ч1У cfijuica триггера 1 1 „ )пемепт 1411 20 предна- начен для

передачи сигнала сброс на чег.гиф- ратор 5. На пепвып вход тчемента 20 подается микрокоманда ЬР5, а второй вход подкчмчен к выходу сЬормиропатп, лч 17.

Злемепт И 21 предназначен для формирования по каждому восьмому такту работы счетчика 13 микрокоманд сиг- п.ша ппкрементапии адрес + 1, пода0 саемого па сметным вход счетчика 4 адреса .

Г. спреп.елигегть 22 импульсов за- гр . жн генератора тестов предназначен для Формирования гигнапа загрузка

5 счетчиков генератора 23 и управляется микрокомандой СХ1, подаваемой на вход рлзрепонпя, а количество выбранных каналов зависит от числа командных счов ГХ в программе. Счет осуще-

0 сгвдяется по микрокоманд СХ2, обну- .ченпе в начале программы по микрокоманде ЬГ5 и по окончании цикла по сигналу конец цикла, поступаюпему пч генератора 23 на вход Ороса счет чпка 72, черсчз элемент И-11Г 80.

Генератор 23 црс щазп.пгеи для от- счета кочпчестьа тактов в цикле про- B -,II и п Формирования сигналов, из которых комбпппр ются i i гiопыс набоС I1 , f оставляющие тест.

У ел п. мяти 24 предназначен для хранения вепомогатечьш гх спгпчлоп (см. таблицу 2) Формирования тестовых наборов, вписанных но фронтам и спадам

5 в разряды счетчиков 81-86 генератора 73 теста и реализован па ППЗУ 8 х х 32, три гшадших адресных входа ко- торого нодключены i младшим входным разрядам счетчика 81 генсратоС ра 23, а на четвертый адресный вход поступает сигнал инверсия с дешифратора 25. Гзел 24 постоянно находится в режиме считывания.

Дешифратор 25 предназначен для

5 управления селектором .(.

Селектор 26 предназначен для стро- бированпя сигнала запись.

Дешифратор 27 номера контакта предназначен для окончательной дешиф

рации номера контакта контромнруемо- го блока и содержит двенадцать двоичных дешифраторов на восемь направлений, объединенных по адресным входтм, на которые подаются три младших входных разряда из блока 7, и объединенных по входу разрешения, на который подается сигнал запись с элемента 18 ИЛИ-НЕ через селектор 26, а выбор дешифраторов осуществляется сигналами, поступающими из дешифратора 15 с выходов 60-71 па другие входы разрешения соответственно.

Регистр 28 предназначен для накоп- пения и передачи информации на регистр 29 и регистр 31 и содержит двадцать псс.тъ триггеров, на входы сброса которых с выходов дешифратора 27 нулями подаются дешифрированные но мера контактов контролируемого блока. Па установочные входы после передачи накопленной информации подается микрокоманда из блока 14 для установки всех выходов регистра в единичное состояние.

Регистр 29 предназначен для хранения дешиАрнрованиых номеров выходных контактов контролируемого блока, перечисленных в диагностической про- грамме и хранящихся в течение прохождения программы. Регистр 29 состоит из девяносто шести Л-триггеров с инверсными выходами и объединенных по С-входу микрокомандой 8F1 из блока 1

Шинный с юрмирователь 30 предназначен для отключения выходов 40 устройства от выводов контролируемого блока и передачи тестовых воздействий на е,го входы. Шинный формирователь 30 состоит из двадцати четырех четырех разрядных шинных формирователей с тремя состояниями выходов, входы разрешения которых подключены соответственно к выходам регистра 29, а ин- формациоиные входы подключены соответственно к выходам регистра 31 „

Регистр 31 предназначен для хранения тестовых наборов, накопленных на регистре 28. Регистр 31 состоит из девяносто шести D-триггеров, объединенных по С-входу микрокомандой 901.

Устройство работает в двух режимах: Щуп и Контроль программы. Первый режим может быть как одиночным, так и циклическим, кроме того, в режиме 1Цуп может осуществляться внешняя синхронизация запуска сигнатурного анализатора 9 по первому

5

5 0

0 5

0 5

о

5

cbpoHTv inn первому rtia iv, паю-- шему на вход 39 устройства.

В блоке 7 обычно хранится несколько диагностических программ, поэтому перед запуском устройства на вход начального условия 32 надо подать начальный адрес программы проверки данного контролируемого блока,

В рекиме Пуп однократный без внешней синхронизации сигналы входов 33, 34, 35, 36, 37 должны быть

UrvM Mil 1 П

соответственно 0 , 1 , 0 , О , О (см. биг.15). По сигналу Пуск со входа 38 триггер 11 устанавливается в единицу, инверсным входом разрешая счет счетчика 13 микрокоманд, который по тактовым импульсам, поступающим из генератора 12, проходит состояние от 000 до 111, За один цикл работы счетчика 13 происходит обработка одного программного слова блока 7. Первым циклом счетчика 13 обрабатывается слово РГ блока 7, записанное по пулевому адресу. На втором такте работы счетчика 13 в блоке памяти 14 на выходе 1 вырабатывается микрокоманда FF2, по которой открывается информационный канал селектора 5, разрешая передачу с входа 32 начального адреса диагностической программы на информационные входы регистра 6.

Следующим тактом счетчика 13 с выхода 2 блока 14 памяти вырабатывается микрокоманда FF3, по которой происходит запись начального адреса программы в счетчик 4. Так как микрокоманда FF2 отсутствует, открыт первый информационный канал селектора 5, через который на блок 7 поступает начальный адрес программы, записанный в счетчике 4. По четвертому такту работы счетчика 13 микрокоманды не вырабатываются.

По начальному адресу каждой диагностической программы записано слово ЬР, которое обрабатывается с пятого такта работы счетчика 13.

На шестом выходе блока 14 памяти вырабатывается микрокоманда bF5, по которой через вход сброса сигнатурного анализатора 9 происходит обнуление регистра сдвига, образующего анализатор 9, а в блоке 10 синхронизации происходит сброс триггера 110, а также происходит обнуление счетчика 72, счетчиков 81-86; через элемент 20 НЛП блока 1 по первому

входу дешифратор; 25 происходит сброс П-триггера 19. По пос7-.мому такту счетчшса 13 при совпадении с тактовыми импульсами на выходе чте- мента И 21 блока 1 формируется сигнал инкрементацни адрес + 1, по которому чррез синхропход счетчика 105 в счетчике 4 адреса происходит переход к следующему адресу дпагпостп- ческой программы.

После слова Ыг в программе пере- численп номера выходных контактов объекта контроля.

На первом такте работы счетчи- ка 13 происходит выработка О на одном из выходов 60-71 дешифраторов 57, 58 дешифратора 15, разрешающего один ип дешифраторов депифратора 27, на соответствующем выходе которого формируется О, определяемы номером выходного контакта контролируемого блока, О формируетсяпри наличии сигнала запись на входе дешифратора 27, поступаюпего через эле мент 10Д И-IIГ. селектора 26 с элемента ПЛИ-ПГ 18 блока 1. На выходе элемента 18 сигнал запись д юрмируетсл при совпадении О восьмого выхода блока 7 и О с генератора 12. О с выхода дешифратора 27 сбрасывает

соответствующий триггер регистра 28. На восьмом такте работы счетчика 13 происходит смена адреса счетчика 4 адреса и переход к спедующему слову диагностической программы, в котором записан следующий выходной контакт контролируемого блока. Заполнение регистра 28 будет происходит до тех пор, пока не будут обработаны все программные слова с номерами выходны контактов контролируемого блока.

После перечисления программных слов, указываюгшх номера выходных контактов контролируемого блока, в тексте программы записано слово 8F. На первом такте работы счетчика 13 вырабатывается микрокоманда 8F1, по которой информация, накопленная в регистре 28, переписывается в регистр 29, отключая соответствующие выходы шинного формирователя 30 и переводя выходы 40 устройства в высокоимпедан- спое состояние. Следующим тактом работы счетчика 13 в блоке 14 вырабатывается микрокоманда -пр., по которой происходит установка в единицу регистра 28. При очередной смене ад

5 0 5 0

5 0

5

0

5

реса счетчика 4 из блок. 7 считывается программное1 слово СХ.

На пс-рпом такте работы счеТчика 13 в блоке 14 вырабатывается микрокоманда CXI, по которой триггер 88 генератора 23 устанавливается л О, разрешая инверсным выходом счет счетчика 72 распределителя 22 импульсов. Счетчик 72 находится в сброшенном состоянии, поэтому по микрокоманде СХ1, разрепарцей работу дешифратора 73 распределителя 22 импульсов, открывается его выход 74, по которому О загружает счетчик 81 генератора 23 теста информацией, указанной в младшем разряде слова СХ программы

Па втором такте работы счетчика 13 в блоке памяти 14 вырабатывается микрокоманда СХ2, по которой счетчик 72 переходит в следующее состояние, подготавливайте дешифрацию следующего выхода дешифратора 73, ив регистр адреса 6 происходит запись адреса программного слова СХ, по которому оно записано л блоке 7.

тексте программы может быть от одного до шести командных слов СХ,оп- редечяющнх соответствующую загрузку счетчиков 81-86 генератора 23 теста по микрокоманде СХ1, вырабатываемой при обработке каждого программного слова СХ.

После командных слов СХ в тексте программы расположены командные слова, распределяющие разряды счетчиков 81-86 генератора теста 23 на входы контролируемого блока.

При очередной смене адреса на . счетчике 4 происходит переход к программному слову dX, определяющему номер разряда генератора теста 23, причем младший разряд слова может принимать значения от О до F, что указывает на выборку первых шестнадцати разрядов генератора теста 23, Для выборки разрядов с 17 по 24 используются два последовательно записанных слова dX, и па помер выбираемого разряда указывает младший разряд только второго слова dX, который может принимать значения от 0 до 7.

На первом такте работы счетчика 13 л блоке памяти 14 вырабатывается микрокоманда dXI, по которой информация, указанная в мпадшем разряде слова dX, записывается в регистр 90, и триггер 92 дешифратора 25 сбрасывается в О. Триггер 91 имеет

11

1 на инверсном выходе. В такое состояние триггер 91 устанавливается сигналом сброс, поступающим из формирователя 17, на первый вход которого поступает О из блока 7 во всех случаях, когда и программе указывается номер контакта контролируемого блока.

Сигнал сброс формируется по четвертому такту работы счетчика 13„

На втором такте работы счетчика 13 при обработке слова-dX вырабатывается микрокоманда dX2, по которой триггер 91 устанавливается в О, таким образом на адресных входах дешифратора 89 поступают нули, на выходе 98 дешифратора 25 формируется О, поступающий на вход выбора селектора 101, на адресные входы которого поступает информация с выходов 94-97 дешифратора 25.

Таким образом, на выходе селектора 101 формируется сигнал, определяемый состоянием указанного в программе разряда генератора 23 теста, и передается на элемент 104 И-НЕ.

После обработки слова dX и перехода к следующему состоянию счетчика 4 адреса из блока 7 происходит считывание программного слова с номером входного контакта контролируемого блока, на который подается указанный выше разряд генератора 23 теста. Указанный помер входного контакта дешифрируется аналогичным способом, описанным ранее для номера выходного контакта контролируемого блока, но записывается в регистр 28 при наличии сигнала запись на выходе элемента Н-НЕ 104, который стробиру- ется сигналами с выходов селекторов 101-103.

В описываемом случае работает селектор 101, на выходе которого присутствует сигнал, соответствующий значению выхода стробированного разряда генератора 23 теста. Если это сигнал О, то в соответств1тощий триггер регистра 28 заносится О, если - 1, то на триггере останется

tl 1

На четвертом такте работы счетчика 13 микрокоманд вырабатывается сигнал сброс, устанавливающий триггер 91 дешифратора 25 в начальное состояние.

4522212

После смены состояния счетчика 4 адреса происходит переход к следующему слову программы. Формирование тестового набора происходит до тех пор, пока не будут обработаны все программные слова с номерами разрядов генератора 23 теста и номерами входных контактов контролиЮ РУемого блока, на которые эти разряды подаются.

Как указывалось ранее, для подачи на входы контролируемого блока разрядов с 17 и 24 генератора 23 теста

15 используются два слова dX. Первое слово dX обрабатывается описанным ранее способом. На первом такте обработки второго слова dX вырабатывается микрокоманда dX1, по которой в ре20 гистр 90 записывается информационная часть слова , а на втором такте микрокомандой dX2 триггер 91 имеет 1 на инверсном входе, что открывает выход 99 дешифратора 25 и разре- 25 шает работу селектора 102, входящего в состав селектора 26

Для выбора специальных тестовых сигналов.из узла 24, участвующих в формировании тестовых наборов, ис30 пользуются командные слова АХ, где младший разряд может принимать значения от 0 до F. На первом такте обработки программного спова АХ вырабатывается микрокоманда АХ1, по котозг рой в регистр 90 записывается информационная часть слова АХ, а триггер 92 устанавливается в 1 на прямом выходе, что определяет выбор выхода 100 дешифратора 25 и разрешает ра40 боту селектора 103.

После перечисления входных контактов контролируемого блока в программе записано слово 90, при очеред- .,- ном переходе к которому на первом такте работы счетчика 13 вырабатывается микрокоманда 901, по которой информация в тестовом наборе, накопленная на промежуточном регистре 28, записывается в регистр входов 31 и подается через шинный формирователь 30 на входы контролируемого блока.

На третьем такте работы счетчика 13 вырабатывается микрокоманда сдвиг, по которой происходит один такт работы сигнатурного анализатора 9, при. котором обрабатывается один бит выходной информации, поступающей

50

на информационный BXO-I гш н,п vpnoro анализатора 9 с входа 39 устройства.

На пятом такте работы счетчика 13 из блока 14 памяти вырабатывается микрокоманда 905, по которой вычита- ется единица из состояния счетчиков 81-86 генератора 23 теста, определяющего один тестовый набор.

На шестом такте работы счетчика 13 вырабатывается микрокоманда 906, по которой через элемент И-НК 108 пр отсутстшш сигнала конец цикла происходит перезапись адреса последнего программного слова СХ из регист ра 6 п счетчик 4.

На восьмом такте работы счетчика 13 происходит смена адреса счетчика 4, переход к первому программному слову, записанному п блоке 7 по- еле слопа СХ, и начинается формирование на регистре 28 следующего тестового набора, но при попом состоянии счетчиков 81-86 генератора теста 23.

Формирование тестовых наборов и передача их па контролируемый блок будет происходить до те:: пор, пока не будет выработан сигнал конец цикла, который запрещает прохожие- ние микрокоманды 906 па пходы записи счетчиков 10S-107 счетчика 4 адреса, поэтому перехода к последнему программному слову СХ нет, а при очере/1 ной смене адреса счетчика 4 происходит переход к следующему ча 90 программному слопу.

В одной программе может быть организовано необходимое количество циклоп формирования тестовых набо- ров. После окончания формирования последнего цикла при очередной смене адреса счетчика 4 in блока 7 считывается последнее спово программы ЕГ.

На седьмом такте работы счетчика 13 вырабатывается микрокоманда EF7, по которой через члемент ИЛИ 19 тригер 11 сбрасывается п О и единицей с инверсного входа запрещает работу счетчика 13 микрокоманд и сбрасывает его в нулевое состояние, а через эдимент II-I1F, 109 по микрокоманде КГ7 счетчики 105-107 сбрасываются в О. Для повторного пуска устройства необходимо подать сигнал пуск на вход 38 устройства .

5

0 5

0

O 5

0

5

R релим I lvn чиь тч м кмп внешней спнхропнчацип спгпачп входов 53, 34, 35, }6 , 37 дочжны быть

стю-отощими: 33 - 34 - 45 - 36, 37 - О.

Обработка программных счов происходит так же, как при режиме Шуи однократный, но при обработке программного слова MF О на входе 35 /запрещает прохождение микрокоманды EF7 через члемент ИЛИ 19, п счетчик 13 не сбрасывается и не запрещается для обработки программ гх слов, но счетчик 4 адреса по первому сбросовому входу сбрасывается в нулевое состояние, что обеспечивает переход к начальному адресу и обработке первого слова программы,

П режиме 1 lyn сппхро + сигналы входов 33, 34, 35, 36, 37 должны быть следующими: 33 - О, 34 - 1, 35 - О, 36 - 1, 37 - О.

Обработка программных слов происходит так же, как в рочпме Пуп однократный до момента выработки микрокоманды 903 .

Кечи при шаге произогпо изменение входной информации с нуля на единицу, то П-триггер 112 блока 10 устанавливается в 1 па инверсном выходе, разрспап прохождение микрокоманды 903 через элемент 2-ЗИ-2-ИЛИ- ПК 116 на вход установки триггера 114, устанавливая его в 1, тем самим П-трпггер 111 устанавливается в 1, разрешая прохо/чцение через члемент П-ПГ 117 микрокоманде 904, вырабатываемой на четвертом такте работы счетчика 13 при обработке слова 90.

Тагим обрл- ом, сигнал сннхро на выходе элемента И-ИГ 117 через элемент H-1IF 109 сбрасывает счетчики 105-107 счетчика 4 адреса. Обработка программных слов начинается с первого слова, по начальное значение вход- нон последовательности, поступающей на вход 39, будет известно и равно 1.

П режтч- Пуп синхро- значение входных сигналов должно бить такое же, как в ре/симе Пуп сннхро+, кроме -ходов 36 и 37, на входе 36 - О, на выходе 37 - Ч.

Работа блока 10 будет происходить аналогичным способом, описанном в . предыдущем режиме, но при изменении входного сигнала с 1 на О произой15

дет установка в Г1 на инверсном входе триггера 113.

Установка триггеров 112, 1 13, 114 осуществляется микрокомандой LF7 один раз за прохождение диагностической программы.

В режиме Контроль программы значение сигналов на входах 33, 34, 35, 36, 37 должно быть следующее: 33 - 1

34 - О, 35, 36, 37 - О.

Обработка программньк слов в режиме работы устройства контроль программы происходит так же, как в ре- . жиме Пуп, но на информационный вход сигнатурного анализатора через коммутатор 8 поступает информация из селектора 16, а на синхровход анализатора 9 через коммутатор 8 поступают тактовые импульсы с генератора 12„

Таким образом, устройство, благодаря универсальному генератору тестовых воздействии, позволяет формировать тестовые наборы любой конфигурации и составлять из них тесты любой длины для проверки сложных многоканальных контролируемых блоков.

Формула изобретения

Устройство для тестового контроля цифровых блоков, содержащее генератор тестов, блок микропрограммного управления, регистр адреса, счетчик адреса, блок памяти, коммутатор и сигнатурный анализатор, причем выходы регистра адреса соединены с информационными входами счетчика адреса, информационный вход сигнатурного а-налнзатора соединен с первым выходом коммутатора, информационный вход которого является входом устройства для подключения к контроль- нон точке контролируемого цифрового блока, первый и второй управляю- щие входы коммутатора являются первым и вторым входами задания режима работы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения формирования тестов для контроля блоков различной структурной организации, устройство содержит блок синхронизации, блок коммутации и мультиплексор, причем третий вход задания режима работы устройства соединен с первым входом логического условия блока микропрограммного управления, вход пуска коV.V

1,j

. „

15

20

25

30

35 до 45 „ 1 |h

торого соединен с входом пуска устройства, вход падания начальных условий которого соединен с первым информационным входом мультиплексора , второй информационный вход которого соединен с выходом счетчика адреса, первый вход сброса которого соединен с выходом блока синхронизации, первый, пторой, третий, четвертый, пятый, шестой и седьмой входы которого соединены с четвертым и пятым входами задания режима работы устройства, с входом устройства для подключения контрольной точки контролируемого цифрового блока, с первым, вторым ( третьим, четвертым выходами поля управления блока микропрограммного управления соответственно, при этом второй выход поля управления блока микропрограммного управления соединен также с входом сброса сигнатурного анализатора и с входом сброса генератора тестов, а третий выход поля управления блоком микропрограммного управления соединен со вторым входом сброса счетчика адреса, вход синхронизации которого соединен с пятым выходом поля управления блоком микропрограммного управления, шестой и v седьмой выходы поля управления которого соединены с первым и вторым входами разрешения счетчика адреса, третий вход разрешения которого соединен с выходом конца цикла генератора тестов, восьмой выход поля управления блока микропрограммного управления соединен с управляющим входом мультиплексора и с синхропходом регистра адреса, информационные входы которого соединены с выходами мультиплексора и с адресными входами блока памяти, выходы которого соединены с информационными входами блока микропрограммного управления, вход сброса регистра адреса соединен с девятым выходом поля управления блока микропрограммного управления и с первым стробирующим входом генератора тестов, первый адресный вход которого соединен с десятым выходом поля управления блока микропрограммного управления, одиннадцатый, двенадцатый и тринадцатый выходы поля управления которого соединены со вторым стробирующим входом генератора тестов, со вторым и третьим адресными входами генератора тестов соответственно,

четвертый адресный вход которого соединен с четырнадцатым пыходом поля управления блока микропрограммного управления и с первым управляющим входом блока коммутации, пятнадцатый выход поля управления блока микропрограммного управления соединен с пятым адресным входом генератора тестов, выход которого соединен с информационным входом блока коммутации выходы которого являются выходами устройства для подключения к входам контролируемого цифрового блока, шестнадцатый, семнадцатый, носсмнад&W

цатыи и девятнадцатый выходы ноля управления блока микропрограммного управления соединены соответственно со вторым, третьим.четвертым и пятым управляющими входами блока коммутации, двадцатый, двадцать первый и двадцать второй выходы поля управления блока микропрограммного управления соединены соответственно с третьим, четвертым и питым управляющими входами коммутатора, второй выход которого соединен г. синхровходом сигнатурного анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

Изобретение относится к вычислительной технике, в частности к системам программного контроля, и может быть использовано для тестовой проверки цифровых блоков. Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования тестов для контроля блоков различной структурной огранизации. Устройство благодаря универсальному генератору тестовых воздействий позволяет формировать тестовые наборы любой конфигурации и составлять из них тесты любой длины для проверки сложных многоканальных контролируемых блоков. 16 ил., 3 табл.

фиг 1

f f f

3 3 +i J-.1 NO

«S oS - , i

a

A A A

СЗЭ

s

-н

t

-fcs

л s

:ь.

гча -.

e;

Oo

CTl -t Cjj N3-O-O-Q-O-

.

S3

r-O-Ot 4«Na

ibiu ii.

сэ

ЈLn

OD--J O «j, INS

V W Ж V V V СГ( Э

-sjO -fc-t 4t4 5

ЪхЖ1

ВхЖ

ex.:

&X.I

вых.

дых.

3

фиг. 6

Bx,I. bd

ьа

Вых. J

Вых. 3

Bbtx. 2

Вых. 1 Ьых.1

Вьа.1

Фиг, 8

Фиг. Ю

Фиг. //

Фиг. 12

U1

--г

LH

Б

ч

4

г

Г4

Ч)

л А л л

o-

SN

- «41 Ъ

CS r

i

СЧ1 K- CQCQ CQCCi

«-.csahc 4;

ча

/ / f

f f f

g VVOVQ ярохпд

1 k fa fa

/ /ч /ч

fe

i

CJ-

5

«

K

45

N

Чэ

N1 :

-O-I

/ / / /

V f f

f

f f /

f

v

JTUT -TlJr jr J Lf Jr Iразряд (енератора-25

Л разряд генератора Z3 Ш разряд генератора 23 17разряд генератора 23

п

Фиг. М

п

S,

Фиг 19

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1987-01-04—Подача