1

Изобретение относится к электронным цифровым системам с резервированием и может быть использовано в качестве хранителя времени в сочетании с высокостабильным генератором в условиях случайных сбоев отдельных элементов.

Известно устройство, содержащее два канала деления, каждый из которых состоит из делителя частоты и схемы контроля. Однако при возникновении случайного сбоя в одном из каналов этот канал отключается и при последующем сбое второго канала устройство становится неработоспособным.

Целью изобретения является коррекция случайных сбоев. С этой целью в каждый канал деления введен элемент памяти, при этом входы элемента памяти каждого канала подключены к выходам схемы контроля, а выход - ко входу схемы контроля и входу установки делителя частоты, выход которого через элемент задержки соединен со входом элемента памяти другого канала деления.

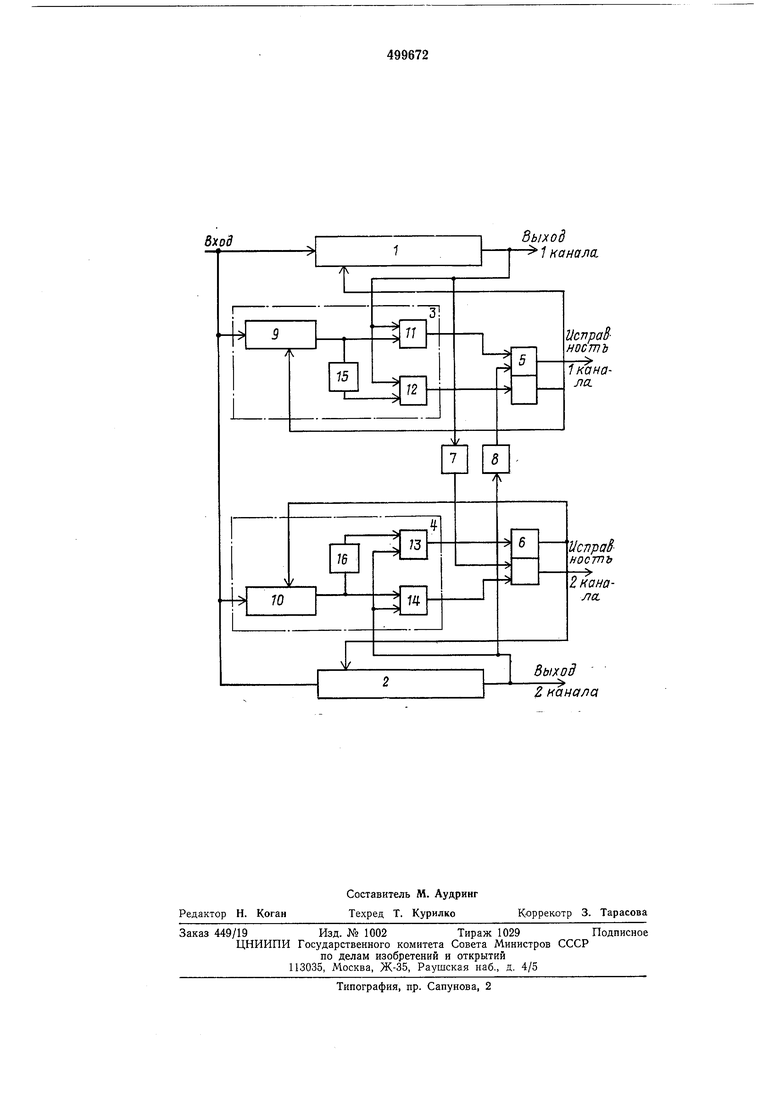

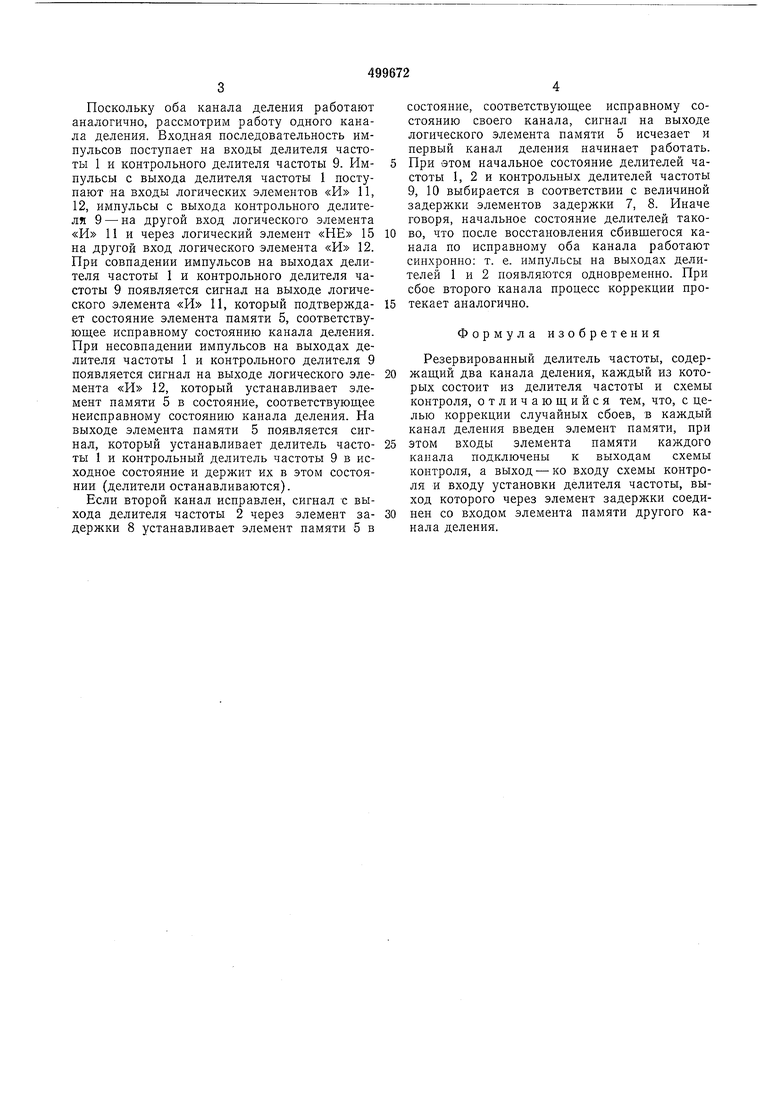

На чертеже представлена схема резервированного делителя частоты, который состоит из делителей частоты 1, 2, схем контроля 3, 4, элементов памяти 5, 6, элементов задержки 7, 8, контрольных делителей частоты 9, 10, логических элементов «И 11 -14, логических элементов «НЕ 15, 16.

На входы делителей частоты 1, 2 и контрольных делителей частоты 9, 10 схем контроля 3, 4 подается входная последовательность импульсов. Выходы делителей 1, 2 соединены соответственно со входами логических элементов «И 11, 12, 13, 14 схем контроля 3, 4 каждого канала деления и с входами элементов задержки 7, 8. Входы логических элементов «И 11 и 14 соединены соответственно с выходами контрольных делителей частоты 9, 10 схем контроля, а входы логических элементов «И 12, 13 соединены с выхода,ми контрольных делителей 9, 10 через логические элементы «НЕ 15, 16. Выходы

логических элементов «И 11, 14 соединены соответственно со входами элементов памяти 5, 6 каждого -канала, а выходы логических элементов «И 12, 13 соединены с другими входами элементов памяти 5, 6. Выходы элементов памяти соединены соответственно со входами установки делителей частоты 1, 2 и схем контроля 3, 4 каждого канала.

Выход делителя частоты 1 через элемент задержки 7 соединен со входом элемента памяти 6, выход делителя частоты 2 через элемент задержки 8 - со входом элемента памяти 5 другого канала.

Работает резервированный делитель частоты следующим образом.

Поскольку оба канала деления работают аналогично, рассмотрим работу одного канала деления. Входная последовательность импульсов поступает на входы делителя частоты 1 и контрольного делителя частоты 9. Импульсы с выхода делителя частоты 1 поступают на входы логических элементов «И И, 12, импульсы с выхода контрольного делителя 9 - на другой вход логического элемента «И 11 и через логический элемент «НЕ 15 на другой вход логического элемента «И 12. При совпадении импульсов на выходах делителя частоты 1 и контрольного делителя частоты 9 появляется сигнал на выходе логического элемента «И 11, который подтверждает состояние элемента памяти 5, соответствующее исправному состоянию канала деления. При несовпадении импульсов на выходах делителя частоты 1 и контрольного делителя 9 появляется сигнал на выходе логического элемента «И 12, который устанавливает элемент памяти 5 в состояние, соответствующее неисправному состоянию канала деления. На выходе элемента памяти 5 появляется сигнал, который устанавливает делитель частоты 1 и контрольный делитель частоты 9 в исходное состояние и держит их в этом состоянии (делители останавливаются).

Если второй канал исправлен, сигнал с выхода делителя частоты 2 через элемент задержки 8 устанавливает элемент памяти 5 в

состояние, соответствующее исправному состоянию своего канала, сигнал на выходе логического элемента памяти 5 исчезает и первый канал деления начинает работать. При этом начальное состояние делителей частоты 1, 2 и контрольных делителей частоты 9, 10 выбирается в соответствии с величиной задержки элементов задержки 7, 8. Иначе говоря, начальное состояние делителей таково, что после восстановления сбившегося канала по исправному оба канала работают синхронно: т. е. импульсы на выходах делителей 1 и 2 появляются одновременно. При сбое второго канала процесс коррекции протекает аналогично.

Формула изобретения

Резервированный делитель частоты, содержащий два канала деления, каждый из которых состоит из делителя частоты и схемы контроля, отличающийся тем, что, с целью коррекции случайных сбоев, в каждый канал деления введен элемент памяти, при этом входы элемента памяти каждого канала подключены к выходам схемы контроля, а выход - ко входу схемы контроля и входу установки делителя частоты, выход которого через элемент задержки соедийен со входом элемента памяти другого канала деления.

ход

Выход 1 канала

llcTipaSностъ

1 канала.

Ислра ностпъ

2 канала

Z напала

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1977 |

|

SU696607A2 |

| Резервированный делитель частоты | 1978 |

|

SU752809A1 |

| Резервированный делитель частоты | 1979 |

|

SU822375A1 |

| Резервированный делитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU805496A2 |

| Многоканальный резервированный генератор | 1982 |

|

SU1072051A1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1984 |

|

SU1156570A1 |

| Резервированное счетное устройство | 1977 |

|

SU705687A1 |

| Резервированный счетчик импульсов | 1981 |

|

SU987815A1 |

| Резервированный формирователь импульсов | 1985 |

|

SU1272510A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

Авторы

Даты

1976-01-15—Публикация

1974-04-02—Подача