142

Изобретение относится к измерительной технике, рассматривающей вопросы определения момента экстремума или фиксации экстремальных значений сигнала, и может быть использовано, например, для определения моментов экстремума при обработке электрического сигнала, получаемого при регистрации пространственного или углового спектра волновых полей (дифракцион-- ных или интерференционных).

Цель изобретения - расширение области применения за счет увеличения точности определения .момента экстре мума и расширения диапазона частот анализируемого сигнала.

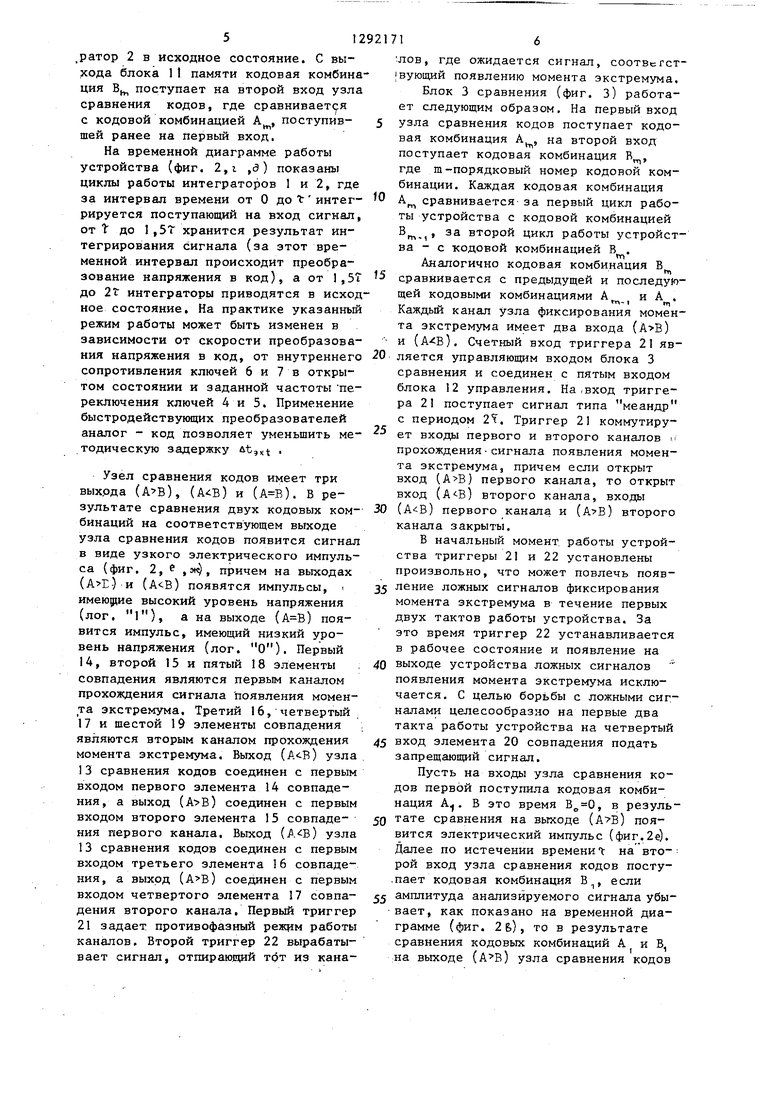

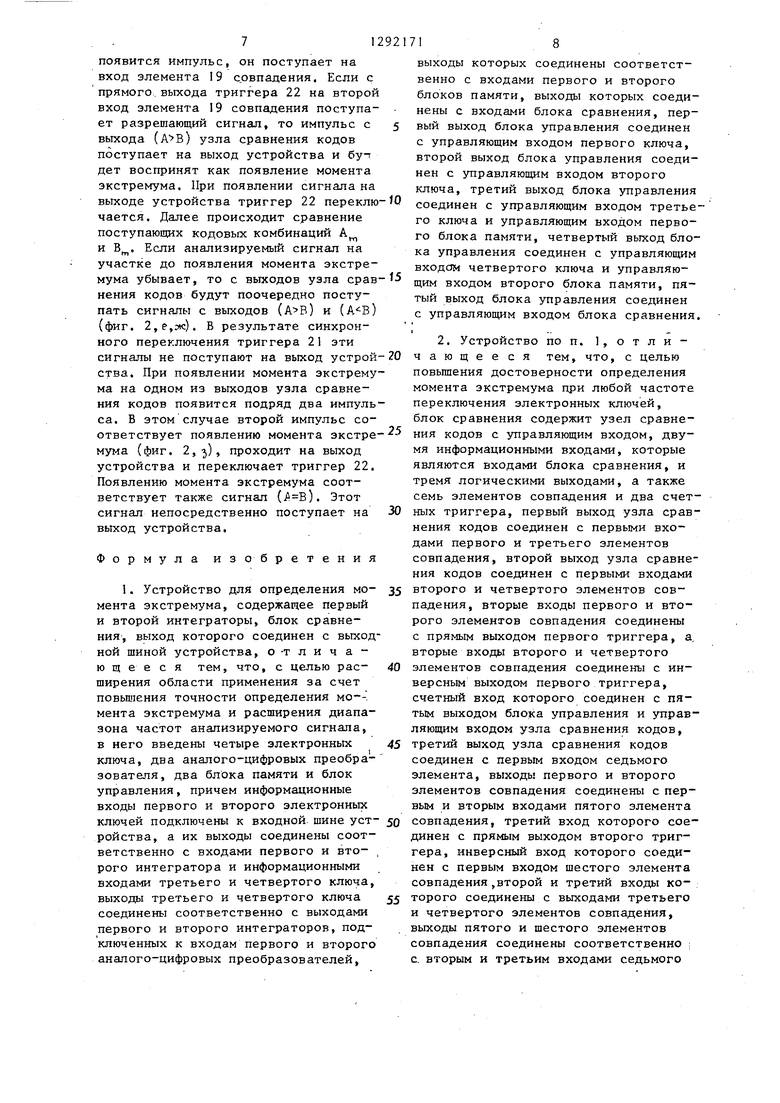

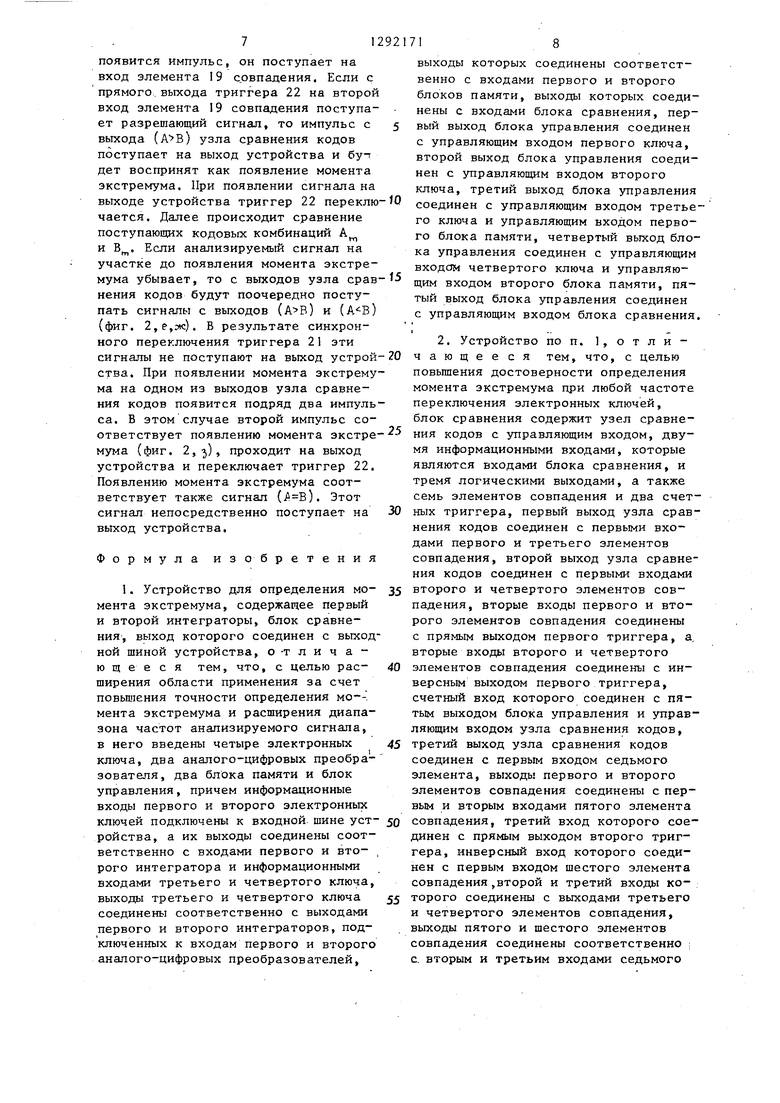

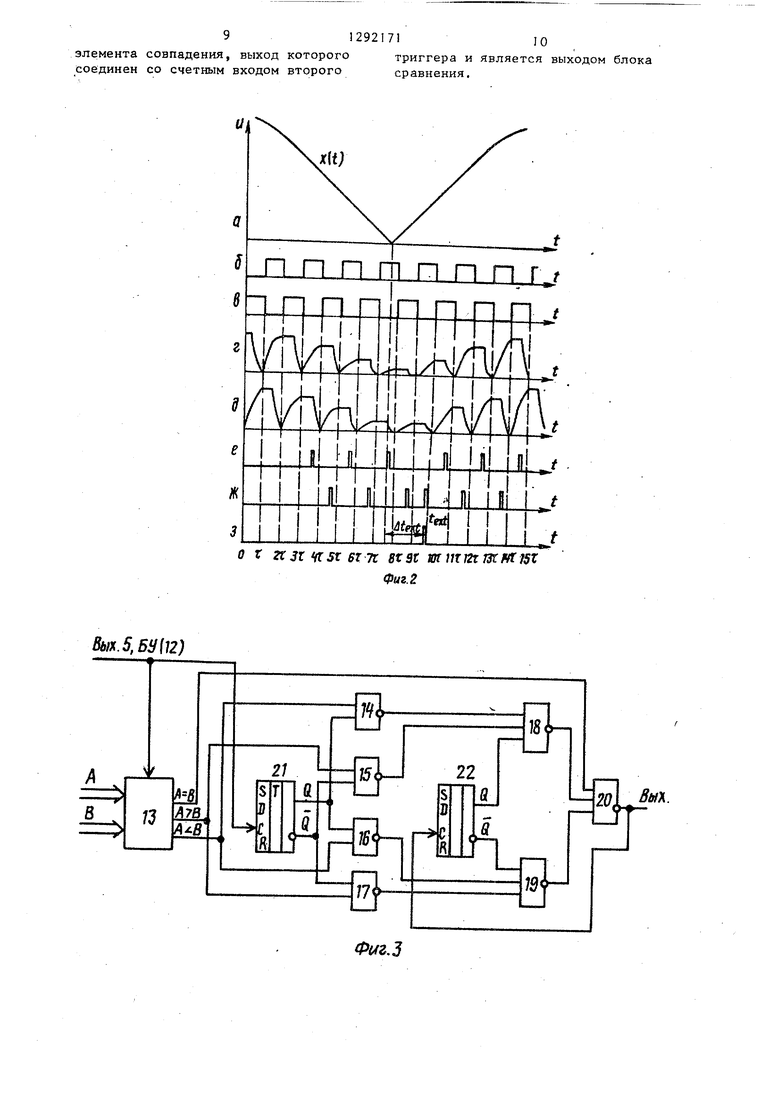

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - схема блока сравнения; на фиг. 4 - схема и временная диаграмма работы блока управления.

Устройство содержит интеграторы 1 и 2, выполненные на операционных усилителях, с конденсатором в петле отрицательной обратной связи, блок 3 сравнения, электронные ключи 4-7, открывающиеся при подаче на управляющий вход напряжения высокого уровня (лог 1), два п разрядных аналого- цифровых преобразователя 8 и 9, два п разрядных блока 10 и 11 памяти, выполненные на D-триггерах, блок 12 управления.

Информационные входы первого 4 и второго 5 ключей соединены и являются входом устройства, а их выходы соединены соответственно с входами первого 1 и второго 2 интеграторов и информационными входами третьего 6 и четвертого 7 ключей, выходы которых соединены соответственно с выходами первого 1 и второго 2 интеграторов и подключены к входам первого 8 и вто- рого 9 аналого-цифровых преобразователей, выходы которых соединены соответственно с входами первого 10 и второго II блоков памяти, выходы которых соединены с входами блока 3 сравнения, его выход является выходом устройства, первый выход блока 12 управления соединен с управляющим входом первого ключа 4, второй выход блока 12 управления соединен с управляющим входом второго ключа 5, третий выход блока 12 управления соединен с управляющим входом третьего ключа 6 и управляющим входом первого

0

0 5

0 5 0 5

712

блока 10 памяти, четвертый выход блока 12 управления соединен с управляющим входом четвертого ключа 7 и управляющим входом второго блока 11 памяти, пятый выход блока 12 управления соединен с управляющим входом блока 3 сравнения.

Блок 3 сравнения (фиг. З) содержит узел 13 сравнения кодов, который имеет два информационных входа А и В, которые являются входами блока сравнения, управляющий вход и три логических выхода (больше, меньше и равно), .а также семь элементов совпадения 14 и два счетных триггера 21 и 22, первый выход () узла 13 сравнения кодов соединен с первыми входами первого 14 и третьего 16 элементов совпадения, второй выход () узла 13 сравнения кодов соединен с первыми входами второго 15 и четвертого 17 элементов совпадения, . вторые входы первого 14 и третьего 16 элементов совпадения соединены с прямым выходом первого триггера 21, а вторые входы второго 15 и четвертого 17 элементов совпадения соединены с инверсным выходом первого триггера 21. счетный вход которого соединен с пятым выходом блока 12 управления и управляющим входом узла 13 сравнения кодов, третий выход А-В узла 13 сравнения кодов соединен с первым входом седьмого элемента 20 совпадения, выходы первого 14 и второго 15 элементов совпадения соединены с первым и вторым входами пятого элемента 18 совпадения, третий вход которого соединен с прямым вы- ходом второго триггера 22, инверсный выход которого соединен с первым входом шестого элемента 19 совпадения, второй и третий входы которого соединены с выходами третьего 16 и четвертого 17 элементов совпадения, выходы пятого 18 и шестого 19 элементов совпадения соединены соответственно с вторым и третьим входами седьмого элемента 20 совпадения, выход которого соединен со счетным входом второго триггера и является выходом блока сравнения.

Блок 12 управления (фиг. 4) содержит, например, задающий генератор 23 тактовых импульсов, к выходу которого подключен вход делителя 24 частоты с коэффициентом деления К, прямой и инверсный выходы которого являются

31

первым и вторым выходами блока 12 управления, третьим и четвертым выходами которого являются выходы соответственно первого 25 и второго 26 элементов 2И, входы первого элемен- та 2И 25 соединены с прямым выходом делителя 24 частоты и прямым выходом (К-l) разряда делителя 2А частоты, выходы второго элемента 2И 26 соединены с инверсным выходом делителя 24 частоты и прямым выходом (К-1) разряда делителя 24 частоты, прямой выход (К-1) разряда делителя 24 частоты является пятым выходом блока 12 управления. В блоки 10 и 1I памяти запись информации с выходов соответствующих аналого-цифровых преобразователей 8 и 9 производится при поступлении на вход блока памяти импуль са (фиг. 4&, г ) с соответствующего выхода блока 12 управления. Указанный импульс поступает на вход формирователя узкого импульса, который по перепаду из низкого уровня напряжения (лог. О) в высокий уровень напряжения (лог. 1) формирует на своем выходе узкий импульс. Выход формирователя узкого импульса соединен с управляющим входом регистра памяти, вьшолненного на триггерах. Информация записывается в регистры памяти при поступлении на их управляющий вход сформированного узкого импульса.

Разрядность блоков 10 и 1I памяти и соответственно число шин в магистралях, соединяющих регистры 10 и 11 памяти.с аналого-цифровыми преобразователями 8 и 9 и с блоком 3 сравнения, определяются разрядностью ана- лого-цифровых преобразователей, которая в свою очередь задается ностью определения момента экстремума,

Устройство работает следующим образом,

Анапизируегфш сигнал x(t) (фиг.2а поступает на информационные входы электронных ключей 4 и 5, С выходов блока 12 управления на управляющие входы электронных ключей 4-7, в регистры 10 и 11 памяти и в блок 3 сравнения поступает последовательность прямоугольных импульсов (фиг, 25,& ), управляющих состоянием ключей. Частота переключения состояний электронных ключей F выбирается много больше частоты анализируемого

14

сигнала x(t) и задается требуемой точностью определения момента экстремума. В начальный момент работы устройства электронный ключ 4 открыт, ключи-5-7 закрыты. Анализируемый сигнал x(t) поступает на вход интегратора 1 и интегрируется им в течение временит 1/2F (фиг. 2,г), по истечении времени Т ключ 4 закрывается, а ключ 5 открывается. Сигнал x(t) поступает на вход интегратора 2 и интегрируется им в течение времени от 2т до ЗТ (фиг. 2,3). Интегратор 1 с момента окончания интегрирования находится в режиме хранения, напряжение с его выхода непрерывно посту- пает на вход аналого-цифрового преобразователя 8, на вьпсоде которого формируется кодовая последовательность, пропорциональная выражению Я

x(t)it. При поступлении импульса

Г

с третьего выхода блока управления

(фиг. 4,5) на вход блока 10 памяти кодовая последовательность А переписывается с выхода аналого-цифрового преобразователя 8 в блок 10 памяти, в это же время ключ 6 открывается и разряжает (закорачивает) конденсатор в петле отрицательной обратной связи интегратора 1, тем са- - мым приводит интегратор 1 в исходное состояние. Преобразование выходного напряжения интегратора 1 в кодовую последовательность и приведение ин- тегратрра 1 в исходное состояние приводится за время от 21 до Зт, в это время сигнал x(t) интегрируется интегратором 2, С выхода блока 10 памяти кодовая комбинация А. поступает на первый вход блока 12 сравнения . За время от 3t до 4f ключ 4 открывается, ключ 5 закрывается, интегратор 1 интегрирует сигнал x(t), интегратор 2 находится в режиме хранения, на выходе аналого-цифрового преобразователя 9 формируется кодоая последовательность , пропорцио- зТ

альная выражению Г x(t)dt.

It По команде с блока 12 управления

(фиг. 4,2), кодовая последовательность В переписывается в блок 11 памяти с выхода аналого-цифрового преобразователя 9, ключ 7 открывается и разряжает конденсатор в петле отрицательной обратной связи интегратора 2, тем самым приводит интег ратор 2 в исходное состояние. С вы- сода блока 1 I памяти кодовая комбинация В. поступает на второй вход узла

сравнения кодов, где сравнивает(5;я с кодовой комбинацией А, поступившей ранее на первьй вход.

На временной диаграмме работы устройства (фиг. 2,г ,5) показаны циклы работы интеграторов 1 и 2, где за интервал времени от О до t интегрируется поступающий на вход сигнал, от t до 1,5Т хранится результат интегрирования сигнала (за этот временной интервал происходит преобразование напряжения в код), а от 1,5Т до 2t интеграторы приводятся в исходное состояние. На практике указанньш режим работы может быть изменен в зависимости от скорости преобразования напряжения в код, от внутреннего сопротивления ключей 6 и 7 в открытом состоянии и заданной частоты переключения ключей 4 и 5. Применение быстродействующих преобразователей аналог - код позволяет уменьшить ме тодическую задержку ut,xt

Г

Уэел сравнения кодов имеет три выхода (А В), () и (), В результате сравнения двух кодовых комбинаций на соответствующем выходе узла сравнения кодов появится сигнал в виде узкого электрического импульса (фиг. 2, Р ,, причем на выходах () и () появятся импульсы, 1 имеющие высокий уровень напряжения (лог. 1), а на выходе () появится импульс, имеющий низкий уровень напряжения (лог. О), Первый 14, второй 15 и пятый 18 элементы совпадения являются первым каналом прохоз адения сигнала появления момента экстремума. Третий 16, четвертый 17 и шестой 19 элементы совпадения являются вторым каналом прохождения момента экстремума. Выход () узла 13 сравнения кодов соединен с первым входом первого элемента 14 совпадения, а выход () соединен с первым входом второго элемента 15 совпадения первого канала. Выход () узла 13 сравнения кодов соединен с первым входом третьего элемента 16 совпадения, а выход () соединен с первым входом четвертого элемента 17 совпадения второго канала. Первый триггер 21 задает противофазный режим работы каналов. Второй триггер 22 вырабатывает сигнал, отпирающий т(5т из кана

ЛОВ, где ожидается сигнал, соотвсгст- |вую1ций появлению момента экстремума. Блок 3 сравнения (фиг. З) работает следующим образом. На первый вход 5 узла сравнения кодов поступает кодовая комбинация на второй вход поступает кодовая комбинация В, где m-порядковый номер кодовой комбинации. Каждая кодовая комбинация О А сравнивается за первый цикл работы устройства с кодовой комбинацией В, за второй цикл работы устройства - с кодовой комбинацией В .

Аналогично кодовая комбинация В 5 сравнивается с предыдущей и последующей кодовыми комбинациями А и А , Каждый канал узла фиксирования момента экстремума имеет два входа () и (), Счетный вход триггера 21 яв- 20 ляется управляющим входом блока 3 сравнения и соединен с пятым входом блока 12 управления. На .вход триггера 21 поступает сигнал типа меандр с периодом 2Т. Триггер 2 коммутиру25

. , ет входы первого и второго каналов и прохождениясигнала появления момента экстремума, причем если открыт вход () первого канала, то открыт вход () второго канала, входы

30 () первого канала и () второго канала закрыты,

В начальный момент работы устройства триггеры 21 и 22 установлены произвольно, что может повлечь появ35 ление ложных сигналов фиксирования момента экстремума в течение первых двух тактов работы устройства. За это время триггер 22 устанавливается в рабочее состояние и появление на

40 выходе устройства ложных сигналов появления момента экстремума исключается, С целью борьбы с ложными сигналами целесообразно на первые два такта работы устройства на четвертый

45 вход элемента 20 совпадения подать запрещающий сигнал.

Пусть на входы узла сравнения кодов первой поступила кодовая комбинация А, В это время , в резуль50 тате сравнения на выходе () появится электрический импульс (фиг,2е). Далее по истечении временит: на вто-: рой вход узла сравнения кодов посту- .пает кодовая комбинация В, если

55 амплитуда анализируемого сигнала убывает, как показано на временной диаграмме (фиг. 2 Е,), то в результате сравнения кодовых комбинаций А и В,

.на выходе

()

узла сравнения кодов

появится импульс, он поступает на вход элемента 19 совпадения. Если с прямого.выхода триггера 22 на второй вход элемента 19 совпадения поступа- ет разрешающий сигнал, то импульс с выхода () узла сравнения кодов поступает на выход устройства и бу-г дет воспринят как появление момента экстремума. При появлении сигнала на выходе устройства триггер 22 переклю чается. Далее происходит сравнение поступающих кодовых комбинаций А и В, Если анализируемый сигнал на участке до появления момента экстремума убывает, то с выходов узла срав нения кодов будут поочередно поступать сигналы с выходов () и () (фиг. 2,e,3tc). В результате синхронного переключения триггера 21 эти сигналы не поступают на выход устрой ства. При появлении момента экстремума на одном из выходов узла сравнения кодов появится подряд два импульса. В этом случае второй импульс соответствует появлению момента экстре мума (фиг. 2,), проходит на выход устройства и переключает триггер 22. Появлению момента экстремума соответствует также сигнал (). Этот сигнал непосредственно поступает на выход устройства.

Формула изобретения

1. Устройство для определения мо- мента экстремума, содержащее первый и второй интеграторы, блок сравнения, выход которого соединен с выходной шиной устройства, о -т л и ч а - ю щ е е с я тем, что, с целью рас- ширения области применения за счет повьачения точности определения мо--. мента экстремума и расширения диапазона частот анализируемого сигнала, в него введены четыре электронных ключа, два аналого-цифровых преобразователя, два блока памяти и блок управления, причем информационные входы первого и второго электронных ключей подключены к входной шине уст- ройства, а их выходы соединены соответственно с входами первого и вто- рого интегратора и информационными входами третьего и четвертого ключа, выходы третьего и четвертого ключа соединены соответственно с выходами первого и второго интеграторов, подключенных к входам первого и второго аналого-цифровых преобразователей.

выходы которых соединены соответственно с входами первого и второго блоков памяти, выходы которых соединены с входами блока сравнения, первый выход блока управления соединен с управляющим входом первого ключа, второй выход блока управления соединен с управляющим входом второго ключа, третий выход блока управления соединен с управляющим входом третьего ключа и управляющим входом первого блока памяти, четвертый выход блока управления соединен с управляющим входом четвертого ключа и управляющим входом второго блока памяти, пятый выход блока управления соединен с управляющим входом блока сравнения

2. Устройство по п. 1, о т л и - чающее ся тем, что, с целью повьшения достоверности определения момента экстремума при любой частоте переключения электронных ключей, блок сравнения содержит узел сравнения кодов с управляющим входом, двумя информационными входами, которые являются входами блока сравнения, и тремя логическими выходами, а также семь элементов совпадения и два счетных триггера, первый выход узла сравнения кодов соединен с первыми входами первого и третьего элементов совпадения, второй выход узла сравнения кодов соединен с первыми входами второго и четвертого элементов совпадения, вторые входы первого и второго элементов совпадения соединены с прямым выходом первого триггера, а, вторые входы второго и четвертого элементов совпадения соединены с инверсным выходом первого триггера, счетный вход которого соединен с пятым выходом блока управления и управляющим входом узла сравнения кодов, третий выход узла сравнения кодов соединен с первым входом седьмого элемента, выходы первого и второго элементов совпадения соединены с первым и вторым входами пятого элемента совпадения, третий вход которого соединен с прямым выходом второго триггера, инверсный вход которого соединен с первым входом шестого элемента совпадения ,второй и третий входы которого соединены с выходами третьего и четвертого элементов совпадения, выходы пятого и шестого элементов совпадения соединены соответственно : с. вторым и третьим входами седьмого

9129217110

элемента совпадения, выход которого триггера и является выходом блока соединен со счетным входом второго сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для определения моментов появления экстремумов | 1989 |

|

SU1661980A2 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для классификации полных циклов | 1985 |

|

SU1330636A1 |

| Устройство для определения достоверности передачи дискретной информации | 1983 |

|

SU1100745A1 |

| Анализатор случайных процессов | 1981 |

|

SU1015393A1 |

Изобретение относится к измерительной технике. Может использоваться для определения момента экстремума или фиксации экстремальных значе- НИИ сигнала при обработке электрического сигнала, получаемого при регистрации пространственного или углового спектра волновых полей (дифракционных или интерференционных). Цель йаоЗ изобретения - расширение области применения - достигается за счет увеличения точности определения момента экстремума и расширения диапазона частот анализируемого сигнала. Для этого в устройство дополнительно введены электронные ключи 4, 5, 6 и 7, два п-разрядных аналого-цифровых преобразователя В и 9, два п-разрядных блока памяти 10 и 11, вьтолнен- ittie на D-триггерах, и блок 12 управления. Кроме того, устройство содержит интеграторы 1 и 2, вьтолненные на операционных усилителях с конденсатором в цепи отрицательной обратной связи, блок 3 сравнения. Устройство состоит из двух каналов, работающих в противофазе и образованных схемными элементами и блоками 4-1- 6-8-10 и 5-2-7-9-11 соответственно. Блок 12 формирует сигналы управления электронными ключами, блоками памяти и блоками сравнения. 1 з.п. ф-лы,4 ил. i (Л dtnaff

§

п п п гл п п п г

о г к31 fr51: бт71 8f9t

фиг. 2

Вых. 5, Si/112)

,3

| Циделко В, Д., Иванов Б | |||

| Р | |||

| Принципы построения определителей экстремумов сигнала | |||

| - Измерения, контроль, автоматизация, 1977, № 1, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1987-02-23—Публикация

1985-07-12—Подача