сумматора в четверичной системе счисления, группа выходов (.)-го одноразрядного четверичного комбинационного сумматора в четверичной системе счисления соединена с группой входов младшего регистра множителя, группы выходов разрядов которого соединены с первым выходом устройства, второй выход которого соединен с группами выходов Л одноразрядных четверичных регистров. 2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что одноразрядный четверичный комбинационный сумматор содержит комбинационный i формирователь суммы,комбинационный формирователь переноса, элемент И, двоичный двухразрядный сумматор, причем первая и вторая информационных входов двоичного двухразрядного сумматора соединены с первой и второй группами входов комбинационного формирователя переноса соответственно и входами двух младших бит четверичной цифры первой и второй .групп одноразрядного четверичного комбинационного сумматора, вхо60399

ды старшего бита четверичной цифры первой и второй групп которого со единены с второй группой входов комбинационного формирователя переноса, третья группа входов которого соединена с выходом элемента И и вькодом переноса двоичного двухразрядного сумматора, первый и второй .выходы суммы которого соединены с первым и вторым входами элемента И и первым

и вторым входами комбинационного

формирователя суммы соответственно, третий вход которого соединен с выходом- элемента И, а четвертый и, пятый входы - с группой входов переноса одноразрядного четверичного комбинационного сумматора (2,3,... 11+1), группа выходов переноса комбинационного формирователя переноса соединена с группой входов переноса 1-го одноразрядного четверичного комбинационного сумматора (1,2,.., Л)«группа выходов комбинационного формирователя суммы соединена с группой выходов т-го одноразрядного четверичного комбинационного сумматора (Л1 1 ,2,...,) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной системе счисления с запоминанием переноса | 1985 |

|

SU1252773A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

1. УСТРОЙСТВО ДЛЯ УМНОЖЕ НИЯ В ИЯБЫТОЧНОЙ ЧЕТВЕРИЧНОЙ СИСТЕМЕ . СЧИСЛЕНИЯ , содержащее регистр множителя, регистр множимого, причем информационные входы регистров множителя и множимого соединены соответственно с входами множителя и множимого устройства, о т л и ч а ю р е е с я тем, что, с целью . повьичения быстродействия j в негр введены П табличных формирователей произведений (П - число разрядов регистров множителя и множимого) и сумматор В четверичной системе счисления, причем группа вькодов старшего разряда регистра мноисителя соединена с первой группой информационных входов табличнь1х формирователей произведений, вторая группа-информационных входов t -го табличного формирователя произведений соединена с группой выходов 1 -го разряда ре гистра множимого. соответственно

Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах различного назначения.

Известно устройство, предназначенное для реализации операции умножения в параллельном двоичном коде, содержащее два регистра, сумматор и формирователь частичных произведений

.причем выход первого регистра соединен через формирователь частичных произведений с входом сумматора, выход второго регистра соединен с вторым входом формирователя частичных произведений рЗ.

Однако устройство имеет малое быстродействие.

известно также устройство умножения, основанное на обработке за один шаг умножения четырех разрядов множителя, содержащее четыре регистра, сумматор, два запоминающих устройства, счетчик, устройство управления, причем выход первого запоминающего устройства через первьй регистр соединен с входом сумматора, выход третьего регистра - с входом четвертого регистра и через второй регистр с входом сумматора, вькод сум матора соединен с входами первого запоминаюв;его устройства и входами третьего и четвертого регистров, второй выход первого запоминающего устройства соединен с входом второго запоминающего устройства, выход второго запоминающего устройства с входом счетчика и устройства управ ления 22.

Однако устройство требует очень большого расхода оборудования и имеет недостаточное быстродействие.

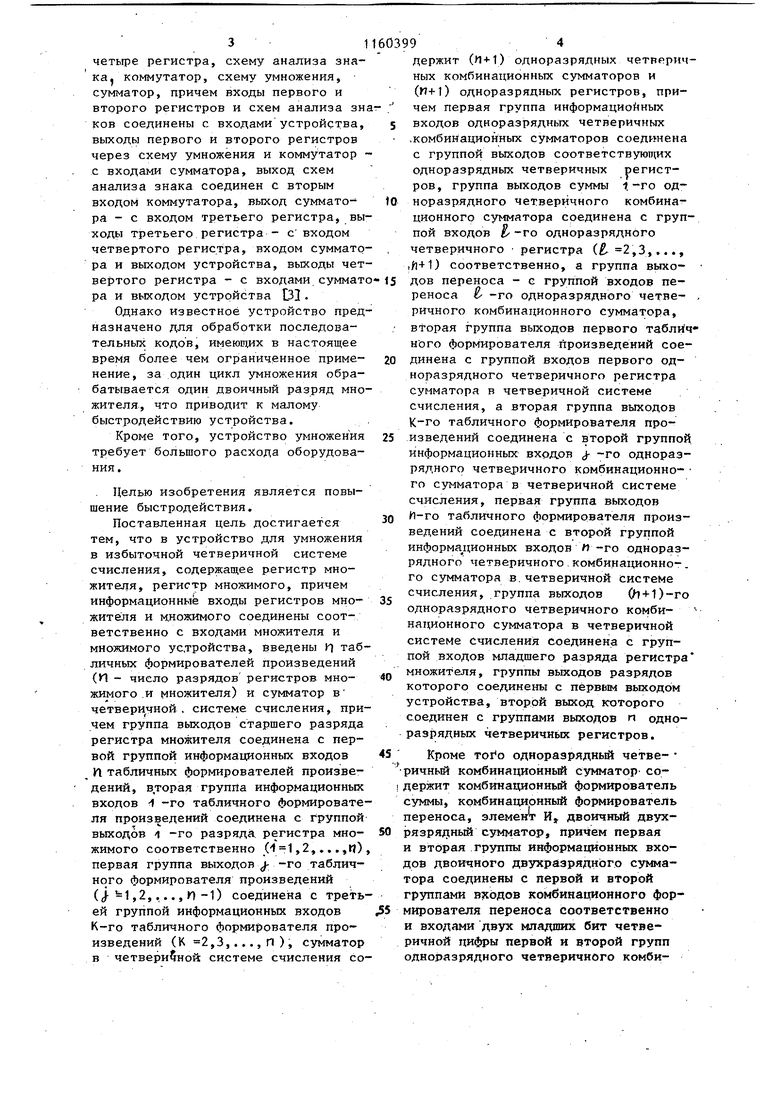

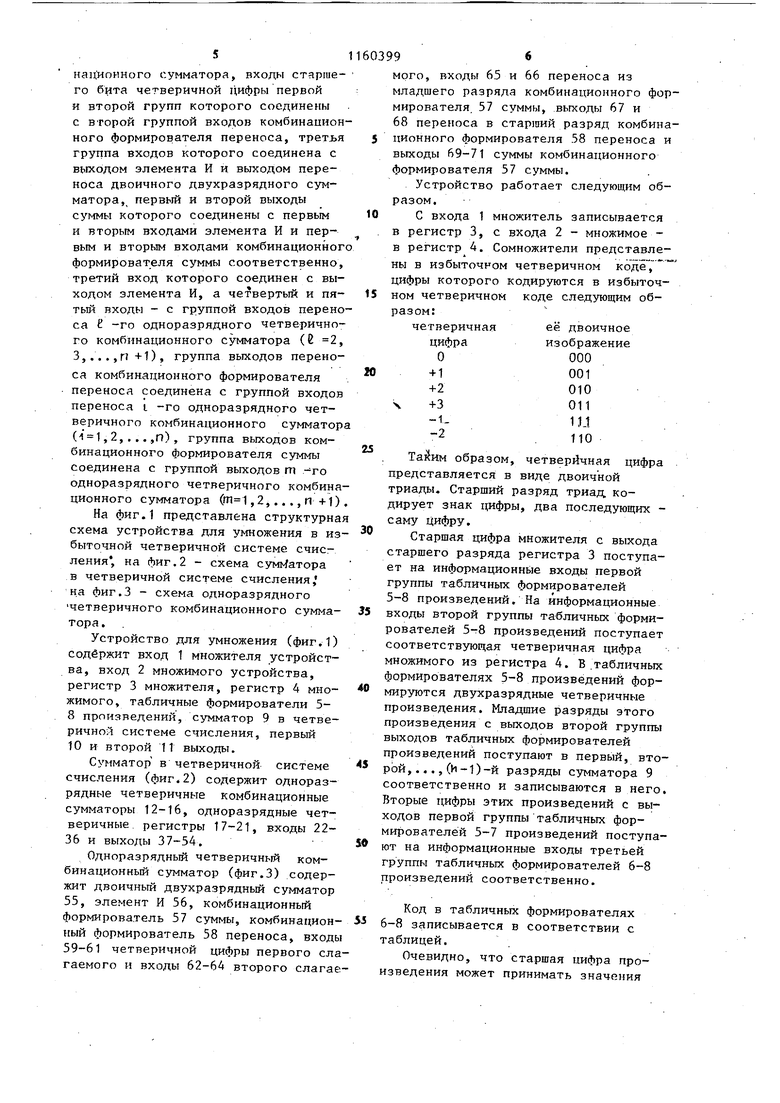

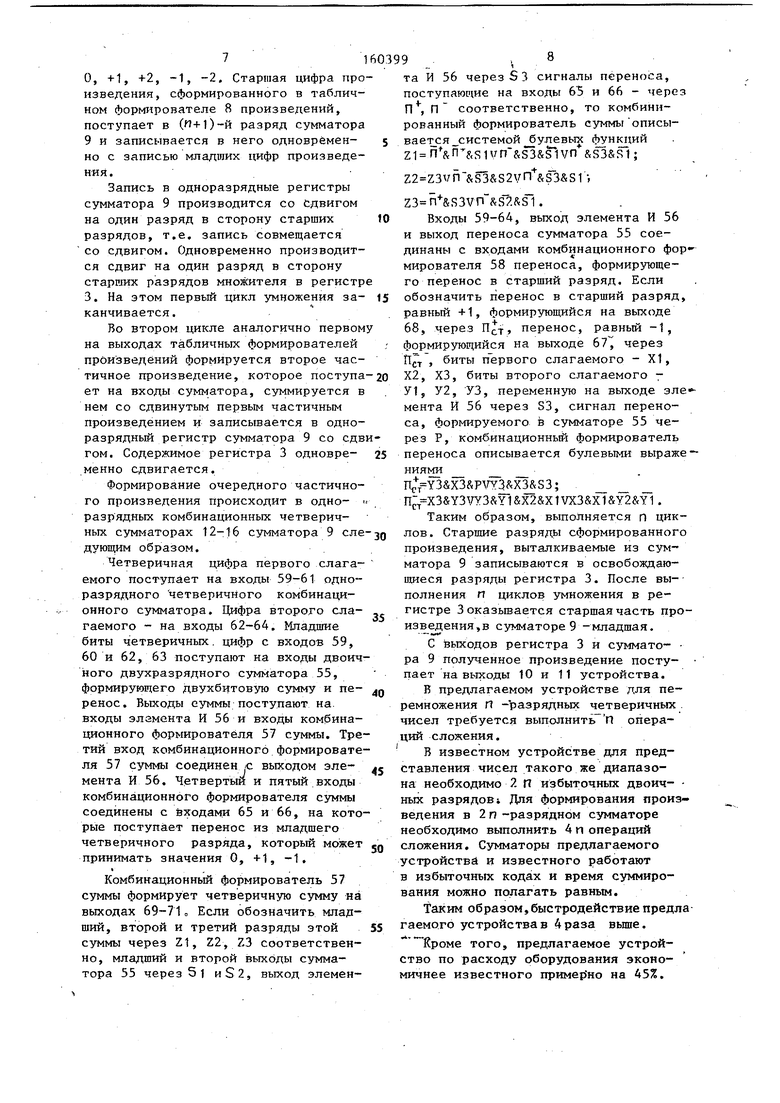

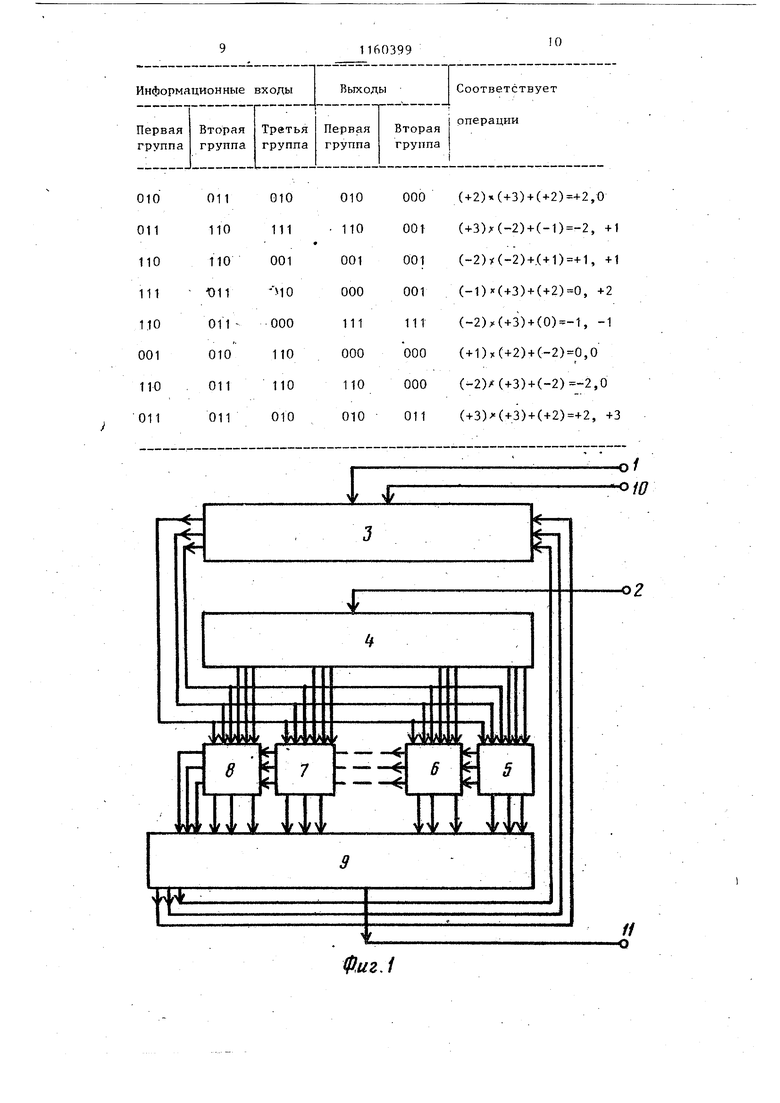

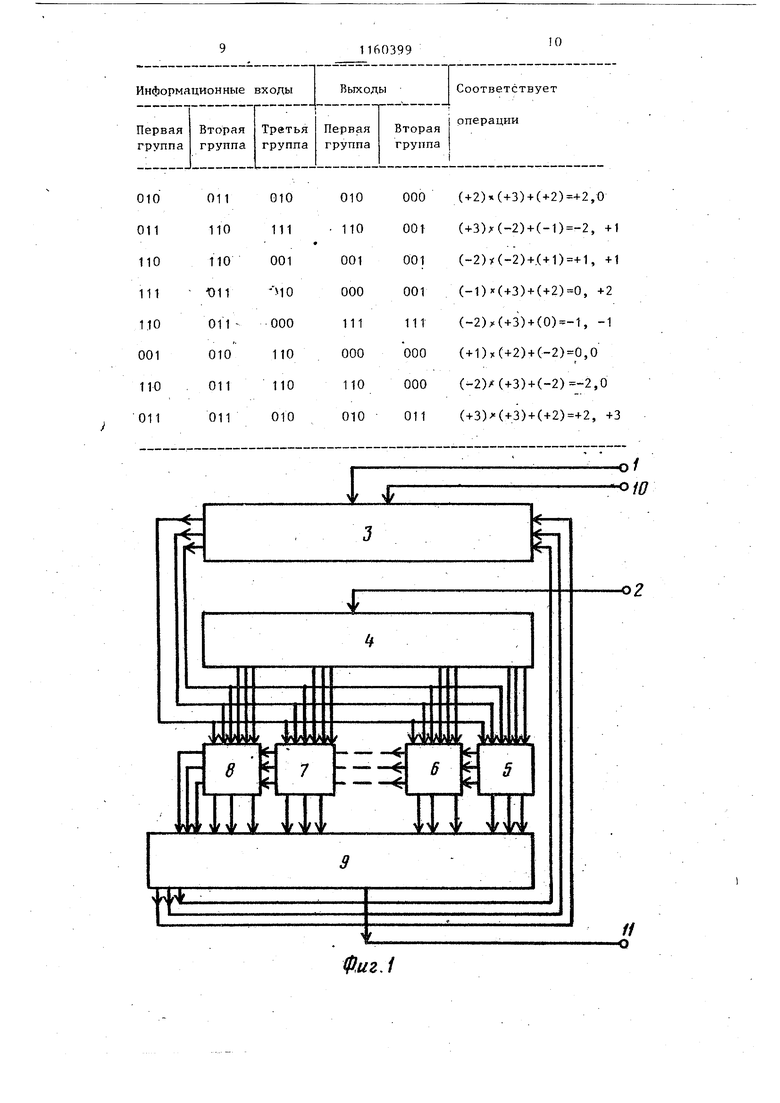

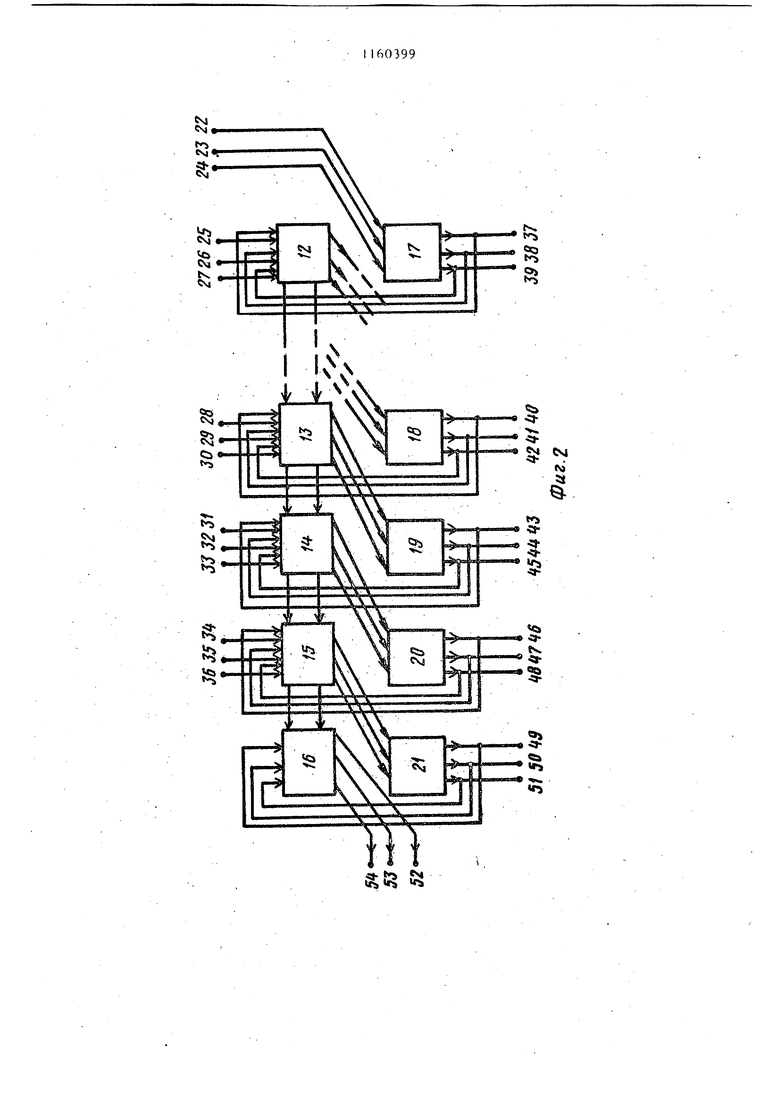

Наиболее близким к изобретению по технической сущности является устройство для умножения в избыточной двоичной системе, содержащее четыре регистра, схему анализа знака, коммутатор, схему умножения, сумматор, причем входы первого и второго регистров и схем анализа зн ков соединены с входамиустройства, выходы первого и второго регистров через схему умножения и коммутатор с входами сумматора, выход схем анализа знака соединен с вторым входом коммутатора, выход сумматора - с входом третьего регистра, вы ходы третьего регистра - с входом четвертого регистра, входом суммато ра и выходом устройства, выходы чет вертого регистра - с входами суммат ра и выходом устройства D3 Однако известное устройство пред назначено для обработки последовательных кодов, имеюп1их в настоящее время более чем ограниченное применение, за один цикл умножения обрабатывается один двоичный разряд мно жителя, что приводит к малому быстродействию устройства. Кроме того, устройство умножения требует большого расхода оборудования. Целью изобретения является повышение быстродействия Поставленная цель достигаемся тем, что в устройство для умножения в избыточной четверичной системе счисления, содержащее регистр множителя, регистр множимого, причем информационные входы регистров множителя и кножимого соединены соответственно с входами множителя и множимого устройства, введены П таб личных формирователей произведений (Л - число разрядов регистров множимого .и множителя) и сумматор в четвери чной . системе счисления, при чем группа выходов старшего разряда регистра множителя соединена с первой группой информа;ционных входов Ц табличных формирователей произведений, вторая группа информационных входов 4 -го табличного формировате ля произведений соединена с группой выходов 1 -го разряда, регистра множимого соответственно (,2,..,ц) первая группа выходов -го табличного формирователя произведений (J--1,2,,..,K)-1) соединена с треть ей группой информационных входов К-го табличного формирователя произведений (К 2,3,...,п), сумматор в четвери 1ной системе счисления со держит (И+1) одноразрядных четверичных комбинационных сумматоров и (и+1) одноразрядных регистров, причем первая группа информациойных входов одноразрядных четверичных .комбинационных сумматоров соединена с группой выходов соответствующих одноразрядных четверичных регистров , группа выходов суммы t-го одноразрядного четверичного комбинационного сумматора соединена с группой входов & -го одноразрядного четверичного регистра ( 2,3,..., ,Й+1) соответственно, а группа выхо- дов переноса - с группой входов переноса t- -го одноразрядного четве- , ричного комбинационного сумматора, вторая группа выходов первого таблйч ного фop fиpoвaтeля произведений соединена с группой входов первого одноразрядного четверичного регистра сумматора в четверичной системе счисления, а вторая группа выходов К-го табличного формирователя произведений соединена с второй группой. информационных входов -го одноразрядного четверичного комбинационно- го сумматора в четверичной системе счисления, первая группа выходов П-го табличного формирователя произведений соединена с второй группой информационных входов « -го одноразрядного четверичного. комби.национно-. го сумматора в. четверичной системе счисления, группа выходов (h+1)-ro одноразрядного четверичного комби- национного сумматора в четверичной системе счисления соединена с группой входов младшего разряда регистра множителя, группы выходов разрядов которого соединены с первым выходом устройства, второй выход которого соединен с группами выходов п одноразрядных четверичньк регистров. Кроме одноразрядный четве- ичный комбинационный сумматор- соержит комбинационньй формирователь уммы, комбинационный формирователь ереноса, элемент И двоичный двухязря ный сумматор, причем первая вторая группы информационных вхоов двоичного двухразрядного сзгммаора соединены с первой и второй руппами входов комбинационного форирователя переноса соответственно и входами двух младших бит четверичной цифры первой и второй групп одноразрядного четверичного комби5наципнного сумматора, входы старшего бита четверичной цифры первой и второй групп которого соединены с второй группой входов комбинацион ного формирователя переноса, третья группа входов которого соединена с выходом элемента И и выходом переноса двоичного двухразрядного сумматора,, первый и второй выходы суммы которого соединены с первым и вторым входами элемента И и первым и вторым входами комбинационног формирователя суммы соответственно, третий вход которого соединен с выходом элемента И, а четвертый и пятый входы - с группой входов перено са е -го одноразрядного четверичного комбинационного сумматора (2 2, 3,.. .,П+1), группа выходов переноса комбинационного формирователя переноса соединена с группой входов переноса i -го одноразрядного четверичного комбинационного сумматор (1 1,2, . .. ,п) , группа выходов комбинационного формирователя суммы соединена с группой выходов m -го одноразрядного четверичного комбина ционного сумматора (,2,.. ., г +1) На фиг.1 представлена структурна схема устройства для умножения в из быточной четверичной системе счисления на Лиг.2 - схема сум1УГатора в четверичной системе счисления, н.а фиг.З - схема одноразрядного четверичного комбинационного сумматора. Устройство для умножения (фиг,1) содержит вход 1 множителя устройства, вход 2 множимого устройства, регистр 3 множителя, регистр 4 множимого, табличные формирователи 58 произведений, сумматор 9 в четверичной системе счисления, первый 10 и второй 11 выходы. Сумматор в четверичной системе счисления () содержит одноразрядные четверичные комбинационные сумматоры 12-16, одноразрядные четверичные регистры 17-21, входы 2236 и выходы 37-54. Одноразрядный четверичный комбинационный сумматор (фиг.З) содерясит двоичный двухразрядный сумматор 55, элемент И 56, комбинационный формирователь 57 суммы, комбинацион ный формирователь 58 переноса, вход 59-61 четверичной цифры первого сл гаемого и входы 62-64 второго слага 96 мрго, входы 65 и 66 переноса из младшего разряда комбинационного формирователя, 37 суммы, выходы 67 и 68 переноса в старший разряд комбинапионноГо формирователя 58 переноса и выходы 69-71 суммы комбинационного формирователя 57 суммы. Устройство работает следующим образом. С входа 1 множитель записывается в регистр 3, с входа 2 - множимое в регистр 4. Сомножители представлены в избыточном четверичном коде, цифры которого кодируются в избыточном четверичном коде следующим образом:её двоичное четверичная изображение цифра 000 001 010 011 1,U 110 Тайим образом, четверичная цифра представляется в виде двоичной триады. Старший разряд триад кодирует знак цифры, два последующргх саму цифру. Старшая цифра множителя с выхода старшего разряда регистра 3 поступает на информационные входы первой группы табличных формирователей 5-8 произведений. На информационные входы второй группы табличньк формирователей 5-г8 произведений поступает соответствующая четверичная цифра множимого из регистра 4. В .табличных формирователях 5-8 произведений формируются двухразрядные четверичные произведения. Младшие разряды этого произведения с выходов второй группы выходов табличных формирователей произведений поступают в первый, второй, ..., (И- 1) -и разряды сумматора 9 соответственно и записываются в него. Вторые цифры этих произведений с выходов первой группы табличных формирователей 5-7 произведений поступают на информационные входы третьей группы табличных формирователей 6-8 произведений соответственно. Код в табличных формирователях 6-8 записывается в соответствии с таблицей. Очевидно, что старшая цифра произведения может принимать значения О, +1, +2, -1, -2, Старшая цифра про изведения, сформированного в табличном формирователе 8 произведений, поступает в (и+1)-й разряд сумматора 9 и записывается в него одноврёменно с записью младших цифр произведения, Запись в одноразрядные регистры сумматора 9 производится со Сдвигом на один разряд в сторону старших разрядов, т.е. запись совмещается со сдвигом. Одновременно производится сдвиг на один разряд в сторону старших разрядов множителя в регистр 3. На этом первый чикл умножения заканчивается. Во втором цикле аналогично первом на выходах табличных формирователей произведений формируется второе частичное произведение, которое поступа ет на входы сумматора, суммируется в нем со сдвинутым первым частичным произведением и записывается в одноразрядный регистр сумматора 9 со сдв гом. Содержимое регистра 3 одновременно сдвигается. Формирование очередного частичного произведения происходит в одноразрядных комбинационных четверичных сумматорах 12-16 сумматора 9 сле дующим образом. Четверичная цифра первого слагаемого поступает на входы 59-61 одноразрядного четверичного комбинационного сумматора. Цифра второго слагаемого - на входы 62-64. Младшие биты четверичных, цифр с входов 59, 60 и 62, 63 поступают на входы двоич ного двухразрядного сумматора 55, формирующего двухбитовую сумму и перенос. Выходы суммы поступают на. входы элемента И 56 и входы комбинационного формирователя 57 суммы. Тре тий вход комбинационного формировате ля 57 суммы соединен с выходом элемента И 56. Четвертый и пятый.входы комбинационного формирователя суммы соединены с входами 65 и 66, на кото рые поступает перенос из младшего четверичного разряда, который может принимать значения О, +1, -1. Комбинационный формирователь 57 суммы формирует четверичную сумму на выходах 69-71 Если обозначить младший, второй и третий разряды этой суммы через Z1, Z2, Z3 соответственно, младший и второй выходы сумматора 55 через 5 1 и$2, выход элемен9та И 56 через S3 сигналы переноса, поступающие на входы 65 и 66 - через П П соответственно, то комбинированный формирователь суммы описывается системой булевых фунгашй Z1 n &n&s1un&S3&Slvn &S3&S1; Z2 Z3vn&S3&S2Vn &S3&S1 V ..RSl. Входы 59-64, выход элемента И 56 и выход переноса сумматора 55 соединаны с входами комбинационного формирователя 58 переноса, формирующего перенос в старший разряд. Если обозначить перенос в старший разряд, равный +1, формирующийся на выходе 68, через перенос, равный -1, формирующийся на выходе 67, через биты первого слагаемого - XI, Х2, ХЗ, биты второго слагаемого У1, У2, УЗ, переменную на выходе эле мента И 56 через S3, сигнал переноса, формируемого в сумматоре 55 через Р, комбинационный формирователь переноса описывается булевыми выражениямиnfVY3&X3&PW3RX3&S3; n.f X3&Y3l.Y3&Y 1 &Х2&Х 1 VX3&X 1 &Y2&Y 1 . Таким образом, выполняется п циклов. Старшие разряды сформированного произведения, выталкиваемые из сумматора 9 записываются в освобождающиеся разряды регистра 3. После вы- полнения п циклов умножения в регистре 3 оказьшается старшая часть произв едения,в сумматоре 9 -младшая, С выходов регистра 3 и суммато- ра 9 полученное произведение посту- пает на выходы 10 и 11 устройства, В предлагаемом устройстве для пеемножения п -разрядных четверичных . исел требуется выполнить П операий сложения, В известном устройстве для представления чисел такого же диапазона необходимо 2 П избыточных двоич- ных разрядов Для формирования произведения в 2 п -разрядном сумматоре необходимо выполнить 4 п операций сложения. Сумматоры предлагаемого устройства и известного работают в избыточных кодах и время суммирования можно полагать равным. Таким образом,быстродействие предла гаемого устройства в 4 раза вьше, Кроме того, предлагаемое устройство по расходу оборудования экономичнее известного примерно на 45%,

Ф,иг.1

61

St 5J. 5256

Т

f

68

58 fi7Фиг.З

59

f

65

57

7f 7b 63

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Способ приготовления консистентных мазей | 1912 |

|

SU350A1 |

| . | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-27—Подача