Ичг бретсчше относится к вычисли- те,пьнс1Й технике и предназначено для ис1(1льзонания в Щ1фровых вычислитель ных магиипах, работающих в избыточной системе счисления.

Цель изобретения - повышение быстродействия.

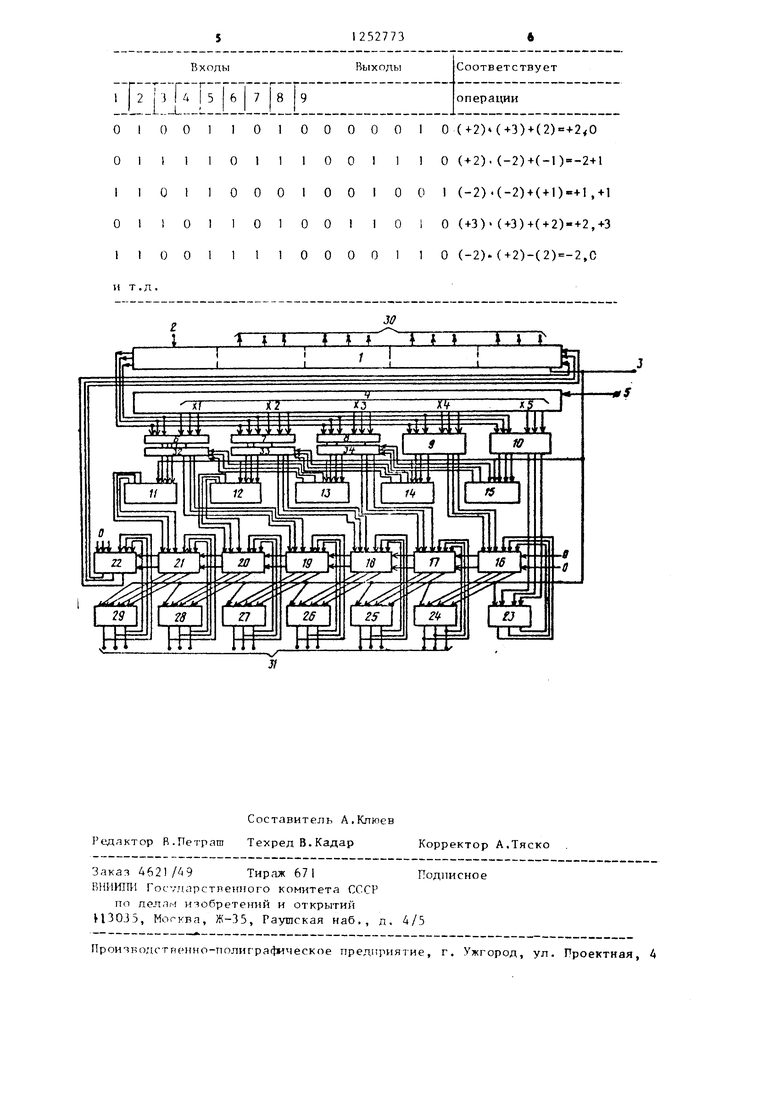

На чертеже представлена схема устройства для умножеьгия в избыточной системе счисления с запоминанием переноса (для ).

Устройство для умножения в избыточной системе счисления с запоми- илнием переноса содержи1г регистр 1 сдвига, вход 2 множителя устройства, тактовый вход 3 устройства, регистр множимого, вход 5 множимого устройстг а, одноразрядные четверичные умножители 6-10, одноразрядные четверичные регистры переноса, одаоразрядные четверичные сумматоры 16-22, одноразрядные четверичные регистры 23-29 суммы, выходы 30 и 31 соответственно старшей и №1с щшей частей нроизведения устройства, двухразрядные четверичные сумматоры 32-34,

Одноразрядные четверичные умножители 6-8 и соответственно двухразрядные четверичные сумматоры 32- 34 могут быть выполнены в виде посто янного запоминающего устройства (ПЗУ В каждом ПЗУ формируется произведение четверичного разряда множителя на ,четверичн1,п 1 разряд множимого плюс четверичный перенос из регистра переноса. Код н ПЗУ записывается в

соответствии с таблицей.

Регистр предназначен для хранения MHOJKHTBjm Y, поступающего с входа 2 устройства. Вход 3 устройства соединен с входом сдвига в сторону старших разрядов регистра 1. Регистр 4 предназначен дпя хранения множимого X, поступаюп .его с входа 5 устройства. Регистры 1 и 4 представляют собой регистры дпя хранения чисел ь избыточном четверичном коде. Для хранения одной четверичной цифры

используется три триггера, t

Цифр1)1 избыточного четверичного

.кода кодируются следующим образом: Четверичная цифра Двоичное изображение

О000

+ 001

+ 2010

-t-3Oil

-1111

-21 10

Перенос из одноразрядных четве- ричных сумматоров 1бт22 может иметь значения 0; +1; -1 .

Устройство работает следующим образом.

Множитель и множимое с входов 2 и 5 соответственно записываются в регистры 1 и Д, Регистры переноса и суммы сброшены в ноль. Дпя отыскания произведения выполнить шесть циклов.

1-й цикл. На выходах умножителей

6-10 формируются произведения старшего разряда множителя Y, , поступающего из регистра 1, на разряды Х/ - Х множимого. Старшие разряды этих

поразрядных произведений (Р, , Р, , РЗ 41 РЯ поступают на входы регистров 11-15 соответственно, младшие - S,, , Sj, , S,, , 841 , пройдя через сумматоры 19, 18, 17 и 16,

поступают на входы регистров 27, 26, 25 и 24; S, поступает на входы регистра 23 непосредственно. По зату- , хании переходных процессов на вход 3 устройства подается сигнал, Р; и

30 Sj записьшаются в указанные регистры. Одновременно содержимое регистра I сдвигается, в его старшем разряде фиксируется следующий разряд множителя Y .

35

2-й цикл. На умножителях 6-10 и сумматорах 32-34 формируются величины У,Х, + П, ; + П„ ; У,Х, + П,, ; У,Х,; У.Х,, где И ,j, , П, , П, - значения переносов, хранящихся в регистрах 13-15 . переноса. Формируются новые значения величин

«2 22 2 1г 72

Sjj . 852 поступает на вход регистра 23. На вход регистра 24 поступает сумма 85, + , на вход регистра 25 - сумма S, + S , на вход регистра 26 - сумма S, + Sjj , на вход ре50 гистра 27 - сумма Sj, + S,, , на вход регистра 28 - величина S,, + П, и на вход регистра 29 поступает 0+П„ , где П„ и П , - значения переносов из регистров 11 и 12 соответственно.

55 По сигналу, поступающему на вход 3, сформированные суммы и переносы за- письгааются в указанные регистры, содержимое регистра 1 сдвигается.

10

31252773

3-й, U- и 5-й циклы выполняются огично циклу,2. Старшие разряды зведения, формирующиеся на вых сумматора 22 в циклах 3-5, сываются в регистр 1.

6-й цикл. На выходах регистра 1, иненных с входами умножителей, - .Поэтому умножители 9 и 10 генеют нули. Переносы П,; , П , П ускаются на выходы суммы без енения, и в сумматорах 17-22 переП, . П„, П„ и П,5 скла- аются с ранее накогтленной суммой ег 1стров 2А-29. Р - Р, в 6-м е не возникают. По сигналу, поающему на пход 3, в регистре 1 Д-х младших разрядах) зафиксируютетыре старших разряда произведеи в регистрах 29, 28, 27, 26, 24 - младшие разряды произведе. Умножение закончено.

(5

20

ус HQ ве га

Г

вх га од то ро ве В1, Пмляв из щ ше од ры ны с пе че вх ра вы ри ти цю чс го не со ри сл ве ря ма вы ря iio го ум но го ма (п су вх од то че не вы то ря с

Формула изобретени

Устройство для умножения в избыточной системе счисления с запоминанием переноса содержащее регистр сдвига, регистр множимо1-о, п одноразрядных четверичных умножителей (п- разрядность операндов), (п-2), двух- разрядньгх четверичных сумматоров, п одноразрядных четверичных регистров переноса, два одноразрядных четверичных сумматора и один однораз- рядный четверичный регистр суммы причем входы множителя и множимого устройства соединены соответственно с информационными входами регистра сдвига и множимого, выход старшего разряда регистра сдвига соединен с первыми входами одноразрядных четверичных умножителей, вторые вхо- ды которых соединены с выходами соответствующих разрядов регистра множимого, выхода одноразрядных четверичных умножителей, кроме п-го и (n-l)-ro, соединены с входами первого слагаемого соответствующих двухразрядных четверичных сумматоров, выходы старшего разряда которых и выходы старшего разряда (п-1)- го и п-го одноразрядных четверичных умножителей соединены соответственно с информационными входами регистров переносов, тактовые входы которых соединены с входом сдвига регистра сдвига и с тактовьпч входом

0

5

0

5

0

0 5 5

0

5

устройства, выходы регистров пере- HQfa с п-г о гто трртий соединены соответственно с входами второго слагаемого двухразрядмых четверичных

;;;;iTOpOB С (п-2)-ГГ) ПО перВЫИ ,

вхол NuiaAHiero разряда pei HCTpa сдвига сое,|;:.:неи с .м.жодом первого одноразрядного четверичного сумматора, вход первого слагаемого которого через первый одноразрядньш чет- веричньо регистр суммы соединен с В1,кодом суммы второго одноразрядно- П четверичного сумматора, выход младших разрядов регистра сдвига является выходом старшей части произведения устройства, о т л и ч а ю- щ е е с я тем, что, с целью повышения быстродействия, оно содержит одноразрядные четверичные сумматоры с третьего по (п+2)-й одноразрядные четверичные регистры суммы с второго по (п+2)-й, причем выходы переноса предьщущего одноразрядного четверичного сумматора соединены с входами переноса последующего одноразрядного четверичного сумматора, выходы cyMMhi одноразрядных четверичных сумматоров с (n-t-2)-ro по третий соединены соответственно с ин- цюрмпциониыми входами одноразрядньЕУ чстнеричнььч регистров суммы с (n-t-1)- го по второй, выходы которых соединены с входами первого слагаемого соотнетствующих одноразрядных четверичных сумматоров, входы второго слагаемого которых соединены соответственно с выходами младшего разряда двухразрядных четперичньсх сумматоров с (п-/-)-го по первый и с выходами второго и первого одноразрядных четверичных регистров пере- iioca, выходы младшего разряда (п-1)- го и п-го одноразрядных черверичных умножителей соединены соответственно с входом первого слагаемого ()- го одноразрядного четверичного сумматора и с информационным входом (п+2)-го одноразрядного регистра суммы, выход которого соединен с входом второго слагаемого (п+2)-го одноразрядного четверичног о cyNfMa- тора, тактовые входы одноразрядных четверичных регистров сумг-1ы соединены с тактовым входом устройства, выход младшей части произвсде1гня которого соединен с П1 гхолами одиираз- рядных четверичных регистров суммы с первого по (Р.+ О-Й.

01001101000001 о(-i-2)(-i-3)-t-(2)

011110111001110(-ь2). (-2)+(-l) -2-t-l

I I О 1 1 О О О 1 О О I О О 1(-2)-(-2) + ( + 1) Ч-1 ,-И

OliOllOlOOllOlO(+3)« (+3)+(-l2),-3

110011110000110(-2)(+2)-(2)-2,0 н т. д .

f

1

J

t 4 г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке универсальных и специализированных вычислительных устройств, предназначенных для обработки цифровой информации. Целью изобретения является повышение быстродействия. Поставленная цепь достигается тем, что в устройство, содержащее регистр сдвига, регистр множимого, одноразрядные регистры переноса, одноразрядные четверичные умножители, двухразрядные четверичные сумматоры, введены одноразрядные четверичные сумматоры и одноразрядные четверичные регистры суммы с соответствующими связями. 1 ил. г (Л

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-01-04—Подача