2. Устройство ПОП.1, oтлйч а ю 1Д е е с я тем, -ЧТО сумматор и избыточной двоичной системе счисления содержит- элемент ИЛИГ элемент НЕ, триггер, первый элемент И, второй элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем nepBfciEa вход сумматора в избыточной двоичной системе счисления соединен с первьм входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом элемента ИЛИ,второй вход которого соединен с вторьм входом сумматора в избыточной двоичной системе .числения и вторым входом элемента ИКЛЮЧАЮЩЕЕ ИЛИ, выход кого,рого соединен с входом триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами первого и второго элементов И, выход элемента ИЛИ соединен с входом элемента НЕ, выход которого соединён с вторым входом первого элемента И, выход которого соединен с первым выходом сумматора в избыточной двоичной системе счисления, второй выход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

1.. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее К-разрядный регистр мнойсимого, К-разрядный регистр множителя, блок элементов И, блок анализа знака,, коммутатор, (К+2)-разрядный регистр результата, причем информационные входы регистра множителя соединены соответственно с входами множителя устройства, информационные входы регистра множимого соединены соответственно с входами множимого устройства, разрядные выходы регистра множителя соединены соответственно с входами первой группы блока элементов И, первый вход блока анализа знака соединен с входом знака множимого устройства, второй : вход блока анализа знака соединен с входом знака множителя устройства, а выход соединен с управлянлцим входом -коммутатора, о.тличающеес я тем, что, с целью его упрощения и получения возможности последовател(Нвго ввода значений множителя старшими разрядами вперед, в него введены второй блок элементов И, сумматор в избыточной двоичной системе счисления, первый К-разрядный комбинационный сумматор, второй (К+1)-разрядный комбинационный сумматор, триггер и регистр коммутации, причем разрядные выходы регистра множимого соединены соответственно с входами первой группы второго блока элементов И, входы второй группы которого соединены с выходом триггера, вход которого соединен с входом множителя устройства, входы второй группы первого блока элементов И соединены соответственно с входа лн множимого устройства, первый выход первого блока элементов И соединен с входом младшего рарряда (К+2)разрядного регистра результата, входы (К+1) старших разрядов которого соединены соответственно с выходами второго (К+1)-разрядного комбинационного су1«1матора, входы первой группы которого соединены соответственно р выходами (К+1) младааих разрядов о (К+2)-разрядного регистра результата ® а входы второй группы - соответстсл венно с выходс1ми первого К-разряадного комбинационного сумматора, вхоДы . первой группы которого соединены соответственно с выходами второго блока эланентов И, а входы второй группы с первого по (К-1)-й соединены соответственно с вторым по К-й выходами первого блока элементов И, вход регистра коммутаЦ ии соединен ел с входом записи .устройства, выходы ;о ел регистра коммутации соединены соответственно с управляющими входами регистра множителя и управляю да щими входами регистра множимого, выход старшего второго (К+1)-разрядного комбинационного сумматора соединен с первым входом сумматора в избыточной двоичной системе счисле1 ния, второй вход которого соединен с выходом старшего разряда (К+2)-разрядного регистра результата, а первый и второй выходы соединены соответственно с первым и вторым входом коммутатора, первый выход которого является выходом положительные значений, устройства, а второй выход выходом отрицательных значений устройства.

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных устройств.

Известно устройство для умножения содержащее регистры множимого и множителя, сумматор, матрицу модулей сложения, блок анализа знака, блок элементов И и блок элементов 2 ИИЛИ tl .

Недостатком данного устройства является невысокое быстродействие, обусловленное невозможностью получения результата старшими разрядами вперед.

Наиболее близким к изобретению по технической сущности является устройство для умножения, содержащее , регистр множителя, регистр множимото, блок анализа, блок элементов И, коммутатор и регистр результата, причем информационные входы регистра множителя соединены соответственно с входами множителя устройства, информационные входы регистра множимо.го соединены соответственно с входам первой группы блока элементов И, первый вход блока анализа знака соеднен с входом знака множимого устройства, второй вход блока анализа знака соединен с входом знака множителя устройства, а выход соединен с управляющим входом коммутатора L23Известное устройство характеризуется сложностью алгоритма вычисления, т.е. большими затратами по оборудова нию, и вводом множителя параллельным кодом.

Цель изобретения - .упрощение устройства и получение возможности последов а тельногб ввода значений множителя старшими разрядами вперед.

Поставленная цель достигается тем, что в устройство введены сумматор

., в избыточной двоичной системе счис- , ления, второй блок элементов И, первый

5 К-разрядный комбинационный сумматор, второй (К+1)-разрядный комбинационный cyMiviaTOp, триггер и регистр коммутации, причем разрядные выходы регистра множимого соединены соотQ ветственно с входами первой группы второго блока элементов И, входы . второй-группы которого соединены с выходом триггера, вход которого соединен с входом множителя устрой ства, входы второй группы первого блока элементов И соединены соответственно с входами множимого устройства, первый .вход первого блока элементов Исоединен с входом млад- шего разряда (К+2)-разрядного регистра резу.пьтата, входы (К+1) старших разрядов которого соединены соответственно с выходами второго (К+1)-раз), рядного комбинационного сумматора, входы первой группы которого соедине5 ны соответственно с выходами (К+1) младших разрядов (К+2)-разрядного, регистра результата, а входы второй ГРУППЫ - соответственно с выходами первого К-разрядного комбинационного

0 румматора, входы первой группы которого соединены, соответственно с выходами второго блока элементов -И, а входы второй группы с первого по (К-1)-й соединены соответственно с

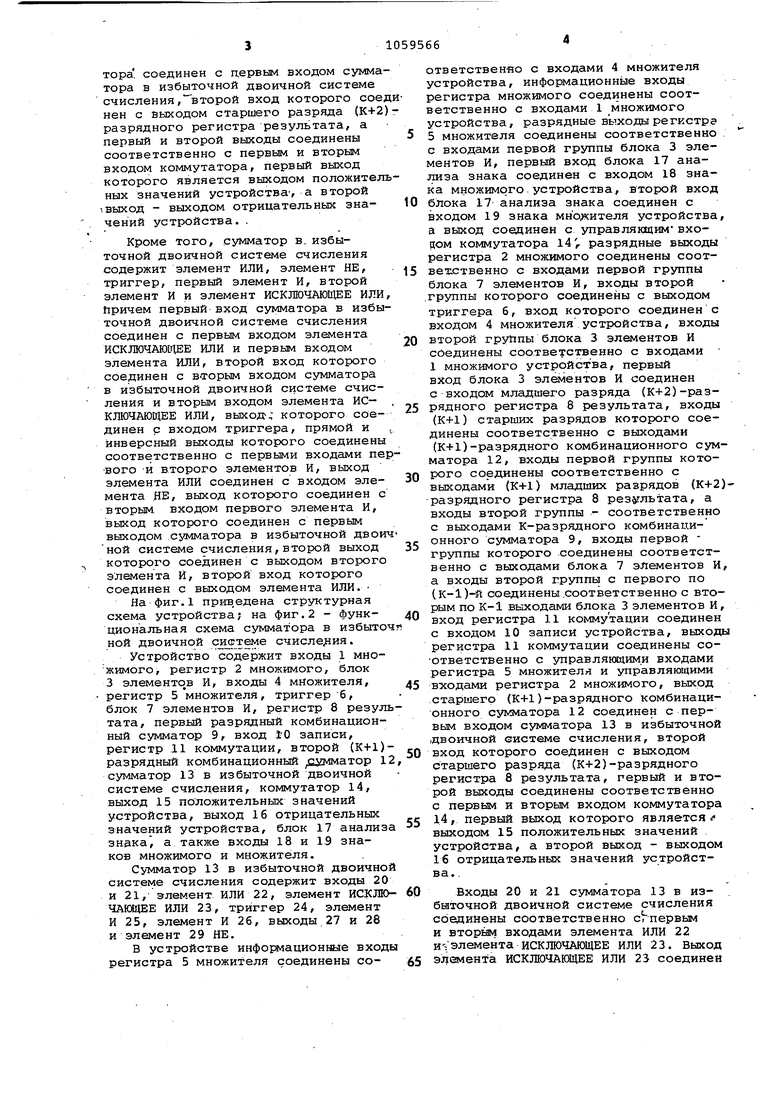

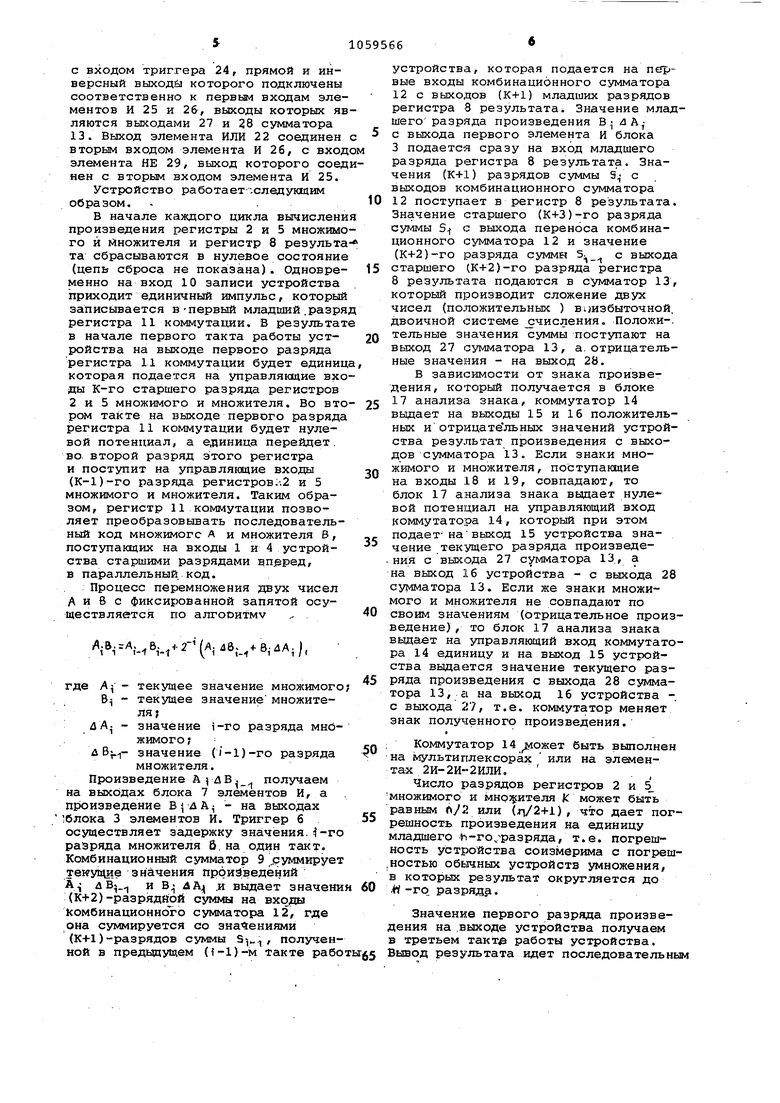

5 вторым по К-й выходами первого блока элементов И, вход регистра коммутации соединен с входом записи устройства, выходы регистра коммутации соединены соответственно с управляюдщими входами регистра множителя и управляющими входами регистра множимого, В1ЛХОД старшего второго (К+1)разрядного комбинационного сумматора соединен с дервым входом сумма тора в избыточной двоичной системе счисления,второй вход которого сое нен с выходом старшего разряда (К+ разрядного регистра результата, а первый и второй выходы соединены соответственно с первым и вторым входом коммутатора, первый выход которого является выходом положите ных значений устройства-, а второй Iвыход - выходом отрицательных значений устройства.. Кроме того, сумматор в. избыточной двоичной системе счисления содержит элемент ИЛИ, элемент НЕ, триггер, первый элемент И, второй элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ причем первый вход сумматора в избы точной двоичной системе счисления соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ И первым входом элемента ИЛИ, второй вход которого соединен с вторым входом сумматора в избыточной двоичной системе счисления и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход-; которого сое динен с входом триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами пе вого -и второго элементов И, выход элемента ИЛИ соединен с входом элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым выходом сумматора в избыточной двои ной системе счисления,второй выход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ. На фиг. 1 прив.едена структурная схема устройства; на фиг.2 - функциональная схема сумматора в избыто ной двоичной «системе счислед1ия. Устройство содержит входы 1 множимого, регистр 2 множимого, блок 3 элементов И, входы 4 множителя, регистр 5множителя, триггер 6, блок 7 элементов И, регистр 8 резул тата, первый разрядный комбинационный сумматор 9, вход 10 записи, регистр 11 коммутации, второй (К+1) разрядный комбинационный ,сумматор 1 сумматор 13 в избыточной двоичной системе счисления, коммутатор 14, выход 15 положительных значений устройства, выход 16 отрицательных значений устройства, блок 17 анализ знака, а также входы 18 и 19 знаков множимого и множителя. Сумматор 13 в избыточной двоично системе счисления содержит входы 20 и 21, элемент ИЛИ 22, элемент ИСКЛЮ ЧАВДЕЕ ИЛИ 23, триггер 24, элемент И 25, элемент И 26, выходы.27 и 28 и элемент 29 НЕ. В устройстве инфорчационшле вход регистра 5 множителя соединены со.ответственно с входами 4 множителя устройства, информационные входы регистра множимого соединены соответственно с входами 1 множимого устройства, разрядные выходы регистра 5 множителя соединены соответственно с входами первой группы блока 3 элементов И, первый вход блока 17 анализа знака соединен с входом 18 знака множимого.устройства, второй вход блока 17 анализа знака соединен с входом 19 знака множителя устройства, а выход соединен с управляющимвходом коммутатора 14, разрядные выходы регистра 2 множимого соединены соответственно с входами первой группы блока 7 элементов И, входы второй группы которого соединены с выходом триггера 6, вход которого соединен с входом 4 множителя устройства, входы второй группы блока 3 элементов И соединены соответственно с входами 1 множимого устройства, первый вход блока 3 элементов И соединен с входом младшего разряда (К+2)-разрядного регистра 8 результата, входы {К+1) старших разрядов которого соединены соответственно с выходами (К+1)-разрядного комбинационного сумматора 12, входы первой группы которого соединены соответственно с выходами (К+1) младших разрядов (К+2)разрядного регистра 8 результата, а входы второй группы - соответственно с выходами К-разрядного комбинационного сумматора 9, входы первой группы которого соединены соответственно с выходами блока 7 элементов И, а входы второй группы с первого по (К-1)-й соединены .соответственно с вторым по К-1 выходами блока 3 элементов И, вход регистра 11 коммутации соединен с входом 10 записи устройства, выходы регистра 11 коммутации соединены соответственно с управлякщими входами регистра 5 множителя и управляющими входами регистра 2 множимого, выход .старшего (К+1)-разрядного комбинационного сумматора 12 соединен с первым входом сумматора 13 в избыточной двоичной системе счисления, второй вход которого соединен с выходом старшего разряда (К+2)-разрядного регистра 8 результата, первый и второй выходы соединены соответственно с первым и вторым входом коммутатора 14, первый выход которого является выходом 15 положительных значений устройства, а второй выход - выходом 16 отрицательных значений устройства. . Входы 20 и 21 сумматора 13 в избыточной двоичной системе счисления соединены соответственно сгпервым и вторш входами элемента ИЛИ 22 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. Выход злояента ИСКЛЮЧАЮЩЕЕ ИЛИ 2S соединен с входом триггера 24, прямой и инверсный выходы которого подключены соответственно к первым входам элементов И 25 и 26, выходы которых яв ляются выходами 27 и 28 сумматора 13. Выход элемента ИЛИ 22 соединен вторым входом элемента И 26, с вход элемента НЕ 29, выход которого соед нен с вторым входом элемента И 25. Устройство работает -.следующим образом. В начале каждого цикла вычислени произведения регистры 2 и 5 множимо го и Множителя и регистр 8 результа та сбрасываются в нулевое состояние (цепь сброса не показана). Одновременно на вход 10 записи устройства приходит единичный импульс, который записывается в-первый младший.разря регистра 11 коммутации. В результат в начале первого такта работы устройства на выходе первого разряда регистра 11 коммутации будет единиц которая подается на управляющие вхо ды К-го старшего разряда регистров 2 и 5 множимого и множителя. Во вто ром такте на выходе первого разряда регистра 11 коммутации будет нулевой потенциал, а единица перейдет, во. второй разряд этого регистра и поступит на управляющие входы (K-l)-ro разряда регистров;-.2 и 5 множимого и множителя. Таким образом, регистр 11 коммутации позволяет преобразовывать последовательный код множимого А и множителя В, поступающих на входы 1 и 4 устройства старшими разрядами вперед, в параллельный, код. Процесс перемножения двух чисел Диве фиксированной запятой осуществляется по алгооитму ) где А - текущее значение множимого Bi - текущее значение множителя4 А- - значение i-ro разряда мнбжимого;л значение (i-l)-ro разряда множителя. Произведение . получаем на выходах блока 7 элементов И, а ПЕЮизведение Bj ЛА - на выходах блока 3 элементов И. Триггер б осуществляет задержку значения.-го разряда множителя б. на один такт. Комбинационный сумматор 9 .руммирует текущее энйчения произведений A-i лв и В ДА.) .и выдает значени (К+2)-разрядной суммы на входы комбинационного сумматора 12, где она суммируется со зна ениями (К+1)-разрядов суммы S,., , полученной в предыдущем (f-l)-M такте рабо устройства, которая подается на пеу вые входы комбинационного сумматора 12 с выходов (К+1) младших разрядов регистра 8 результата Значение младшего разряда произведения В- выхода первого элемента и блока 3 подается сразу на вход младшего разряда регистра 8 результата. Значения (К+1) разрядов суммы S.,- с выходов комбинационного сумматора 12 поступает в регистр 8 результата. Значение старшего (К+3)-го разряда суммы S с выхода переноса комбинационного сумматора 12 к значение (К+2)-го разряда суммн 5;: с выхода старшего (К+2)-го разряда регистра 8 результата подаются в сумматор 13, который производит сложение двух чисел (положительных ) виизбыточной. двоичной системе счисления. Положи-, тельные значения суммы поступают на выход 27 сумматора 13, а. отрицательные значения - на выход 28. В зависимости от знака произведения, который получается в блоке 17 анализа знака, коммутатор 14 выдает на выходы 15 и 16 положительных и отрицательных значений устройства результат произведения с выходов сумматора 13. Если знаки множимого и множителя, поступаквдие на входы 18 и 19, совпадают, то блок 17 анализа знака вьвдает нулевой потенциал на управляющий вход коммутатора 14, который при этом подает навыход 15 устройства значение текущего разряда произведения с выхода 27 сумматора 13, а на выход 16 устройства - с выхода 28 сумматора 13. Если же знаки множимого и множителя не совпадают по своим значениям (отрицательное произведение), то блок 17 анализа знака выдает на управляющий вход коммутатора 14 единицу и на выход 15 устройства выдается значение текущего разряда произведения с выхода 28 сумматора 13, с1 на выход 16 устройства -. с выхода 27, т.е. коммутатор меняет знак полученного произведения. Коммутс1тор быть выполнен на мультиплексорах или на элементах 2И-2И-2ИЛИ. Число разрядов регистров 2 и 5 множимого и мно5 ителя К может быть равным ЛУ2 или () , что дает погрешность произведения на единицу младшего -ь-го.разряда, т.е. погрешность устройства соизмерима с погреш,ностью обьганых устройств умножения, в которых результат округляется до .fi -го. разряда. Значение первого разряда произведения на ,выходе устройства получаем в третьем такте работы устройства. Вывод результата идет последовательным

кодом старшими разрядами вперед.Время вычисления произведения равно n+J тактов.

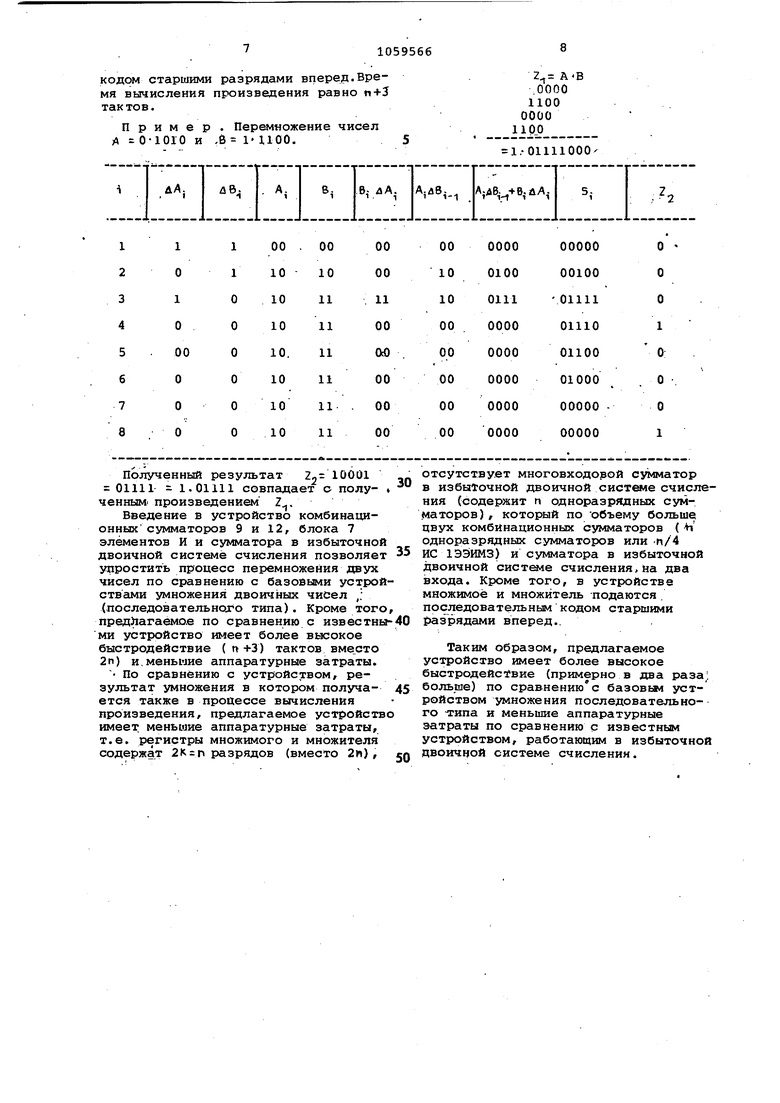

Пример . Перемножение чисел А 0-1010 и , 1100. Полученный результат Z, 10001 01111 1.01111 совпадает с полученным произведением Z. Введение в устройство комбинационных сумматоров 9 и 12, блока 7 элементов И и сумматора в избыточной двоичной системе счисления позволяет упростить процесс перемножения двух чисел по сравнению с базовыми устрой ствами умножения двоичных чисел ,; (последовательного типа). Кроме того предЛагаемо-е по сравнению с известны ми устройство имеет более высокое быстродействие { п+3) тактов вместо 2г1) и.меньшие аппаратурные затраты. По сравнению с устройством, результат умножения в котором получается также в процессе вычисления произведения, предлагаемое устройств имеет меньшие аппаратурные затраты, т.е. регистры множимого и множителя содержат разрядов (вместо 2м),

2 А.в ,0000 1100 0000 llCLp

gjvi.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU550637A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| С, 06 F 7/49, 19.78 (прототип). | |||

Авторы

Даты

1983-12-07—Публикация

1982-07-02—Подача