первой группы соединены с управляющими входами информационных регисров группы и входных шинных формирователей третьей группы, информационные входы которых соединены с выходами D-триггеррв группы и первыми входами элементов И четвертой группы, выходы входных шинных формирователей третьей группы подключены к выходу записи-считывания устройства, выходы элементов И четвертой группы соединены с управляющими входами входных шинных формирователей второй группы, выходы которых соединены с информационными выходами устройства, i-й выход распределителя импульсов подключен к управляющему входу i-ro входного шинного формирователя первой группы и соединен с третьим входом i-ro элемента И первой группы, вторым входом i-го элемента И четвертой группы и синхровходом 1 -го D-триггера группы (i , N , где.- количество элементов в групnej.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приоритетное устройство доступа к общей памяти | 1987 |

|

SU1529239A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство доступа к общей памяти | 1987 |

|

SU1543410A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

| Запоминающее устройство | 1982 |

|

SU1295447A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К ОБЩЕЙ ПАМЯТИ, содержащее тактовьй генератор, группу информационных регистров и группу выходных шин- ных формирователей, причем информационный вход устройства соединен с информационными входами информационных регистров группы, выходы которых соединены с информационными входами выходных шинных формирователей груп- . пы, выходы которых соединены с группой информационных выходов устройства, отличающееся тем, что, с целью повьшения пропускной способности за счет увеличения количества микропроцессоров, совместно использующих общую память в зада«ном интервале времени, оно содержит формирователь одиночного импульса;, распределитель импульсов, первую, вторую, третью и четвертую группы элементов .И, группу дешифраторов, грзтпу D-триггеров, группу входных регистров, , вторую и третью группы входных шинных формирователей, причем вход установки в О распределителя импульсов соединен с входом начальной установки устройства, первый выход тактового генератора соединен с выходом тактовых импульсов ус1 ройства, второй выход тактового генер атора соединен с синхровходом распределителя импульсов и входом формирователя одиночного импульса, выход которого соединен с первыми входами элементов И первой группы, вторые входы которых соединены с первыми входами элементов И второй и третьей групп и выходами дешифраторов (Л группы, группа адресных входов устройства подключена к входам дешифрас торов группы и соединена с информационными входами входных шинных формирователей первой группы, выходы которых соединены с адресным выходом устройства, группа входов записи устройства подключена к вторым вхоа дам элементов И второй группы, выходы которых соединены с управляющими входами входных регистров группы и SP информационными входами D-триггеров 4 группы, группа входов считьюания устройства подключена; к вторым элементов И третьей группы, вы:ходы которых соединены с управля:ющимв входами выходных шинных формирователей, информащюнные входы входных регистров группы подключе,ны к группе информационных входов устройства, выходы входных регистров группы соединены с информацион ными входами шинных формирователей второй группы, выходы эцекентоа И

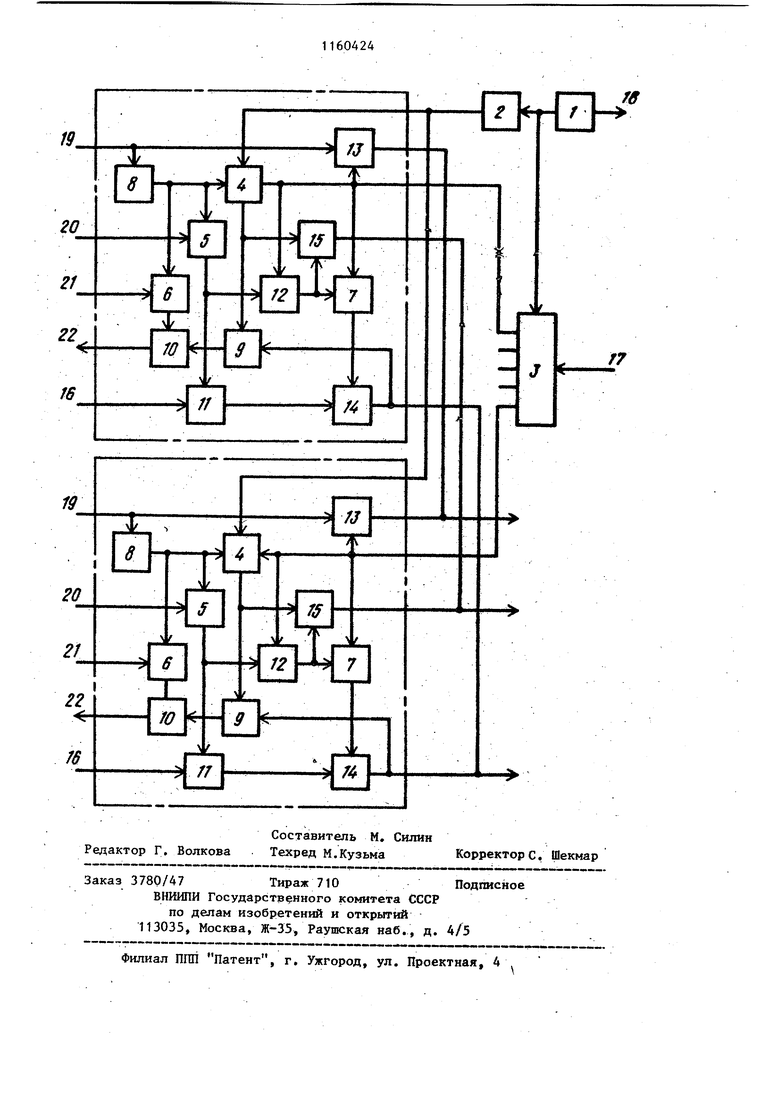

Изобретение относится к цифровой вычислительной технике и предназна чено для использования в мультипроцессорных системах на основе микропроцессоров и микроэвм, Известно устройство, обеспечивающее возможность использования обще памяти двумя микропроцессорами-, содержащее общую память, общий генератор, тактовых импульсов, используемьй для синхронизации работы микро процессоров, приоритетный арбитр, служащий для организации доступа микропроцессоров к общей памяти, а также усилители-формирователи, обеспечивающие связь микропроцессоров с общей памятью lJ. Недостатком этого устройства является снижение производительноети микропроцессоров вследствие простоев при их одновременном обращени к памяти, что связано с вьшолнением микропроцессорами дополнительных тактов ожидания готовности памяти. Наиболее близким по технической сущности к изобретению является уст ройство, содержащее общую память, тактовьш генератор, входной мультиплексор, выходные регистры и выходные усилители-формиров&тели 2 J. Недостатком известного устройства является невозможность его использования более чем-двумя микро;процессорами, Цель изобретения - повьшение пропускной способности устройства за счет увеличения количества микро процессоров, совместно использующих общую память в заданном интервале, времени. Поставленная цель достигается тем, что в устройство для управления доступом к общей памяти, содержащее тактовый генератор, группу информационных регистров и группу выходных шинных формирователей, причем информационный вход устройства соединен с информационными входами информационных регистров группы, выходы которых соединены с информационными входами выходных шинных формирователей группы, выходы которых соединены с группой информационных выходов устройства, введены формирователь одиночного импульса, распределитель импульсов, первая, вторая, третья и четвертая группы элементов И, группа.дешифраторов, группа D-триггеров, группа входных регистров, первая, вторая и третья группы входных шинных формирователей, причем вход установки в О распределителя импульсов соединен с входом начальной установки устройства, первьй выход тактового генератора соединен с выходом тактовых импульсов устройства, второй .выход тактового генератора соединен с синхровходом распреелителя импульсов и входом формиователя одиночного импульса, выход оторого соединен с первыми входами лементов И первой группы, вторые ходы которых соединены с первыми ходами элементов И второй и третьей групп н выходами дешифраторов группы, группа адресных входов устройства подключена к входам дешифраторов группы и соединена с информационными входами входных шинных формирователей первой группы, выходы которых соединены с адресным выходом устройства, группа входов записи устройства подключена к. вторым входам элементов И второй группы, выходы KOTOpbtx соединены с упраЬляюзими входами входных регистров груп пы и информационными входами D-триггеров группы, группа входов считыва,ния устройства подключена к вторым входам элементов И третьей группы, выходы которых соединены с управляющими входами выходных шинных формирователей, информационные входы вход ных регистров группы подключены к группе информационных входов устройства, выходы входных регистров группы соединены с информационными входа ми шинных формирователей второй груп пы, вькоды элементов И первой группы соединены с управляющими входами информационных регистров группы и вход ных шинных формирователей третьей группы, информационные входы которых соединены с выходами D-триггеров гру пы и первыми входами элементов И чет вертой группы, выходы входных шинных формирователей третьей группы подклю чены к выходу записи-считывания устройства, выходы элементов И-четвертой группы соединены с управляющими входами входных шинных формирователе второй группы, выходы кот.орых соединены с информационными выходами устройства, i-й выход распределителя им пульсов подключен к управляющему вхо ду 1-го входного шинного формирователя- первой группы и соединен с третьим входом i-ro элемента И первой группы, вторым входом i-ro элеме та И четвертой группы и синхровходом i-ro D-триггера группы (i 1, N), где .N - количество элементов в группе) . На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит тактовый генератор 1, формирователь 2 одиночног импульса, распределитель 3 импульсов четыре группы элементов И 4-7, груп- пу дешифраторов 8, группу информационных регистров 9, группу выходных шинных формирователей 10, группу вхол ных регистров 11, группу D-триггеров 12, три группы входных шинных формирователей 13-15, группу информационных входов 16 устройства, вход 17 начальной установки, выход 18 Фактовых импульсов тактового генератора, группу адресных входов 19 устройства, группы входов записи 20,и считывания 21 устройства, группу информационных выходов 22 устройства. Устройство работает следующим образом. При поступлении сигнала по входу 17 начальной установки распределитель 3 импульсов устанавливается в исходное состояние. Тактовые импульсы с первого выхода тактового генератора 1 поступают на выход 18 тактовых импульсов, обеспечивая синхронизацию работы подключенных к устройству микропроцессоров. По окончании действия сигнала начальной установки очередной тактовый импульс, поступающий со второго выхода тактового генератора 1, выэьгоает появление сигнала на первом выходе расйределнтеля 3 импульсов. Этот сигнал обеспечивает прохождение на информационный выход, адресный выход и выход записи-считывания устройства сигналов с выходов первых элементов групп соответственно 1315 на время t, равное периоду следования тактовых импульсов на втором выходе тактового генератора 1. Длительность рабочих циклов записи t, и считьшания Гщ-ч используемой в устройстве 16 памяти, должна удовлетворять условию t Q max (t, о цaп цсм ; Тактовые импульсы на втором выЬсоде ;тактового генератора 1 вызывают циклическое изменение сигналов на выходах распределителя 3 таким образом, что пололмтельный сигнал последовательно появляется на всех его выходах от первого до N-ro, обеспечивая поочередно коммутацию на выходы устройства сигналов с выходов элементов соответственно с первого по R-й групп 13-15. Период циклическоо изменения сигналов на выходах распред лителя 3 равен периоду следования сигналов на выходе 18 тактовых импульсов, которые используются для тактирования работы микропроцессоов и определяют длительность их ашинных тактов. Таким образом, за

время длительности машинного такта работающих синхронно микропроцессоров к общей памяти последовательно могут получить доступ все N микропроцессоров.

Появление очередного тактового импульса на втором выходе тактового генератора 1 вызывает появление на выходе формирователя 2 одиночног импульса импульсного сигнала.

Формирователь 2 одиночного импульса обеспечивает вьщолнение временных условий для циклов записи и считывания используемой памяти.

При обращении i-ro мик эопроцессора к общей памяти для записи или считывания данных на соответствующем входе группы 19 адреса устанавливаются сигналы, обеспечивающие появление сигнала на вькоде i-ro дешифратора 8 труппы.

При записи данных в память сигнал с i-ro входа группы 20 проходит на выход i-ro элемента И группы 5 и обеспечивает запись информации в i-й входной регистр группы 11 с i-ro информационного входа группы входов 16 устройства. Появление управляющего сигнала на соответствующем выходе распределителя 3 вызывает подключение к адресному выходу устройства сиг;налов с соответствующего входа группы 19. Одновременно управляющий сигнал устанавливет по С входу соответствующий D-тригер, что приводит к прохождению запсанной в i-й входной регистр группы 11 информации через i-й формирователь группы 14 на информационньй выход устройства.. Импульсный сигнал с выхода формирователя 2 одиночного импульса, проходя через i-й элемент И группы 4 на управляющий вход i-ro формирователя группы 15, вызывает прохождение сигнала с «го информационного входа на выход записи-считывания устройства, обеспечивая запись информации.

Окончание си1нала на i-м входе группы входов 20 вызывает сброс срот5 ветствующего D-триггера с поступлением на его С-вход очередного управляющего сигнала. При этом на выходе соответствующего формирователя группы 15 появляется сигнал, обеспечивающий считывание информации.

При считывании данных на i-м входе Г1эуппы входов 19 устанавливается адрес ячейки памяти, откуда будет осуществлено считывание во время

5 действия импульсного сигнала на выходе формирователя 2 одиночного импульса. В этом случае считанная информация будет занесена в i-й регистр 9 группы по сигналу на его управляющем входе. Появление сигнала на соответствующем входе группы 21.вызывает прохождение хранящейся в соответствующем регистре 9 информации через соответствующий формирователь 10

группы на соответствующий выход 22 устройства.

Применение предлагаемого устройства для управления доступом к общей памяти обеспечивает исключение простоев микропроцессоров вследствие отсутствия конфликтов при обращении к общей памяти, что исключительно важно для управляющих мультимикромашинных систем, работающих в масштабе реального времени, и улучшение использования памяти по сравнению с известными устройствами.

Технико экЬномическ1Й эффект изобQ ретения достигается за счет повышения эффективности использования памяти и производительности мультимикромащинных управляюще-вычислительных систем обработки и передачи данных, е использующих Предлагаемое устройство для организации взаимодействия.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Yue W.I.,Halverson R.P | |||

| Making; the most ot multiprocessing for micrdcoTOp uters.- Comput.Des., 1982, 21, № 2, 10Ы06 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Schmidt R.W | |||

| Asyncronous sampling method simplifies dualport memories.- EDN, 1980, 25, № 8, 201-204 (прототип) | |||

| V - . | |||

Авторы

Даты

1985-06-07—Публикация

1984-01-20—Подача