25

(Л

изменения последовательности доступа процессоров к общей памяти. Устройство содержит генератор 1 импульсов, формирователь 2 одиночного импульса, распределитель 3 импульсов, элементы И 4, 5, 6.и 7, дешифратор 8 адреса, регистр 9 чтения, регистр 10 записи, триггер 11, шинные формирователи 12, 13, 14 и 15, схемы 16 запрета для шин 17 сигнала чтения, схемы 8 запрета для шин 19 сигнала записи, схемы 20 запрета для шин 21 сигналов считываемой информации, схемы 22 запрета для шин 23 записьгоаемой информации, схемы 24 запрета для шин 25 адреса, регистр 26 -приоритета с информационным входом 27 и входом 28 записи, вход 30 начальной установки (сброса) и счетный вход 31 счетчика распределителя 3 импульсов. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в мультипроцессорных системах на основе микропроцессоров и микроЭВМ. Целью изобретения является сокращение аппаратных затрат и расширение функциональных возможностей за счет оперативного изменения последовательности доступа процессоров к общей памяти. Устройство содержит генератор 1 импульсов, формирователь 2 одиночного импульса, распределитель 3 импульсов, элементы И 4, 5, 6, и 7, дешифратор 8 адреса, регистр 9 чтения, регистр 10 записи, триггер 11, шинные формирователи 12, 13, 14 и 15, схемы запрета 16 для шин 17 сигнала чтения, схемы запрета 18 для шин 19 сигнала записи, схемы запрета 20 для шин 21 сигналов считываемой информации, схемы запрета 22 для шин 23 записываемой информации, схемы запрета 24 для шин 25 адреса, регистр приоритета 26 с информационным входом 27 и входом записи 28, вход начальной установки /сброса/ 30 и счетный вход 31 счетчика распределителя 3 импульсов. 2 ил.

Изобретение относится к цифровой вычислительной технике и предназначено для использования в мультипроцессорных системах на основе микропроцессоров (МП) и микроэвм.

Цель изобретения - сокращение аппаратурных затрат и расширение функциональных возможностей за счет оперативного изменения последовательности доступа процессоров к общей памя- ти.

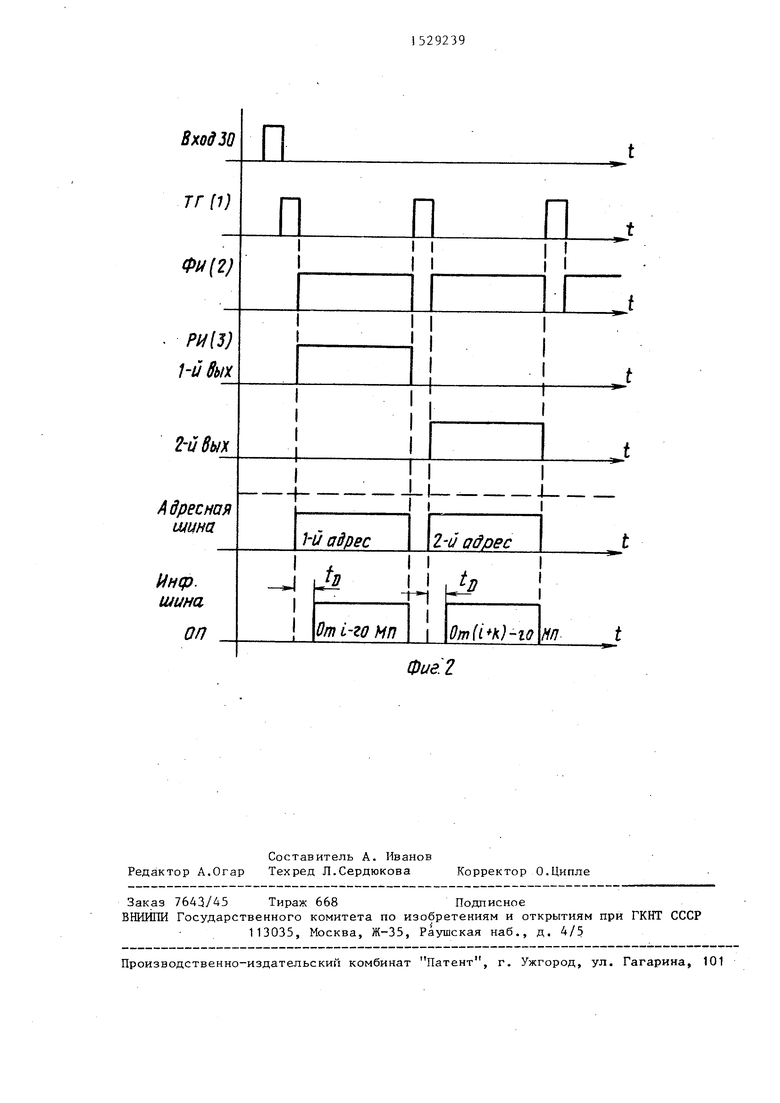

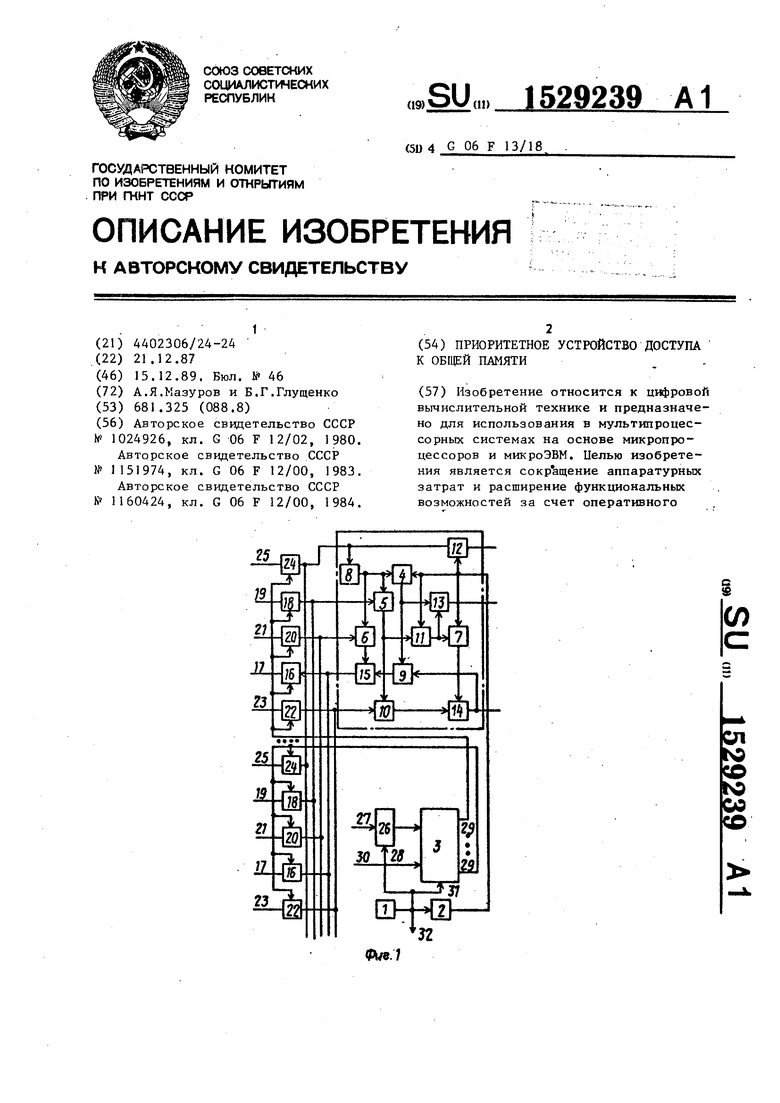

На фиг,1 изображена функциональная схема устройства; на фиг.2 - временные диаграммы его работы.

Устройство (фигЛ) содержит гене7 ратор 1 импульсов, формирователь 2 одиночного импульса, распределитель 3 импульсов, элементы И 4-7, дешифратор 8 адреса, регистр 9 чтения, регистр 10 записи, триггер 11,, шинные форми- рователи , схемы 16 запрета для шин 17 сигнала чтения, схемы 18 запрета для шин 9 сигнала записи, мы 20 запрета для шин 2 считываемой ин- формации, схемы 22 запрета для шин 23 за- письшаемой информации, схемы 24 запрета для шин 25 адреса, регистр 26 приоритета, его информационный вход 27 и вход 28 записи, выходы,29 распределителя импульсов, вход 30 начальной ус- тановки сброса) счетчика распределителя импульсов и счетный вход 31 , счетчика распределителя 3 иг шульсов.

Устройство работает следующим образом о

При поступлении сигнала Сброс на вход 30 счетчик распределителя импульсов переходит в нулевое состояние . Тактовые импульсы генератора 1 с Выхода 32 поступают ча входы ГШ, обеспечивая тактирование подключенных к общей памяти №. По окончании действия сигнала начальной установки очередной импульс генератора с выхода

О 0 5

0

5

генератора 1 вызывает появление еди- нии)1 в счетчике распределителя 3 импульсов по входу. 3 5 а по входу 28 разрешает занесение в регистр 26 кода приоритета по входу 27.

Работу распределителя импульсов на три выхода можно представить в виде . трех уравнений для Y g Ч сывающих структуру комбинационной схемы распределителя импульсов. Первые три двоичных разряда обозначают (содержание) состояние регистра 26, а следующие два - состояния счетчика :

Y 00101V0100iVOniOV1001.lv 101 11-V 11 010;

Yj 00110 V 0101 1 V 0110 У lOOOlV 101 0 VllOl 1 ;

Y, - 001 И V 01010 V О 1 1 V lOOlOV 10101 V 11001.

После занесения в регистр 26 кода приоритета и едршицьг в счетчик распределителя на вькоде распределителя, соответствующем Ш с максимальным приоритетом, появляется единичньй сигнал, который открывает схемы запрета, связанные с этим выходом распределителя, В резу.пьтате МП с выс- приоритетом оказывается подключенным к входам 17, 19; 21, 23, 25 устройства, но еще отключен от общей оперативной памяти (ООП) шинными формирователями 12-15. Это подключение, происходит на время , равное периоду следования импульсов генератора 1, Длительность рабочих диклов записи С5,ц и считывания t - в.общей, оперативной памяти должна удовлетво- рят соотношению tp j, max(, t:) ,

По следующему импульсу генератора увеличивает на. единицу свое содержание счетчик распределителя, вновь

заносится по входу 27 код приоритета и на одном из выходов распределителя импульсов появляется един ичный сигна (импульс), который открьшает следующую группу схем запрета и подсоединяет очередной МП к входным полюсам устройства. Так, по очереди, в соответствии с приоритетом подключаются все МП к ООП, Период пиклического изменения сигналов на выходах распределителя 3 равен периоду следования . сигналов на выходе 32 генератора импульсов, которые используются для тактирования работы МП и определяют длительность их машинных тактов.

Появление очередного тактового импульса на втором выходе генератора 1 вызывает появление на выходе формирователя 2 импульсного сигнала. Формирователь 2 обеспечивает,выполнение нременных условий для циклов записи и считывания используемой памяти.

При обращении i-ro МП (i 1, N, где N - количество подключенных к устройству МП) к ООП для записи или считывания данных на i-м вьсходе распределителя появляется единичный сиг- ib:pi, который открьшает i-ю группу схем запрета, и к входу устройства пказьюаются подсоединены (от i-ro МП) 1П1на 25 адреса, шина 19 сигнала запи- iin, шина 7 сигнала чтения, шина 21 считываемой из ООП информации и шина 2 записываемой в ООП информации.

Адрес от i-ro МП поступает по шипе 25 адреса через схему 24 запрета 111 вход шинного формирователя 12. По управляющему входу шинный формирователь 12 открыт сигналом с выхода формирователя 2, и за время длительности этого сигнала адрес через шинный формирователь 2 передается на адрес - ную шину ООП (фиг. 2).

При записи данных в ООП сигнал записи поступает на i-й вход 19 и через схему 18 запрета, открытую сигналом с 1-го выхода распределителя 3 импульсов, на вход элемента И 5, открытый по второму входу сигналом с дешифратора 8 адреса, и разрешает занесение информации в регистр 10 Записи.

Информация, подлежащая записи с выхода i-ro МП, поступает на i-й вход 23 и через-схему 22 запрета на регистр 10.

Сигнал с элемента И 5 поступает также на вход триггера 11 и записьша0

5

0

5

0

5

0

5

0

ет ся в него сигналом по входу записи с формирователя 2.

С выхода триггера единичный сигнал поступает на вход элемента И 7, открытый по второму входу сигналом с |форм ирователя 2. С выхода элемента Н 7 Управляющий единичный сигнал разрешает прохождение информации, подлежащей записи, с регистра 10 через шинный формирователь 14 на информацион ные щины в ООП.

С выхода дешифратора 8 адреса единичный сигнал поступает на вход элемента И 4, открытый по второму входу сигналом с формирователя 2, С выхода элемента И 4 единичный йигнал поступает на вход шинного формирователя 13, на второй вход которого подан разрешающий сигнал с выхода триггера. С выхода шинного формирователя 13 единичный сигнал в качестве сигнала Запись, передается на шину записи- считьшания в ООП.

Так, при записи в ООП передается сигнал записи (единичный), код адреса на адресную шину ООП и информация, . подлежащая записи на информационную шину ООП. При считьюании информации i-M МП из ООП из i-й ш-ине 19 записи присутствует нулевой сигнал (так как запись отсутствует) , которьй передается через схему 18 запрета на элемент И 5, с выхода которого этот нулевой сигнал поступает на информаци- онньй вход триггера, на выходе которого также появляется нулевой сигнал, который передается на управляющий .вход шинного формирователя 13. С его выхода нулевой сигнал в качестве сигнала Считывания передается на управляющую шину записи-считьшания в ООП.

Передача кода адреса на шину адреса в ООП при считьвании происходит так же, как и при записи информации, т.е. код адреса по i-й шине 25 адреса через i-ю схему 24 запрета поступает на шинный формирователь 12, открытый единичньт сигналом с формирователя 2. С шинного формирователя 12 адрес передается на адресную шину ООП.

Прочитанная по этому адресу информация по информационной шине ООП поступает на Вход регистра 9 чтения. На его управляющий вход поступает разрешающий сигнал по цепочке: i-й вход 23, дешифратор 8 адреса, элемент

;И 4 (открытьй по второму входу С1-1гна- лом с формирователя 2). По сигналу с ;выхода элемента И 4 прочитанная из ЮОП информация заносится врегистр 9.

Сигнал Считьюание поступает на i-й вход 21 через схему 20 запрета на .элемент И 6 (на второй вход которого поступает единичный сигнал с выхода деши||ратора 8 адреса). С выхода эле- мента И 6 разрешающий сигнал разре- пает выдачу прочитанного из ООП и занесенного на регистр 9 числа через пинный формирователь 15 на i-ro шину 17 через i-то схему J6 запрета,

Формула изобретения Приоритетное устройство доступа к эбщей памяти, содержащее генератор импульсов, формирователь одиночного импульса, распределитель импульсов, дешифратор адреса, триггер, четыре элемента И, четыре шинных формирователя, регистр записи и регистр чтения причем выход генератора ге пульсов

соединен с входом формирователя одиночного импульса и входом распределителя импульсов и является тактовым выходом устройства для тактирования процессоров, выход формирователя оди- ночного импульса соединен с первыми входами первого и второго элементов И, Входом разрешения первого шинного формирователя и входом установки триггера, выход дешифратора адреса соединен с вторым входом первого элемента И и первьин входами третьего и четвертого элементоь И, выход первого элемента И соединен с входом I разрешения-второго шинного формирова1теля и входом записи регистра чтения, :второй ВХОД второго элвмента И-сое- динен с прямым выходом триггера и ин- :формаи ионным .-входом второго шинного формирователя, выход второго элемента И соединен с входом разрешения третьего шинного формирователя, выход которого является информационным вхо- ом-вьгходом устройства и соединен с информационным входом регистра чте- ния, информационный выход которого соединен с одноименным входом четвертого шинного формирователя, выход третьего элемента И соединен с информационным входом триггера и входом записи регистра записи, выход которо го соединен с информационным входом третьего шинного формирователя, выход четвертого элемента И соединен с вхо

. .

|Q (5

20 , 25

зОQ д5

35

55

дом разрешения четвертого шинного .формирователя, выходы первого и второго шинных формирователей являются выходами адреса и записи-считьшания устройства соответственно, о т л и - чаю.щееся тем. что, с целью сокращения аппаратурных затрат и расширения его функциональней .возможностей за счет оперативного изменения последовательности доступа процессоров к общей памяти, оно содержит группу схем запрета адреса,.группу схем запрета сигнала записи, группу схем запрета сигнала чтения, группу схем запрета считьюаемой информации, группу схем запрета записьшаемой информации и регистр приоритета, причем k-й адресный .вход устройства (k 1 , N, где 1 - количество подключаемых к устройству процессоров) соединен с входом k-й схемы запрета адреса группы, выходы всех схем запрета адреса группы соединены с инЛормаци- онными входами дешифратора адреса и первого шинного формирователя, k-й вход сигнала записи устрюйства соединен с входом k-й схемы запрета сигнала записи группы, выходы схемы запре- та сигнала записи группы соединены с вторым входом третьего элемента-И, k-й вход сигнала чтения устройства соединен с входом k-й схемы запрета сигнала чтения группы, выходы схем запрета сигнала чтения группы соединены с вторым входом четвертого элемента И, k-й выход информации устройства соединен, с выходом k-й схемы запрета считываемой информации группы, входы схем запрета считываемой информации группы соединены с информапирн- ным выходом четвертого шинного „формирователя, k-й информационный вход устройства соединен с входом схемы запрета записываемой информации группы, выходы схем запрета записьшаемой информации группы соединены с информационным Входом регистра записи, вход приоритета устройства соединен с информацион|1ьп-1 входом регистра приоритета, выход которого соединен с .входом распределителя импульсов, вход сброса которого соединен с одно- именньм входом устройства, вход записи регистра .приоритета соединен с выходом генератора импульсов, вход разрешения k-x схем запрета всех групп соединен с k-м выходом распределителя импульсов«

Фиг:2

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система доступа к памяти | 1983 |

|

SU1151974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления доступом к общей памяти | 1984 |

|

SU1160424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1987-12-21—Подача