1129

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для цифровой обработки сигналов, в частности для цифровой фильтрации в различных цифровых комплексах.

Цель изобретения - повышение быстродействия адресного устройства.

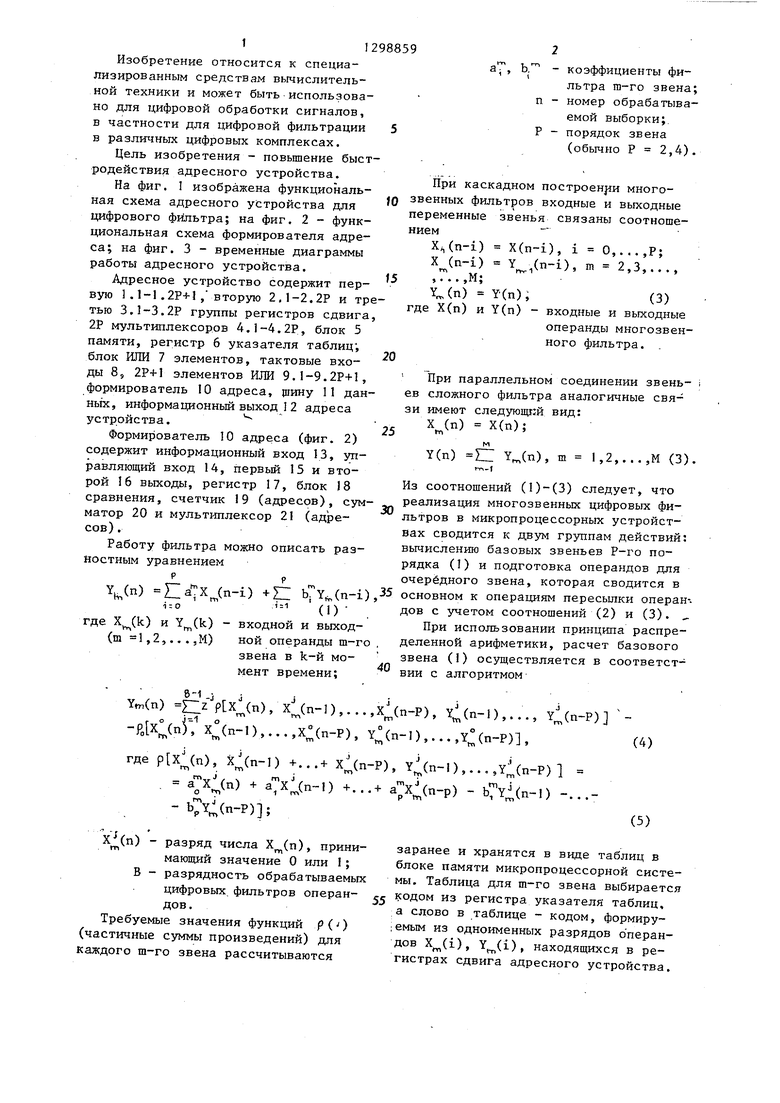

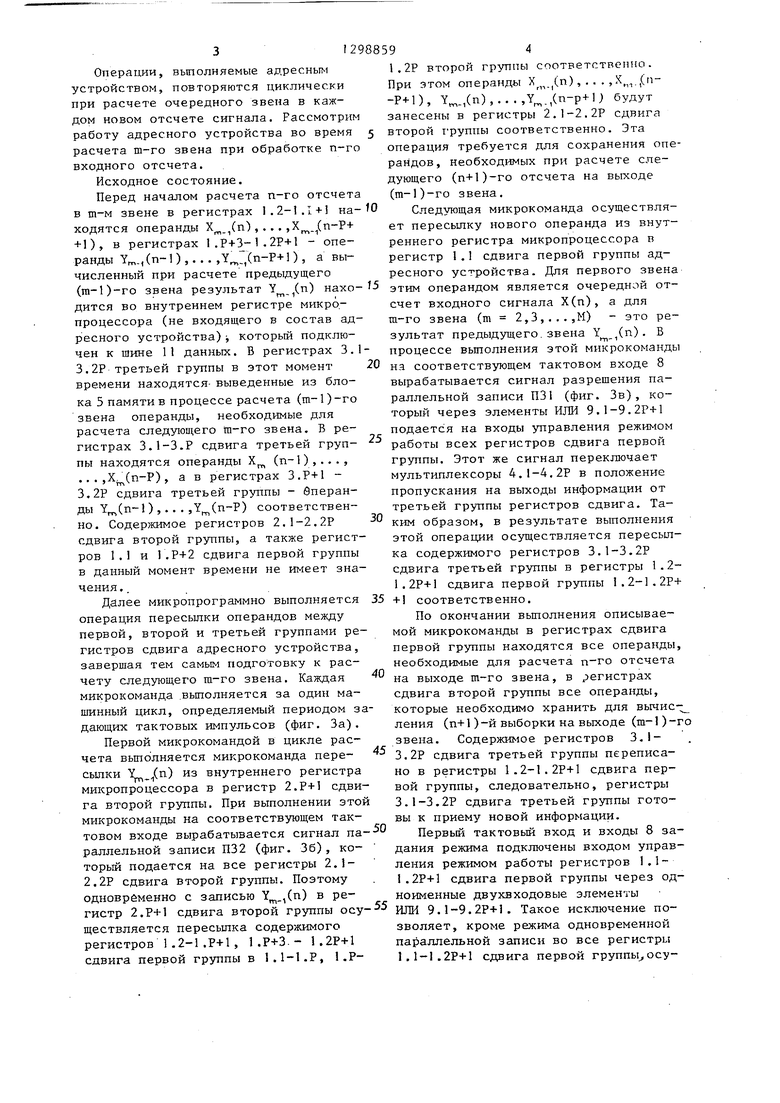

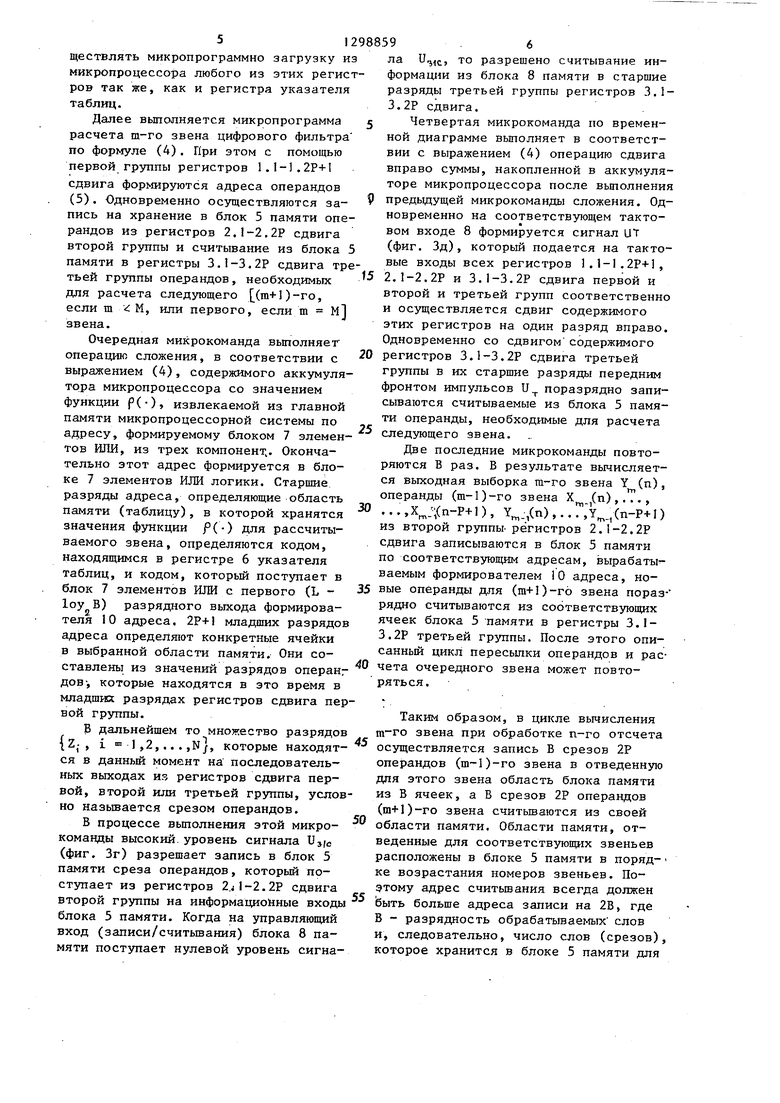

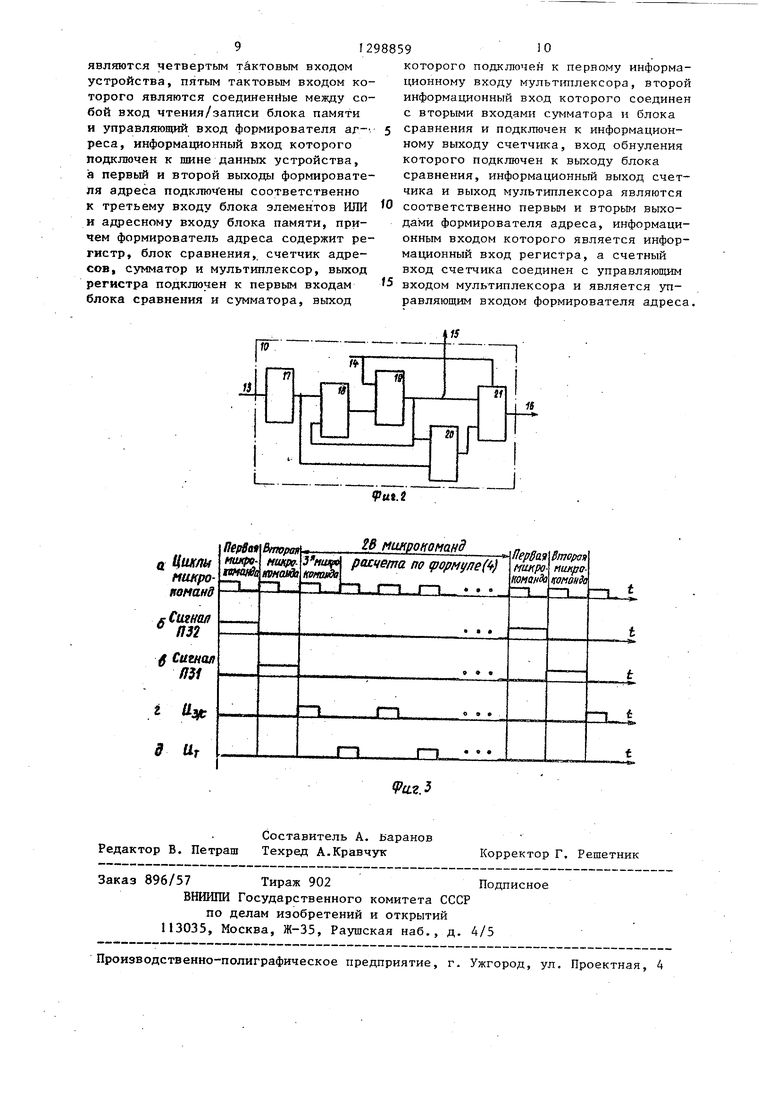

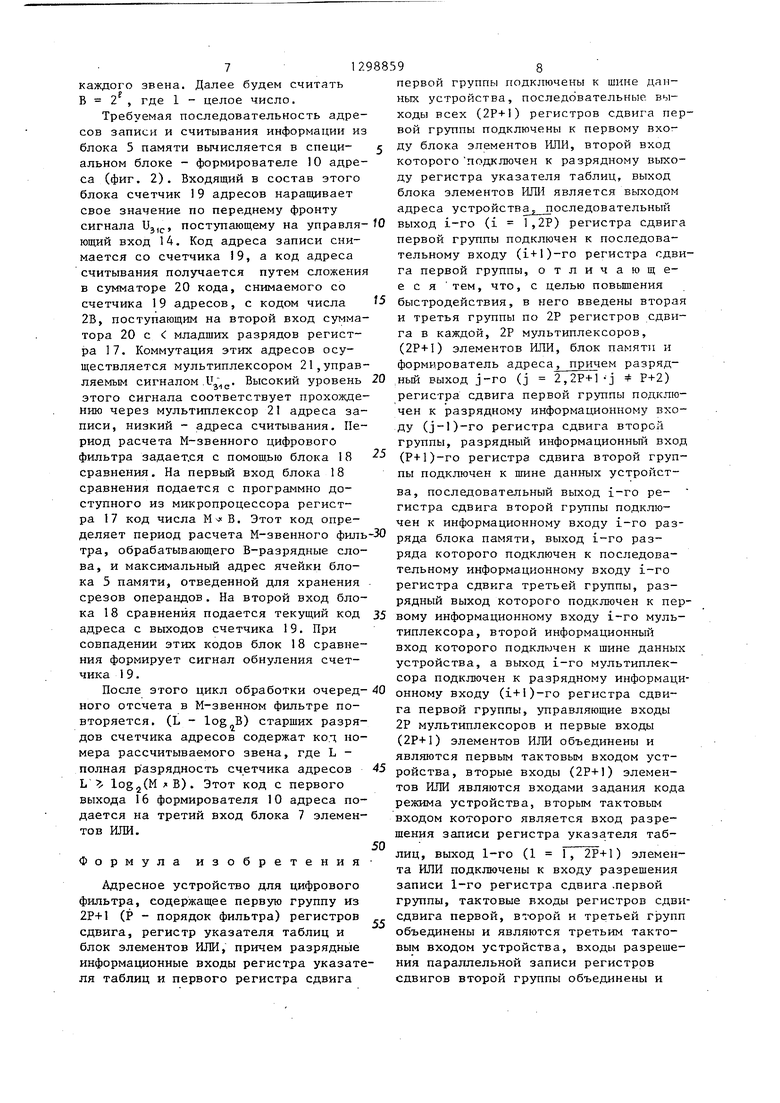

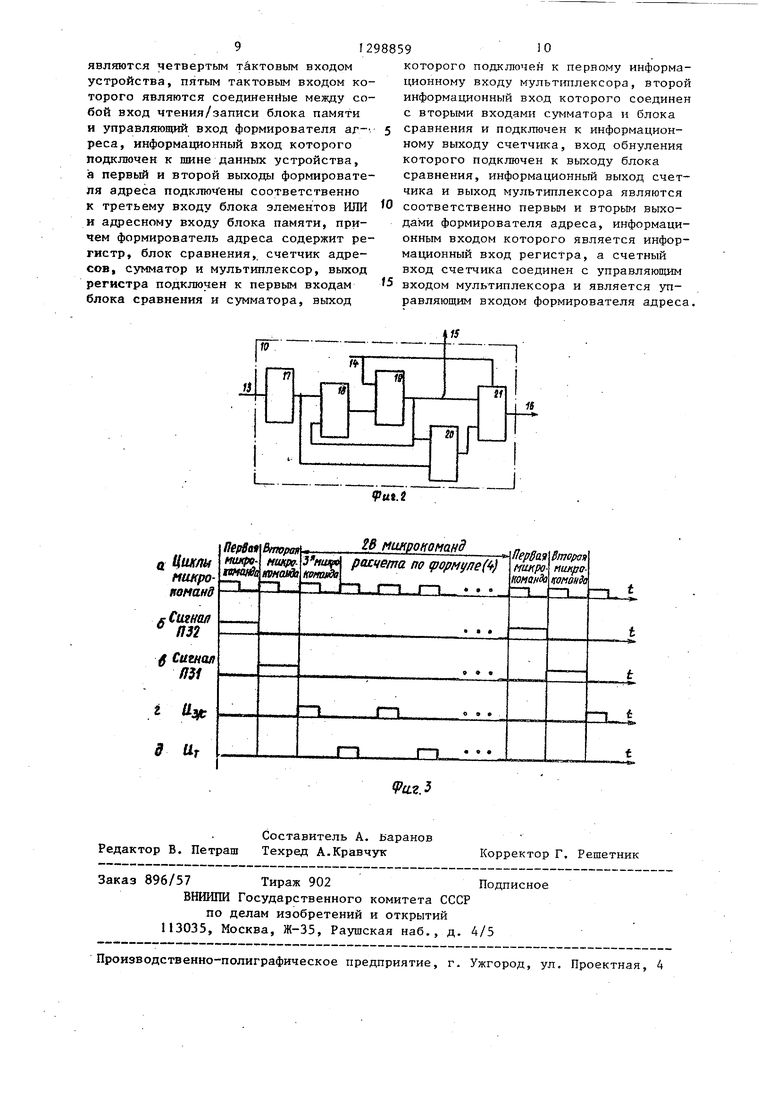

На фиг. 1 изображена функциональная схема адресного устройства для цифрового фильтра; на фиг. 2 - функциональная схема формирователя адреса; на фиг. 3 - временные диаграммы работы адресного устройства.

Адресное устройство содержит первую 1 .1-1 .2P-t-l/вторую 2,1-2.2Р и третью 3.1-3.2Р группы регистров сдвига, 2Р мультиплексоров 4,1-4.2Р, блок 5

памяти, регистр 6 указателя таблиц; блок ИЛИ 7 элементов, тактовые входы 8, 2Р+1 элементов ИЛИ 9.1-9.2Р+1, формирователь 10 адреса, шину 11 дан- Hbix, информационный выход 1 2 адреса устройства.

Формирователь 10 адреса (фиг. 2) содержит информационный вход 13, управляющий вход 14, первый 15 и второй 6 выходы, регистр 17, блок 18

где X(n) и Y(n) - входные и выходные операнды многозвенного фильтра. .

20

25

При параллельном соединении звеньев сложного фильтра аналогичные связи имеют следующий вид:

X (п) Х(п);

гт

Y(n) 11: Y(n), m 1,2,...,М (3).

-t

Из соотношений (1)-(3) следует, что

сравнения, счетчик 19 (адресов), сум- - реализация многозвенных цифровых фи., f . ni ттт-ГЯГЧ/ЛТ о Т ТЛГТЛОПГ Г ТТО г r r ntrt-rV ТГРТЛОЙРТ-

льтров В микропроцессорных устройствах сводится к двум группам действий: вычислению базовых звеньев Р-го порядка (1) и подготовка операндов для очерёдного звена, которая сводится в

матор 20 и мультиплексор 21 ( сов) .

Работу фильтра можно описать разностным уравнением

РР

Y (п) (n-i) +Г .(n-i) , основном к операциям пересылки операн-.

Цп - 1 m -г t «/-о /04

(I) дов С учетом соотношении (2) и (3). При использовании принципа распре(т 1,2,.,.,М) ной операнды т-го . деленной арифметики, расчет базового звена в k-й мо- звена (I) осуществляется в соответст1:0

где X(k) и Y(k) - входной и выход40

мент времени;

8J-i

Y(n) 11:2 PlXJn),XJn-l),...,XJn-P), Y(n-l),..., Y(n-P)J , xjn-l),...,x;(n-P), Y;(n-I),...,Y;(n-P),

где (n), X(n-l) +...-f X(n-P), Y;(n-l),...,Y;i(n-P)

C - «(- ) (n-p) - Ь,(п-1) -...-bX(n-P);

X(n) - разряд числа X(n), принимающий значение О или 1; В - разрядность обрабатываемых цифровых, фильтров операндов .

Требуемые значения функций Я (О (частичные суммы произведений) для каждого ш-го звена рассчитываются

Ь. - коэффициенты фильтра га-го звена;

п - номер обрабатываемой выборки;.

Р - порядок звена

(обычно Р 2,4).

При каскадном построенной многозвенных фильтров входные и выходные переменные звенья связаны соотношением

X;,(n-i) X(n-i), i 0,...,Р;

X(n-i) ), m 2,3,...,

,...,M;

X.(n) Y(n),(3)

где X(n) и Y(n) - входные и выходные операнды многозвенного фильтра. .

При параллельном соединении звеньсложного фильтра аналогичные свяимеют следующий вид:

X (п) Х(п);

гт

Y(n) 11: Y(n), m 1,2,...,М (3).

-t

соотношений (1)-(3) следует, что

реализация многозвенных цифровых фи ттт-ГЯГЧ/ЛТ о Т ТЛГТЛОПГ Г ТТО г r r ntrt-rV ТГРТЛОЙРТ-

льтров В микропроцессорных устройствах сводится к двум группам действий: вычислению базовых звеньев Р-го порядка (1) и подготовка операндов для очерёдного звена, которая сводится в

. деленной арифметик звена (I) осуществ

40

ВИИ с алгоритмом

(4)

(5)

заранее и хранятся в виде таблиц в блоке памяти микропроцессорной системы. Таблица для т-го звена выбирается кодом из регистра указателя таблиц, а слово в таблице - кодом, формиру- ; емым из одноименных разрядов о перан- дов X(i), Y(i), находящихся в регистрах сдвига адресного устройства.

Операции, выполняемые адресным устройством, повторяются циклически при расчете очередного звена в каждом новом отсчете сигнала. Рассмотрим работу адресного устройства во время расчета ш-го звена при обработке п-го входного отсчета.

Исходное состояние.

Перед началом расчета п-го отсчета в т-м звене в регистрах 1.2-l.I-t-l находятся операнды Х(п) , .,. ,Х(п-Р+ +1), в регистрах 1.Р+3-1.2Р+1 - операнды Уг„,,(п-1),. . . ,Y,(n-P+l ) , а выСледующая микрокоманда осуществляет пересылку нового операнда из внутреннего регистра микропроцессора в регистр 1.1 сдвига первой группы адресного устройства. Для первого звена

численный при расчете предыдущего (in-l)-ro звена результат Y(n) нахо- -5 этим операндом является очередной от- дится во внутреннем регистре микро- счет входного сигнала Х(п), а для процессора (не входящего в состав адресного устройства); который подключен к шине 11 данных. В регистрах 3.1ш-го звена (т 2,3,...,М) - это результат предыдущего, звена Y.(n). В процессе выполнения этой микрокоманды 3.2Р третьей группы в этот момент 20 на соответствующем тактовом входе 8 времени находятся- выведенные из бло- вырабатывается сигнал разрешения пака 5 памяти в процессе расчета (т-1) -го звена операнды, необходимые для

расчета следующего га-го звена, В ре-

гистрах 3.1-З.Р сдвига третьей груп- - работы всех регистров сдвига первой пы находятся операнды Х (п-1),..., группы. Этот же сигнал переключает ...,Xj(n-P), а в регистрах З.Р+1 - мультиплексоры 4.1-4.2Р в положение

пропускания на выходы информации от третьей группы регистров сдвига. Таким образом, в результате выполнения этой операции осуществляется пересылка содержимого регистров 3.1-3.2Р

раллельной записи П31 (фиг. Зв), который через элементы ИЛИ 9.1-9.2Р+1 подается на входы управления режимом

3.2Р сдвига третьей группы - вперан- ды Yrp,(n-l ) ,.. . ,Y(n-P) соответственно. Содержимое регистров 2.1-2.2Р 0 сдвига второй группы, а также регистров 1.1 и 1.Р+2 сдвига первой группы

сдвига третьей группы в регистры 1.2- 1.2Р+1 сдвига первой группы I.2-1.2P+

в данный момент времени не имеет значения ,

Далее микропрограммно выполняется 35 + соответственно, операция пересылки операндов между По окончании вьшолнения описывае40

. 45

первой, второй и третьей группами регистров сдвига адресного устройства, завершая тем самым подготовку к расчету следующего га-го звена. Каждая микрокоманда вьтолняется за один машинный цикл, определяемый периодом за дающих тактовых импульсов (фиг. За). Первой микрокомандой в цикле расчета выполняется микрокоманда пере сьшки Y(n) из внутреннего регистра микропроцессора в регистр 2.Р+1 сдвига второй группы. При выполнении этой микрокоманды на соответствующем тактовом входе вырабатывается сигнал раллельной записи П32 (фиг. 36), который подается на все регистры 2.1- 2.2Р сдвига второй группы. Поэтому одновременно с записью Y,(n) в ремой микрокоманды в регистрах сдвига первой группы находятся все операнды необходимые для расчета п-го отсчета на выходе т-го звена, в регистрах сдвига второй группы все операнды, которые необходимо хранить для вычис ления (п+1)-и выборки на выходе (m-l)звена. Содержимое регистров 3.1- 3.2Р сдвига третьей группы переписано в регистры 1.2-1.2Р+1 сдвига первой группы, следовательно, регистры 3.1-3.2Р сдвига третьей группы готовы к приему новой информации.

Первый тактовый вход и входы 8 задания режима подключены входом управления режимом работы регистров 1.1- 1.2Р+1 сдвига первой группы через одноименные двухвходовые элементы

гистр 2.Р+1 сдвига второй группы осу- ИЛИ 9.1-9.2Р+1. Такое исключение по- ществляется пересылка содержимого зволяет, кроме режима одновременной регистров 1.2-1.Р+1, 1.Р+З. - 1.2Р+1 параллельной записи во все регистры сдвига первой группы в 1.1-1.Р, 1.Р- 1.1-1.2Р+1 сдвига первой группы осу5

О

88594

1 . 2Р второй группы соответственно. При этом операнды Х(п), . . . ,Х,.,(п-Р- 1), Y.,(n),...,Y.,(n-p+U будут занесены в регистры 2.1-2.2Р сдвига второй группы соответственно. Эта операция требуется для сохранения операндов, необходимых при расчете следующего (п+1)-го отсчета на выходе (m-l)-ro звена.

Следующая микрокоманда осуществляет пересылку нового операнда из внутреннего регистра микропроцессора в регистр 1.1 сдвига первой группы адресного устройства. Для первого звена

-5 этим операндом является очередной от- счет входного сигнала Х(п), а для ш-го звена (т 2,3,...,М) - это результат предыдущего, звена Y.(n). В процессе выполнения этой микрокоманды на соответствующем тактовом входе 8 вырабатывается сигнал разрешения па

работы всех регистров сдвига первой группы. Этот же сигнал переключает мультиплексоры 4.1-4.2Р в положение

раллельной записи П31 (фиг. Зв), который через элементы ИЛИ 9.1-9.2Р+1 подается на входы управления режимом

сдвига третьей группы в регистры 1.2- 1.2Р+1 сдвига первой группы I.2-1.2P+

мой микрокоманды в регистрах сдвига первой группы находятся все операнды, необходимые для расчета п-го отсчета на выходе т-го звена, в регистрах сдвига второй группы все операнды, которые необходимо хранить для вычис- ления (п+1)-и выборки на выходе (m-l)ro звена. Содержимое регистров 3.1- 3.2Р сдвига третьей группы переписано в регистры 1.2-1.2Р+1 сдвига первой группы, следовательно, регистры 3.1-3.2Р сдвига третьей группы готовы к приему новой информации.

Первый тактовый вход и входы 8 задания режима подключены входом управления режимом работы регистров 1.1- 1.2Р+1 сдвига первой группы через одноименные двухвходовые элементы

ИЛИ 9.1-9.2Р+1. Такое исключение по- зволяет, кроме режима одновременной параллельной записи во все регистры 1.1-1.2Р+1 сдвига первой группы осуществлять микропрограммно загрузку из микропроцессора любого из этих регистров так же, как и регистра указателя таблиц.

Далее выполняется микропрограмма расчета т-го звена цифрового фильтра по формуле (4). При этом с помощью первой группы регистров 1.1-).2Р+1 сдвига формируются адреса операндов (5). Одновременно осуществляются запись на хранение в блок 5 памяти операндов из регистров 2.1-2.2Р сдвига второй группы и считывание из блока 5 памяти в регистры 3.1-3.2Р сдвига третьей группы операндов, необходимых для расчета следующего (т+1)-го, если m М, или первого, если m М звена.

Очередная микрокоманда вьтолняег операцию сложения, в соответствии с выражением (4), содержимого аккумулятора микропроцессора со значением функции р(-) извлекаемой из главной памяти микропроцессорной системы по адресу, формируемому блоком 7 элементов ИЛИ, из трех компонент,. Окончательно этот адрес формируется в блоке 7 элементов ИЛИ логики. Старшие разряды адреса, определяющие область памяти (таблицу), в которой хранятся значения функции f(-) для рассчитываемого звена, определяются кодом, находящимся в регистре 6 указателя таблиц, и кодом, который поступает в блок 7 элементов ИЛИ с первого (L - 1оу В) разрядного выхода формирователя 10 адреса. 2Р+1 младших разрядов адреса определяют конкретные ячейки в выбранной области памяти. Они составлены из значений разрядов операнг ДОВ-, которые находятся в это время в младший разрядах регистров сдвига первой группы.

В дальнейшем то множество разрядов

ла ° разрешено считывание информации из блока 8 памяти в старшие разряды третьей группы регистров 3.1- 3.2Р сдвига.

5 Четвертая микрокоманда по временной диаграмме выполняет в соответствии с выражением (4) операцию сдвига вправо суммы, накопленной в аккумуляторе микропроцессора после выполнения 9 предыдущей микрокоманды сложения. Одновременно на соответствующем тактовом входе В формируется сигнал UT (фиг. Зд), который подается на тактовые входы всех регистров 1 .1-1 . ,

f5 2.1-2.2Р и 3.1-3.2Р сдвига первой и второй и третьей групп соответственно и осуществляется сдвиг содержимого этих регистров на один разряд вправо. Одновременно со сдвигом содержимого

20 регистров 3.1-3.2Р сдвига третьей группы в их старшие разряды передним фронтом импульсов и поразрядно записываются считываемые из блока 5 памяти операнды, необходимые для расчета следующего звена.

Две последние микрокоманды повторяются В раз. В результате вычисляется выходная выборка т-го звена Y (п), операнды (m-l)-ro звена Х (п),..., ..., Х„Д(п-Р+1), ,(n) ,... , Y., (п-Рн-1) из второй грзтпы-регистров 2.1-2.2Р сдвига записываются в блок 5 памяти по соответствующим адресам, вырабатываемым формирователем 10 адреса, но35 вые операнды для (т+1)-г6 звена пораз- рядно считываются из соответствующих ячеек блока 5 памяти в регистры 3.1- 3.2Р третьей группы. После этого описанный цикл пересылки операндов и расчета очередного звена может повторяться.

25

30

40

Таким образом, в цикле вычисления

„ - ,-,... т-го звена при обработке п-го отсчета

{Z-, i 1,2,...,N}, которые находят- осуществляется запись В срезов 2Р

ся в данный момент на последователь- операндов (m-l)-ro звена в отведенную

ных выходах из регистров сдвига первой, второй или третьей группы, условно называется срезом операндов.

Б процессе выполнения этой микрокоманды высокий, уровень сигнала (фиг. Зг) разрешает запись в блок 5 памяти среза операндов, который поступает из регистров 2,1-2.2Р сдвига

50

для этого звена область блока памяти из В ячеек, а В срезов 2Р операндов (т+1)го звена считьшаются из своей области памяти. Области памяти, отведенные для соответствующих звеньев расположены в блоке 5 памяти в порядке возрастания номеров звеньев. Поэтому адрес считьшания всегда должен

второй группы на информационные входыбыть больше адреса записи на 2В, где

блока 5 памяти. Когда на управляющийВ - разрядность обрабатываемых слов

вход (записи/считьшания) блока 8 па-и, мяти поступает нулевой уровень сигнаследовательно, число слов (срезов которое хранится в блоке 5 памяти для

ла ° разрешено считывание информации из блока 8 памяти в старшие разряды третьей группы регистров 3.1- 3.2Р сдвига.

Четвертая микрокоманда по временной диаграмме выполняет в соответствии с выражением (4) операцию сдвига вправо суммы, накопленной в аккумуляторе микропроцессора после выполнения 9 предыдущей микрокоманды сложения. Одновременно на соответствующем тактовом входе В формируется сигнал UT (фиг. Зд), который подается на тактовые входы всех регистров 1 .1-1 . ,

5 2.1-2.2Р и 3.1-3.2Р сдвига первой и второй и третьей групп соответственно и осуществляется сдвиг содержимого этих регистров на один разряд вправо. Одновременно со сдвигом содержимого

0 регистров 3.1-3.2Р сдвига третьей группы в их старшие разряды передним фронтом импульсов и поразрядно записываются считываемые из блока 5 памяти операнды, необходимые для расчета следующего звена.

Две последние микрокоманды повторяются В раз. В результате вычисляется выходная выборка т-го звена Y (п), операнды (m-l)-ro звена Х (п),..., ..., Х„Д(п-Р+1), ,(n) ,... , Y., (п-Рн-1) из второй грзтпы-регистров 2.1-2.2Р сдвига записываются в блок 5 памяти по соответствующим адресам, вырабатываемым формирователем 10 адреса, но5 вые операнды для (т+1)-г6 звена пораз- рядно считываются из соответствующих ячеек блока 5 памяти в регистры 3.1- 3.2Р третьей группы. После этого описанный цикл пересылки операндов и расчета очередного звена может повторяться.

5

0

0

для этого звена область блока памяти из В ячеек, а В срезов 2Р операндов (т+1)го звена считьшаются из своей области памяти. Области памяти, отведенные для соответствующих звеньев расположены в блоке 5 памяти в порядке возрастания номеров звеньев. Поэтому адрес считьшания всегда должен

В - разрядность обрабатываемых слов

и,

следовательно, число слов (срезов), которое хранится в блоке 5 памяти для

каждого звена. Далее будем считать В 2, где 1 - целое число.

Требуемая последовательность адресов записи и считывания информации из блока 5 памяти вьнисляется в специ- альном блоке - формирователе 10 адреса (фиг. 2). Входящий в состав этого блока счетчик 19 адресов наращивает свое значение по переднему фронту сигнала Uj,, поступающему на управляющий вход 14. Код адреса записи снимается со счетчика 19, а код адреса считывания получается путем сложения в сумматоре 20 кода, снимаемого со счетчика 19 адресов, с кодом числа 2В, поступающим на второй вход сумматора 20 с младших разрядов регистра 17. Коммутация этих адресов осуществляется мультиплексором 21,управ ляемьм сигналом . Высокий уровень этого сигнала соответствует прохождению через мультиплексор 21 адреса записи, низкий - адреса считывания. Период расчета М-звенного цифрового фильтра задает.ся с помощью блока 18 сравнения. На первый вход блока 18 сравнения подается с программно доступного из микропроцессора регистра 17 код числа В. Этот код опре

первой группы подключены к шнне дан ных устройства, последовательные вы ходы всех (2Р+1) регистров сдвига п вой группы подключены к первому вхо ду блока элементов ИЛИ, второй вход которого подключен к разрядному вых ду регистра указателя таблиц, выход блока элементов ИЛИ является выходо адреса устройства, последовательный выход i-ro (i 1,2Р) регистра сдви первой группы подключен к последова тельному входу (i+l)-ro регистра сд га первой группы, отличающе еся тем, что, с целью повышения быстродействия, в него введены втор и третья группы по 2Р регистров сдв га в каждой, 2 мультиплексоров, (2P+I) элементов ИЛИ, блок памяти и формирователь адреса, причем разряд ньш выход j-ro (j 2,2P+l--j Р+2) регистра сдвига первой группы подкл чен к разрядному информационному вх ДУ (j-l)-ro регистра сдвига второй группы, разрядный информационньш вх (Р+1)-го регистра сдвига второй гру пы подключен к шине данных устройст ва, последовательный выход i-ro регистра сдвига второй группы подключен к информационному входу i-ro ра

деляет период расчета М-звенного филь-30 блока памяти, выход i-ro раз- тра, обрабатывающего В-разрядные слова, и максимальный адрес ячейки блоряда которого подключен к последова тельному информационному входу i-ro регистра сдвига третьей группы, раз рядный выход которого подключен к п

ряда которого подключен к последовательному информационному входу i-ro регистра сдвига третьей группы, разрядный выход которого подключен к перка 5 памяти, отведенной для хранения срезов операндов. На второй вход блока 18 сравнения подается текущий код 35 вому информационному входу i-ro мультиплексора, второй информационный вход которого подключен к шине данных устройства, а выход i-ro мультиплексора подключен к разрядному информациадреса с выходов счетчика 19. При совпадении этих кодов блок 18 сравнения формирует сигнал обнуления счетчика 19.

После этого цикл обработки очеред-40 энному входу (i+l)-ro регистра сдвиного отсчета в М-звенном фильтре повторяется. (L - log В) старших разрядов счетчика адресов содержат код номера рассчитываемого звена, где L - полная р азрядность счетчика адресов 45 L 1о§2(М; В). Этот код с первого выхода 16 формирователя 10 адреса подается на третий вход блока 7 элементов ИЛИ.

50 Формула изобретенияАдресное устройство для цифрового фильтра, содержащее первую группу из 2Р+1 (Р - порядок фильтра) регистров сдвига, регистр указателя таблиц и блок элементов ИЛИ, причем разрядные информационные входы регистра указателя таблиц и первого регистра сдвига

га первой группы, управляющие входы 2Р мультиплексоров и первые входы (2Р+1) элементов ИЛИ объединены и являются первым тактовым входом устройства, вторые входы {2Р+1) элементов ИЖ являются входами задания кода режима устройства, вторым тактовым входом которого является вход разрешения записи регистра указателя таблиц, выход 1-го (, 2Р+1) элемента ИЛИ подключены к входу разрешения записи 1-го регистра сдвига .первой группы, тактовые входы регистров сдви- сдвига первой, второй и третьей групп объединены и являются третьим тактовым входом устройства, входы разрешения параллельной записи регистров сдвигов второй группы объединены и

5 fO 5 20 88598

первой группы подключены к шнне данных устройства, последовательные выходы всех (2Р+1) регистров сдвига первой группы подключены к первому входу блока элементов ИЛИ, второй вход которого подключен к разрядному выходу регистра указателя таблиц, выход блока элементов ИЛИ является выходом адреса устройства, последовательный выход i-ro (i 1,2Р) регистра сдвига первой группы подключен к последовательному входу (i+l)-ro регистра сдвига первой группы, отличающееся тем, что, с целью повышения быстродействия, в него введены вторая и третья группы по 2Р регистров сдвига в каждой, 2 мультиплексоров, (2P+I) элементов ИЛИ, блок памяти и формирователь адреса, причем разряд- ньш выход j-ro (j 2,2P+l--j Р+2) регистра сдвига первой группы подключен к разрядному информационному вхо- ДУ (j-l)-ro регистра сдвига второй группы, разрядный информационньш вход (Р+1)-го регистра сдвига второй группы подключен к шине данных устройства, последовательный выход i-ro ре гистра сдвига второй группы подключен к информационному входу i-ro раз25

-30 блока памяти, выход i-ro раз- блока памяти, выход i-ro раз-

ряда которого подключен к последовательному информационному входу i-ro регистра сдвига третьей группы, разрядный выход которого подключен к первому информационному входу i-ro мультиплексора, второй информационный вход которого подключен к шине данных устройства, а выход i-ro мультиплексора подключен к разрядному информацига первой группы, управляющие входы 2Р мультиплексоров и первые входы (2Р+1) элементов ИЛИ объединены и являются первым тактовым входом устройства, вторые входы {2Р+1) элементов ИЖ являются входами задания кода режима устройства, вторым тактовым входом которого является вход разрешения записи регистра указателя таблиц, выход 1-го (, 2Р+1) элемента ИЛИ подключены к входу разрешения записи 1-го регистра сдвига .первой группы, тактовые входы регистров сдви- сдвига первой, второй и третьей групп объединены и являются третьим тактовым входом устройства, входы разрешения параллельной записи регистров сдвигов второй группы объединены и

являются четвертым тактовым входом устройства, пятым тактовым входом которого являются соединенные между собой вход чтения/записи блока памяти и управляющий вход формирователя аг- реса, информационный вход которого подключен к шине данных устройства, а первый и второй выходы формирователя адреса подключ ены соответственно к третьему входу блока элементов ИЛИ и адресному входу блока памяти, причем формирователь адреса содержит регистр, блок сравнения,, счетчик адресов, сумматор и мультиплексор, выход регистра подключен к первым входам блока сравнения и сумматора, вьгеод

1 рт ;,,

L..

а Цш(/ш микро- яопанд

хСигная ° П32

X Сигнал ffSI

2 % д UT

Редактор В. Петраш

Составитель А. Баранов Техред А.Кравчук

Заказ 896/57 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

которого подключен к первому информационному входу мультшшексора, второй информационный вход которого соединен с вторыми входами cy мaтopa и блока сравнения и подключен к информационному выходу сч&тчггка, вход обнуления которого подключен к выходу блока сравнения, информационный выход счетчика и выход мультиплексора являются соответственно первым и вторым выходами формирователя адреса, информационным входом которого является информационный вход регистра, а счетный вход счетчика соединен с управляющим входом мультиплексора и является управляющим входом формирователя адреса,

16

ti

IS

го

Vut.i

Корректор Г. Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Микропрограммное управляющее устройство | 1987 |

|

SU1527634A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Устройство для адресации процессора быстрого преобразования Фурье | 1985 |

|

SU1298765A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Секционный микропроцессор | 1982 |

|

SU1062711A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для цифровой обработки сигналов, в частности для цифровой фильтрации в различных цифровых комплексах. Цель изобретения - повьшение быстродействия. Поставленная цель достигается за счет того, что устройство содержит первую .группу из (2Р+1) регистров сдвига 1.1-1.2Р+, вторую 2.1-2.2Р и третью 3.1-3.2Р, группы из 2 регистров сдвига, мультиплексоры 4.1- 4.2Р, (Р - порядок фильтра), блок 5 памяти, регистр 6 указателя таблиц, блок элементов ИЛИ 7, тактовые входы 8, элементы ИЛИ 9.1-9.2Р+1, формирователь 10 адреса, шину 11 данных и выход 12 адреса. 3 ил. ю

| Цифровой фильтр | 1982 |

|

SU1107291A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Zeman I | |||

| and Nagle Т | |||

| А hi h-Speed Mickopkogrammable Digital Signal Processor Employind Distributes Arithmetic | |||

| - IEEE Journal of Solid-State circuit, 1980, vol | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-18—Подача