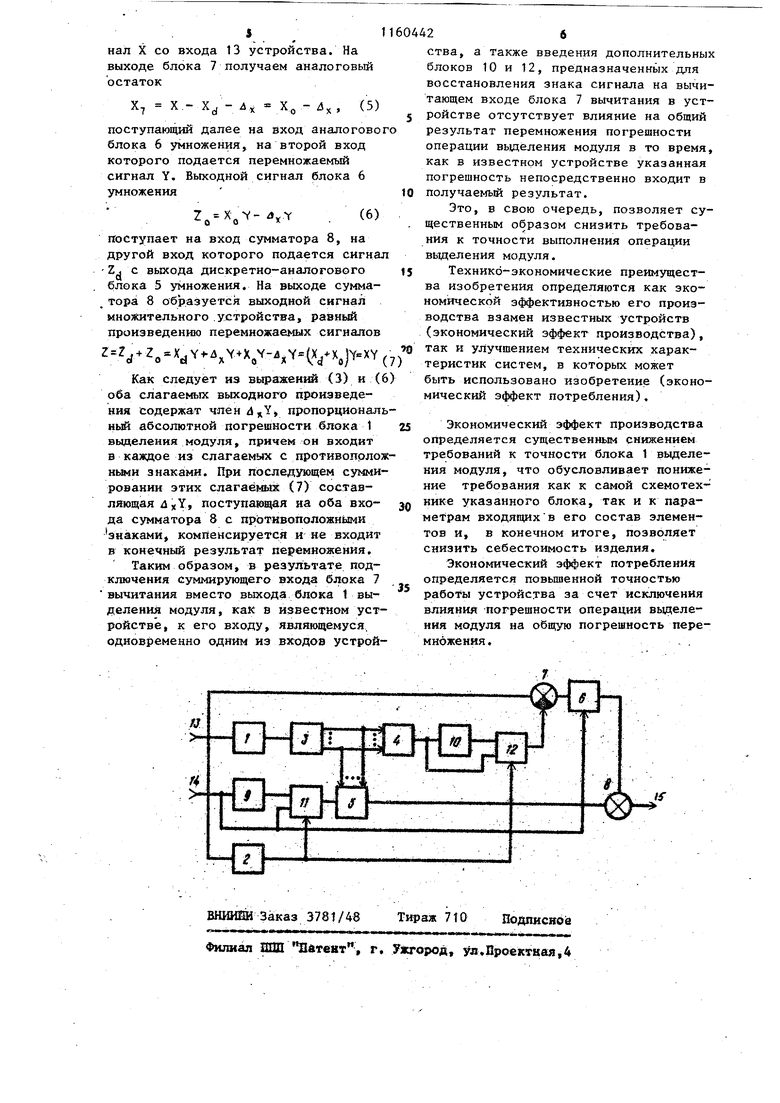

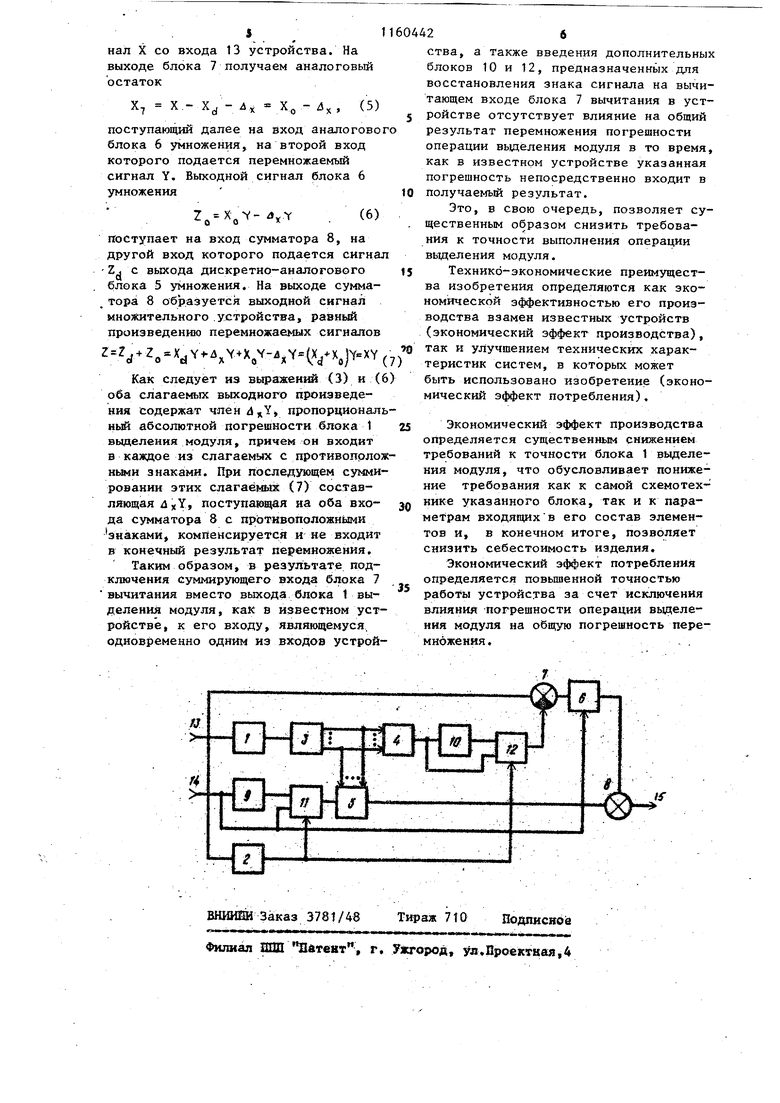

I. 1 Изобретение относится к аналогово вычислительной технике и может быть использованр в системах и устройства автоматики. ч Известно множительное устройство с аналого-цифроаналоговым преобразователем, содержащее аналого-цифровой (АЦП) и цифроаналоговьй (ЦАП) преобразователи, дискретно-аналоговьп и аналоговый перемножители, схему, вычи тания и сумматор fl j, Однако это устройство (если АЦП и ШШ - однополярные, а дискретно-аналоговый умно)|сения соответственн двухквадратньй) способно осуществлят операцию перемножения лишь в двух квадрантах. Расширение области работ устройства до четырех квадрантов путем применения биполярных АЦП и ЦАП чегырехкваедрантного дискретно-аналогового перемножителя существенно увеличивает объем устройства. Наиболее близким по технической сущности к изобретению является множительное устройство, в котором используется множительное устройство tlJ в качестве двухквадрантнрго. Такое устройство содержит блок выделения модуля, знаковьй компаратор, аналого-цифровой и цифроаналоговый преобразователи, дискретно-аналоговый и аналоговый блоки умножения, блок вычитания,сумматор, инвертор и коммутатор, причем входы блока вьщеления модуля и знакового компаратора соединены с первым входом устройства выход знакового компаратора соединен с управляющим входом коммутатора, первый и второй входы которого соеди нены соответственно с входом и выход инвертора, выход блока выделения модуля соединен с входом аналого-цифро вого преобразователя, выход которого соединен с входом цифроаналогового преобразователя и дискретным входом дискретно-аналогового перемножителя, выход последнего подключен к одному из входов сумматора, второй вход сумматора соединен с выходом аналого вого блока умно;|сения, первый вход ,которого соединен с выходом блока вычитания ,, Однако в известном устройстве точность блока выделения модуля в цепи одного из перемножаемых сигналов влияет на точность /работы устрой ства в целом. Цель изобретения - повышение точности устройства.. A2 Поставленная цель достигается тем, что множительное устройство, содержащее блок выделения модуля и знаковый компаратор, входы которых объединены и являются первым информаЦИОННЫМ входом устройства, аналогоцифровой и цифроаналоговый преобразователи, дискретно-аналоговый и аналоговый блоки умножения, блок вычитания, первый инвертор, первый коммутатор и сумматор, два входа которого подключены к выходаж соответственно дискретно-аналогового и аналогового блоков умножения, а выход является выходом устройства выход знакового компаратора соединен с управляющим входом первого коммутат,ора, два информацион|ных входа которого подключены соответственно к входу и выходу первого инвертора, дискретньй вход дискретноаналогового блока умножения подсоединен к выходу, аналого-цифрового и входу цифроаналогового преобразователей, вход аналого-цифрового преобразователя подключен к выходу блока выделения модуля, один из входов аналогового блока умножения подсоединен к выходу блока вычитания, дополдительно содержит второй инвертор и второй коммутатор, управляющий вход которого соединен с выходом знакового компаратора, а два информационных входа и вь1ход подключены соответствеи:.о к входу и выходу второго инвертора и к вычитающему входу блока вычитания, подсоединенного суммирующим входом к лервому информационному входу устройства, вход второго инвертора подключен к выходу цифроаналогового преобразователя, второй вход аналогового блока умножения соединен с входом первого инвертора и вторым информационным входом устройства, выход первого коммутатора подключен к аналоговому входу дискретно-аналогового блока умножения. На чертеже представлена структурная схема множительного устройства. Устройство содержит блок 1 выделения модуля, знаковый компаратор 2, аналого-цифровой преобразователь (АЦП) 3, цифроаналоговый преобразова;гель (ЦАП) 4, дискретно-аналоговый и аналоговьш, блоки умножения соответственно 5 и 6, блок 7 вычитания, сумматор 8, первый 9 и второй 10 инверторы, первый 11 и второй 12 коммутаторы, первый 13 и второй 14 информационные входь и выход 15 уст31

ройства. Входы блока 1 вьщеления модуля, знакового компаратора 2 и суммирующий вход блока 7 вычитания объединены и образуют вход 13 устройства, выход блока 1 выделения модуля соединен со входом АЦП 3, а выход последнего - со входом ЦАП 4 и дискретным входом дискретно-аналогового блока 5 умножения. Выход ЦАП 4 подключен через инвертор tO к одному из входов и непосредственно - к второму входу коммутатора 12, управляющий вход которого соединен с аналогичным входом коммутатора 11 и выходом знакового компаратора 2, а выход - с вычитающш4 входом блока 7 вычитания, выход .последнего подключен к одному из входов аналогового блока 6 умно женил, выход которого подключен к одному из входов сумматора 8, второй вход которого соединен с выходом дискретно-аналогового блока 5 умножения. Входы инвертора 9, коммутатоpa11 и второй вход аналогового блока 6 умножения объединень и образуют вход 14 устройства, выход- коммутатора t 1 соединен с аналоговым входом дискретно-аналогового блока умножения, выход сумматора 8 является выходом 15 устройства.

Устройство работает следукнцим образрм.

I Перемножаемый сигнал у со входа 13 устройства поступает на вход блока 1 выделения модуля. Сигнал на выходе последнего

X, U1

(t)

X

где4х абсолютная погрешность на

выходе блока выделения модуля.

Одновременно сигнал X поступает на вход знакового компаратора 2, на выхода которого при X О образуется сигнал логической единицы, а ПРИ X . О - сигнал логи 1еского нуля.

Сигнал X, с выхода блока 1 поступает далее на вход АЦП 3, на выходе которого образуется код

1-4 i jdxid ).

где квантованное по уровню значение величины 1X1, Kj - коэффициент преобразования АЦП 3.

604424 .

Код N поступает на дискретный вход дискретно-аналогового блока 5 умножения, на аналоговый вход которого подается сигнал с выхода перJ вого коммутатора 11, который, в свою очередь, образуется из второго перемножаемого сигнала Y путем изменения его полярности в соответствии с полярностью сигнала X. Сигнал Y 10 поступает на один из входов коммутатора 11 непосредственно, а на другой его вход - через инвертор 9. Коммутатор 11 подключает к аналоговому входу дискретно-аналогового блока 5

15 умножения сигнал Y со входа 14 устройства при наличии сигнала логической единицы на его управляющем входе, и инвертированное значение сигнала Y, получаемое на выходе инвертора 9, 2Q если на управляющем входе блока 11 имеется сигнал логического нуля. Таким образом, коммутатор 11 и инвертор 9 совместно со знаковым компаратором 2 осуществляют перемноже-.

5 ние сигнала Y на знак сигнала X. Дискретно-аналоговый блок 5 умножения перемножает сигнал Y на квантованное значение модуля сигнала X

Z,,-K5Nj K,Ks(,Yb 0 При выполнении условия 1 получим,

. , (3)

где Y - произведение сигнала Y на 5 знак сигнала X, Kj - масштабный коэффициент дискретно-аналогового блока 5 умножения.

Код NX поступает также на вход ЦАП 4, дри помощи которого преобразуется в аналоговую форму : , K,K(|X|jVAj

При Kjk 1 получим

х ,

(4)

X.

где К4 - масштабный коэффициент ЦАП 4.

Сигнал Хц. поступает непосредственно на один из входов коммутатора 12, и через инвертор 10 - на другой

его вход. Коммутатор 12 подключает к вычитающему входу блока 7 вычитания сигналы таким образом, что знаки сигналов X и |Х| ,-еЛ. всегда совпадают. Следовательно, на вычитающем входе блока 7 имеется сигнал восстановленной полярностью. На с мирующий вход блока 7 вычитания поступает сиг

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1163335A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| УСТРОЙСТВО СЛЕДЯЩЕГО ТИПА ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ВТОРОЙ ОРТОГОНАЛЬНОЙ СОСТАВЛЯЮЩЕЙ ВЕКТОРА | 2000 |

|

RU2187839C2 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок выделения модуля и знаковьй компаратор, входы которых объединены и явл яются первым информационным входом устройства, аналогоцифровой и цифроаналоговый преобра.зователи, дискретно-аналоговый и аналоговый блоки умножения, блок .вычитания, первый инвертор, первьй коммутатор и сумматор, два входа которого подключены к выходам соответственно дискрегтно-аналртового, и аналогового блоков умножения, а выход является выходом устройства, выход знакового компаратора соединен с управляющим входом первого коммутатора, два информационных входа которого подключены соответственно к входу и выходу первого инвертора, дискретный вход дискретно-аналогового блока умножения подсоединен к выходу аналого-цифрового и входу цифроаналогового преобразователей, вход аналого-цифрового преобразователя подключен к выходу блока выделения модуля, один из входов аналогового, блока умножения подсоединен к выходу блока вычитания, отличающееся тем, что, с целью повьпиения точности, .оно содержит второй инвертор и второй коммутатор, управляющий вход которого соединен с выходом знакового компаратора, а два инфор(Л мационных входа и выход подключены с соответственно к входу и выходу второго инвертора и к вычитающему входу блока вычитание, подсоединенного суммирукщим входом к первому информационному входу устройства, вход второго инвертора подключен к выходу цифроаналогового Преобразователя, о: второй вход аналогового блока умноо жения соединен с входом первого ин4: 4 вертора и вторым информационным входом устройства, выход первого коммуto татора подключен к аналоговому входу дискретно аналогового блока умноже- ния..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Корн Г | |||

| Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины | |||

| М,, Мир, 1968, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 395 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1985-06-07—Публикация

1984-01-04—Подача