1

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики, в частности в устройствах измерения энергии импуль ных сигналов.

Цель изобретения - расширение частотного диапазона перемножаемых сигналов.

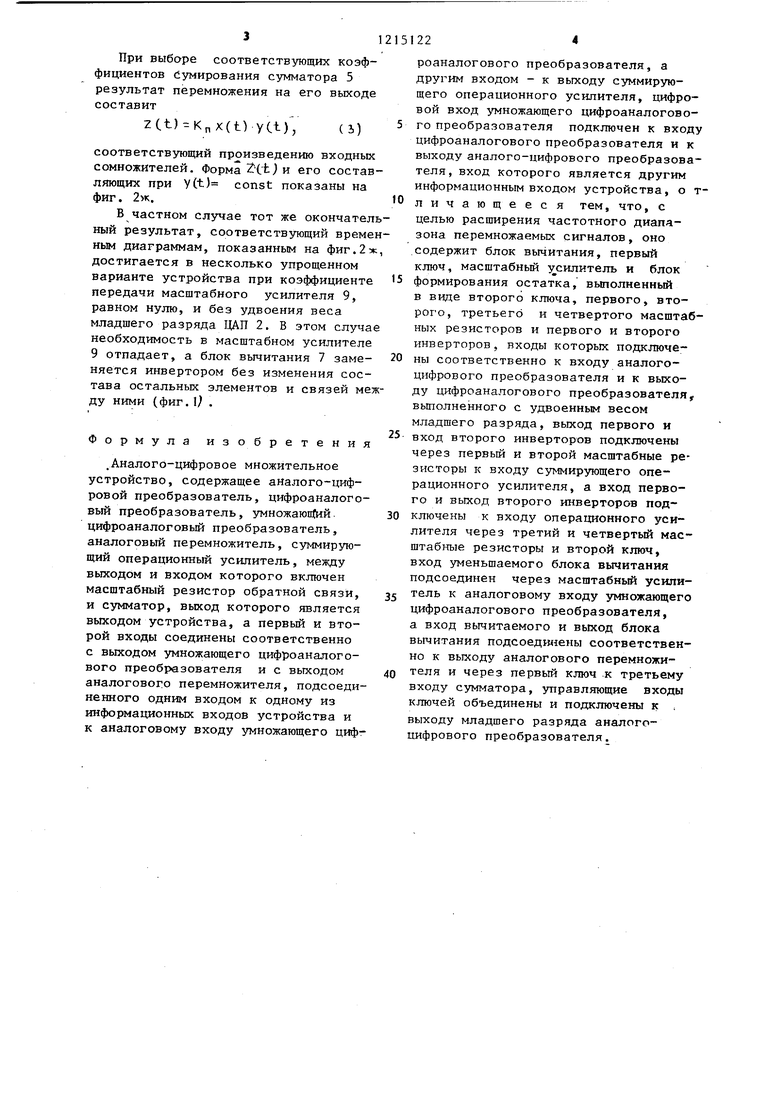

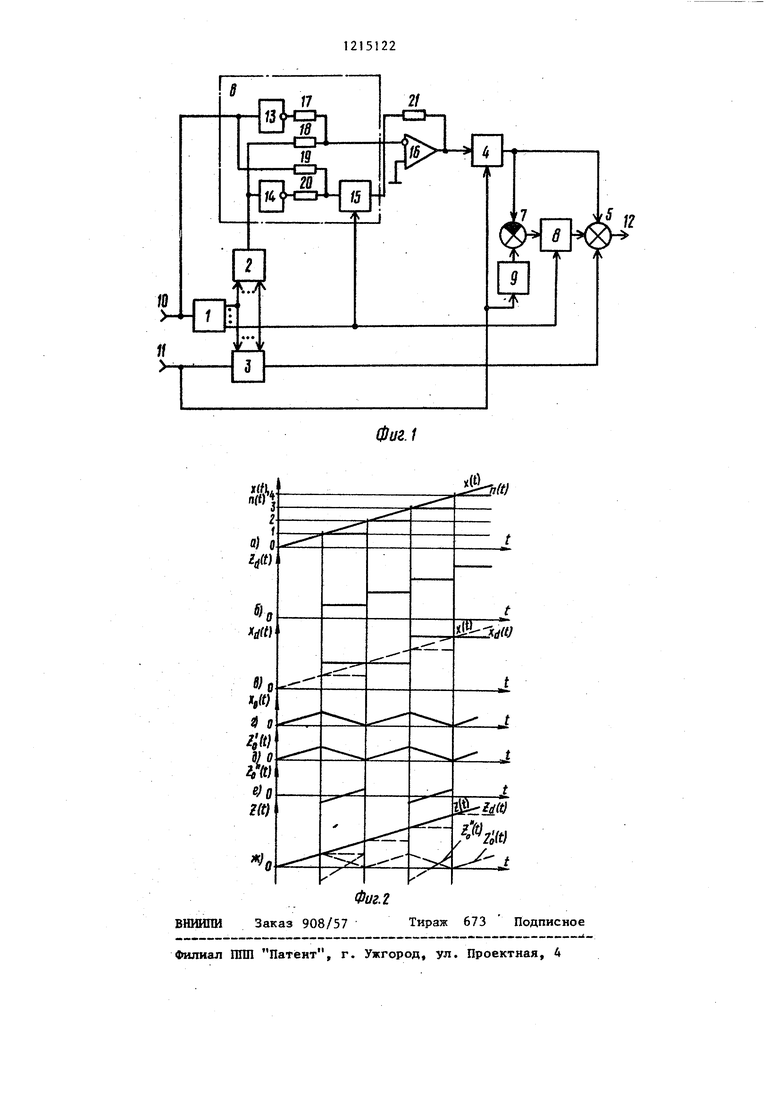

На фиг. 1 приведена структурная схема аналого-цифрового множительного устройства; на фиг. 2 - диаграммы поясняющие его работу.

Множительное устройство содержит аналого-цифровой (АЦП) и цифроанало- говый (ЦАП) преобразователи 1 и .2, умножающий цифроаналоговый преобразователь (ЦАП) 3, аналоговый перемножитель (АЛ) 4, сумматор 5, блок 6 формирования остатка, блок 7 вычитания, ключ 8, масштабный усилитель 9, первый 10 и второй 11 входы и выход 12 устройства. Вход АЦП 1 является входом 10 устройства, выходы АЦП 1 подключены к цифровым входам 2 и 3, аналоговый вход прследнего, являющийся одновременно входом 11 устройства, соединен с одним из входов АО А, а выход подключен к первому входу сумматора 5, второй вход которого соединен с выходом АП 4, выход сумматора 5 является выходом 12 устройства. Входы блока 6 формирования остатка подключены соответственно к входу 10 устройства и к выходу ЦАП 2.

Блок 6 формирования остатка содержит первый и в торой инверторы 13 и 14, дополнительный ключ 15, подключенный к входу суммирующего операционного усилителя (ОУ) 16 уст- ройства, первый 17, йторой 18, тре- тий 19 и четвертый 20 масштабные резисторы. Резистор 21 выполняет функции резистора обратной связи ОУ 16.

Аналого-цифровое множительное устройство работает следующим образом.

Первый сомножитель X(t) (фиг.2а) с входа 10 устройства поступает на вход АЦП 1 с малой разрядностью, осуществляющего квантование X (t-) по уровню с представлением результат. в двоичном коде н(1),

h(t)(t)-ux(t), (1)

20

25

5122

где К , - масштабный коэффициент

преобразования АЦП 1; АХ() - абсолютная погрешность

квантования.

5 Поступая далее на цифровой вход ЦАП 3, кoди(t умножается на второй сомножитель у (t) , который, в свою очередь, поступает на аналоговый вход ЦАП.3с входа 11 устройства. О Выходной сигнал ПАП 3

Z4Ct)-K,KjUCt)u(t)yUK (2)

где K.J - масштабный коэфАициент НАД 3. Форма сигнала Z.cl(tj для (1) 15 const представлена на фиг. 2S.

Одновременно кодовый cHrHant-(t) поступает на цифровой вход ЦАП 2, выполненного с удвоенным весом младшего разряда. Соотношение весов разрядов такого ЦАП: 2-2-4-8-.... В результате дискретная часть Xc|(t). приобретает форму, показанную на фиг. 2В.

С вькода ЦАП 2 сигналXjCt) поступает на инвертор 14 блока 6 формирования остатка на инвертор 13 которого подается сомножитель X(t) с входа 10 устройства, а на управляющий вход ключа 15 - код Ид младшего разряда АЦП 1. Инверторы 13 и 14 и масштабные резисторы 17-20 осуществляют вь1читание сигналов x(t) иХс|С1) с соответствующими масштабными коэффициентами и знаками.

35 Форма сигнала остатка Xo(t) на выходе ОУ 16 представлена на фиг. 2.

Сигнал остатка Xolt.) далее поступает На первый вход АП 4, в котором производится его умножение на второй 40 сомножитель vCt) с соответствующим масштабным коэффициентом.

Форма сигнала Zo(t) на выходе АП 4 при VCt) const показана на фиг.2а. С выхода АП 4ZoC t) поступает на 45 один из входов сумматора 5.

Одновременно ) подается на вход вычитания блока 7 вычитания, на вход уменьшаемого которого поступает сигнал с выхода масштабного 50 усилителя 9.

Поскольку на управляющем входе ключа 8 действует код HO младшего разряда АЦП 1, сигнал с выхода блока вычитания проходит через ключ 8 толь- 55 ко при Ио 1. Поэтому на выходе

последнего имеем форму сигнала Z., () при y(t) const, показанную на фиг. 2е.

30

При выборе соответствующих коэффициентов Сумирования сумматора 5 результат перемножения на его выходе составит

Z(t)-KnX(t) yet), (1)

соответствующий произведению входных сомножителей. Форма Z C t и его составляющих при y(t) const показаны на фиг. .

В частном слз чае тот же окончательный результат, соответствующий временным диаграммам, показанным на фиг.2ж, достигается в несколько упрощенном варианте устройства при коэффициенте передачи масштабного усилителя 9, равном нулю, и без удвоения веса младшего разряда 1ДАП 2. В этом случае необходимость в масщтабном усилителе 9 отпадает, а блок вычитания 7 заме- няется инвертором без изменения состава остальных элементов и связей между ними (фиг. I) ,

Формула изобретения

.Аналого-цифровое множительное устройство, содержащее аналого-цифровой преобразователь, цифроаналого- вый преобразователь, умножаюп йй. цифроаналоговый преобразователь, аналоговый перемножитель, суммирующий операционный усилитель, между выходом и входом которого включен масштабный резистор обратной связи, и сумматор, выход которого является выходом устройства, а первьш и второй входы соединены соответственно с выходом умножающего цифроаналого- вого преобразователя и с выходом аналогового перемножителя, подсоединенного одним входом к одному из информационных входов устройства и к аналоговому входу умножающего циф5

0

5 20

5

0

5

0

роаналогового преобразователя, а другим входом - к выходу суммирующего операционного усилителя, цифровой вход умножающего цифроаналогово- го преобразователя подключен к входу цифроаналогового преобразователя и к выходу аналого-цифрового преобразователя, вход которого является другим информационным входом устройства, о т- личающееся тем, что, с целью расширения частотного диапазона перемножаемых сигналов, оно содержит блок вычитания, первый ключ, масштабный усилитель и блок формирования остатка, выполненный в виде второго ключа, первого, второго, третьего и четвертого масштабных резисторов и первого и второго инверторов, входы которых подключены соответственно к входу аналого- цифрового преобразователя и к выходу цифроаналогового преобразователя выполненного с удвоенным весом младшего разряда, выход первого и вход второго инверторов подключены через первый и второй масштабные резисторы к входу сзгммирующего операционного усилителя, а вход первого и выход второго инверторов подключены к входу операционного усилителя через третий и четвертый масштабные резисторы и второй ключ, вход уменьшаемого блока вычитания подсоединен через масштабный усилитель к аналоговому входу умножающего цифроаналогового преобразователя, а вход вычитаемого и выход блока вычитания подсоедш ены соответственно к выходу аналогового перемножителя и через первый ключ к третьему входу сумматора, управляющие входы ключей объединены и подключены к , выходу младшего разряда аналого- цифрового преобразователя.

xgK

12

i

ч) в

V«

Sh jfrfrt)

Фиг.1

x(t)

,(t)

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| Устройство для преобразования координат | 1983 |

|

SU1098009A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАКОПЛЕНИЯ ЭНЕРГИИ В МАТЕРИАЛЕ ПРИ ЦИКЛИЧЕСКОМ НАГРУЖЕНИИ | 1994 |

|

RU2087895C1 |

| Множительное устройство | 1984 |

|

SU1160442A1 |

| Преобразователь угол-код | 1986 |

|

SU1336242A1 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

8)0

Xfit)

g 4(t)

d}0 W

e)o

т

,

внишш

Заказ 908/57

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

Тираж 673 Подписное

Авторы

Даты

1986-02-28—Публикация

1984-07-05—Подача