1 п

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики.

Цель изобретения - повышение точности перемножения.

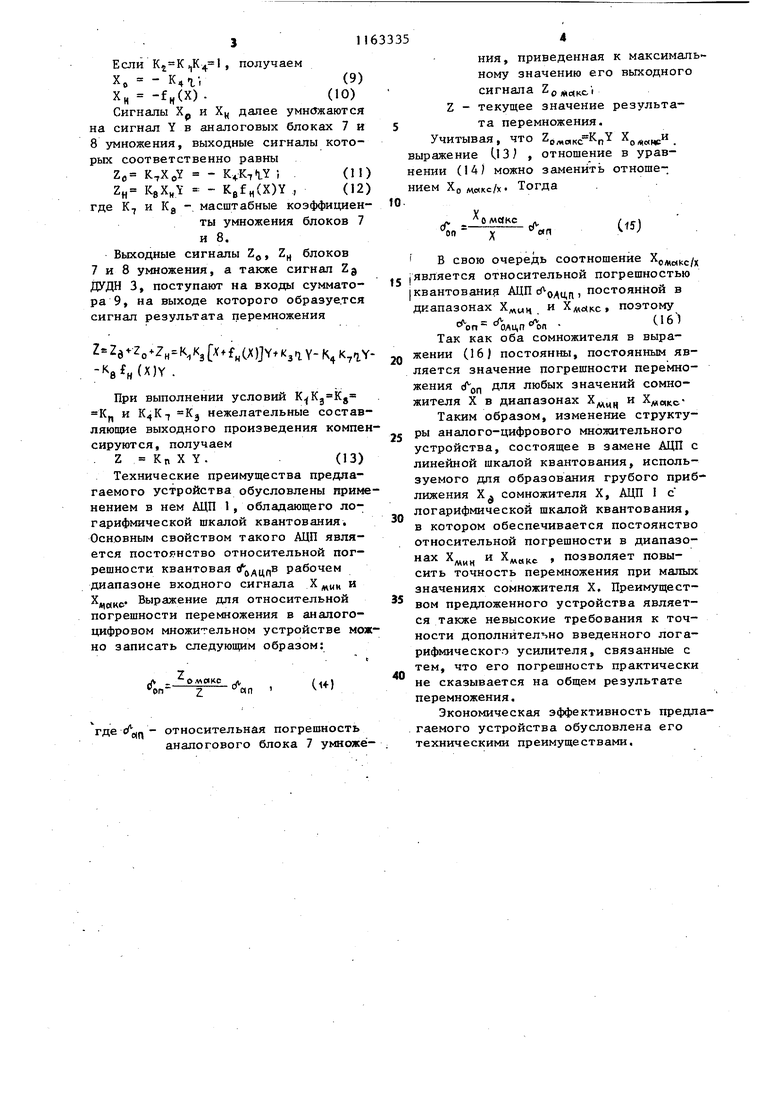

На чертеже представлена структурная схема аналого-цифрового множительного устройства.

Устройство содержит логарифмический аналого-цифровой преобразователь (АЦП/ 1, логарифмический усилитель 2, дискретно управляемый делитель 3 напряжения (ДУДН ), цифроаналоговый преобразователь (ЦАП ) 4, блок 5 вычитания, дополнительный блок 6 вычитания, аналоговый блок 7 умножения, дополнительный аналоговый блок 8 умножения, сумматор 9, первый 10 и второй 1I входы и выход 12. Входы логарифмических АЦП 1 усилителя 2 и суммирующий вход блока 6 вычитания объединены и образуют вход 11 устройства, выход АЦП 1 подключен к входу ЦАП 4 и управляющему входу ДУДН 3, аналоговый информационный вход которого, являющийся одновременно входом 10 устройства соединен с одним из входов блока 7 и одним из входов блока 8 умножения. Выход логарифмического усилителя 2 подключен к суммирующему и вычитающему входам блоков 5 и 6 вычитания соответственно, выход последнего соединен с вторым входом аналого вого блока 8 умножения, вычитающий вход блока 5 вычитания подсоединен к выходу ЦАП 4, а выход - к второму входу аналогового блока 7 умножения. Выходы ДУДН 3, а также блоков 7 и .8 умножения подключены к трем входам сумматора 9, выход которого является выходом 12 устройства.

Устройство работает следующим образом.

Один из перемножаемых сигналов X с входа 11 устройства поступает на вхор логарифмического АЦП 1. Характеристика последнего неравномерна: на область малых значений сигнала X приходится большее уровней квантования, чем на область больших. В своей основной части, заключенной в пределах диапазона Хуц„„, млис ° описывается соотношением

N

(1)

-г

мин

33352

где К - масштабный коэффициент аналого-цифрового преобразования;

Ч - абсолютная погрешность кван- 5 тования, приведенная к выходу АЦП I .

В диапазбне от нуля Хд,„ характеристика преобразования АЦП 1 линейна. Рассматриваемая характеристика преобразования может быть представлена суммой трех составляющих: первая составляющая - линейная аппроксимация характеристики АЦП 1, вторая некоторая нелинейная функция f(X), 15 третья - абсолютная погрешность квантования 1 АЦП 1. Таким образом, характеристика преобразования логарифмического АЦП 1 может быть представлена соотношением 20 + н(Х) +4- (2)

Выходной код 1 управляет коэффициентом передачи ДУДН 3, на информационный аналоговый вход которого поступает второй сомножитель 5 Y с входа 10 устройства. Сигнал на выходе ДУДН 3

ЕЙ (Х)-У-1-КзаУ,(3) где К, - масштабный коэффициент ДУДН

3.

Q Одновременно код N поступает на вход ЦАП 4, на выходе которого преобразуется в аналоговую форму

, ,(X)j + , (4) где К - коэффициент преобразования ЦАП 4.

Сомножитель X с входа 11 устройства поступает также на вход логарифмического усилителя 2, имеющего характеристику преобразования вида X

X

(5)

In X

мин

где К, - масштабный коэффициент усилителя 2.

Последняя характеристика, как и характеристика логарифмического АЦП 1, может быть представлена суммой линейной и нелинейной составляющих

Х + f к (X).(6)

Сигнал X с выхода логарифмического усилителя 2 подается на вычитающий и суммирующий входы блоков 6 и 5 вычитания соответственно, на другие входы которых поданы сигналы с входа 11 устройства и выхода ЦАП 4. На выходах блоков 5 и 6 образуются сигналы соответственно

(Х) -K,K,(X)(7) Х„ X - + „(Х). (8)

Если V.V. .J , получаем

X о К 4 г I

и (10)

Х„ (Х) .

Сигналы Хд и Хц далее умнсУжаются

и Х. на сигнал Y в аналоговых блоках 7 и 8 умножения, выходные сигналы которых соответственно равны

z, - ; (п

ZH - - KefH(X)Y ,

где К, и Kg -. масштабные коэффициенты умножения блоков 7 и 8.

Выходные сигналы Z,

блоков

7 и 8 умножения, а также сигнал Zg ДУДН 3, поступают на входы сумматора 9, на выходе которого образуется сигнал результата перемножения

Z- e-Zo ZH-K/jC fHCMjYtK.riY-K.K lY-S Hf lY.

При выполнении условий -Kj, и , Кз нежелательные составляющие выходного произведения компенсируются, получаем

Z Кп X Y.(13)

Технические преимущества предлагаемого устройства обусловлены применением в нем АЦП 1, обладающего логарифмической шкалой квантования. Основным свойством такого АЦП является постоянство относительной погрешности квантовая с о/уцпВ рабочем диапазоне входного сигнала X „ц и /чйкс Выражение для относительной погрешности перемножения в аналогоцифровом множительном устройстве можно записать следующим образом:

оллакс

(И)

(, 2

ап

где сЛ., - относительная погрешность

аналогового блока 7 умножёния, приведенная к максималь ному значению его выходного сигнала

Z - текущее значение результата перемножения. Учитывая, что . выражение (3) , отношение в уравнении (14 можно заменить отноше-. нием XO OIKC/X. Тогда

(12)

о MCJKC

(15)

с.

«п

i В свою очередь соотношение . |является относительной погрешностью квантовани АЦП , постоянной в диапазонах и XJ,. поэтому

С161

оп оли,п

Так как оба сомножителя в выражении (16) постоянны, постоянным является значение погрешности перемножения для любых значений сомножителя X в диапазонах Хд, и Х ощсТаким образом, изменение структуры аналого-цифрового множительного устройства, состоящее в замене АЦП с линейной шкалой квантования, используемого для образования грубого приближения Х сомножителя X, АЦП I с логарифмической шкалой квантования, в котором обеспечивается постоянство относительной погрешности в диапазонах Х и . , позволяет повысить точность перемножения при малых значениях сомножителя X. Преимуществом предложенного устройства является также невысокие требования к точности дополнительно введенного логарифмического усилителя, связанные с тем, что его погрешность практически не сказывается на общем результате перемножения.

Экономическая эффективность предлагаемого устройства обусловлена его техническими преимуществами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Гибридное множительное устройство | 1984 |

|

SU1171814A1 |

| Множительное устройство | 1984 |

|

SU1160442A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Устройство преобразования "аналог-код | 1979 |

|

SU834893A1 |

АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее цифроаналоговый преобразователь, блок вычитания, аналоговый блок умножения , сумматор и дискретно управля- емый делитель напряжения, информационный аналоговый вход которого соединен с одним из входов аналогового блока умножения и является первым входом устройства, а выход подключен к первому входу сумматора, второй,вход которого подключен к выходу аналогового блока умножения , а выход является выходом устройства, другой вход аналогового блока умножения соединен с выходом блока вычитания, подключенного вычитающим входом к выходу цифроаналогового преобразователя, отличающееся тем, что, с целью повышения точности, оно содержит логарифмический усилитель, дополнительный блок вычитания, дополнительный аналоговый блок умножения и логарифмический аналого-цифровой преобразователь, вход которого соединен с входом логарифмического усилителя и суммирующим входом дополнительного блока вычитания и являсл ется вторым входом устройства, а выход подключен к входу цифроаналогового преобразователя и к управляющему входу дискретно управляемого делителя напряжения, выход, логарифмического усилителя соединен с суммирующим входом блока вычитания Од и вычитающим входом дополнительного блока вычитания, подсоединенного 00 выходом к одному из входов допол00 нительного аналогового блока умножеCio СП ния, другой вход и выход которого подключены соответственно к первому входу устройства и к третьему выходу сумматора.

| Математическое моделирование и теория электрических цепей | |||

| Сборник, вып | |||

| П | |||

| Киев, Наукова думка, 1973, с.157 | |||

| Корн Г., Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины | |||

| М., Мир, 1967, с.395. |

Авторы

Даты

1985-06-23—Публикация

1983-12-06—Подача