i

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых и гибридных вычислительньк устройствах, а также в специализированных вычисли,тельных устройствах с различной формой представления информации для перемножения аналоговых сигналов с представлением результата в цифровой форме,

Известно устройство для перемножения аналоговых сигналов с цифровым выходом, содержащее два аналого-цифровых преобразователя следящего типа, коммутатор, сумматор-вычитатель и элементы управления tl3.

Недостаток устройства - ограничен ный частотный диапазон перемножаемых аналоговых сигналов.

Известно также аналого-цифровое множительное устройство, содержащее накапливающий сумматор, коммутатор, комбинационный сумматор, группу элементов ИЛИ, два блока сдвига кода последовательного приближения, распределитель импульсов и два аналогоцифровь1х: преобразователя, каждый из которых содержит компаратор, цифроаналоговый преобразователь и регистр последовательного приближения 12.

Данное устройство характеризуется пониженным быстродействием.

Наиболее близким к изобретению является инкрементный умножитель аналоговых сигналов, содержащий два аналого-цифровых преобразователя следящего типа с переменным шагом уравновешивания, первый из которых соединен информационным входом с шиной ввода первого сомножителя, тактирующим входом - с шиной ввода тактовых импульсов и с входом триггера, выходом знакового разряда, уравновешивающего кода - с первым входом первого сумматора по модулю два, а выходом знака рассогласования - с первым входом второго сумматора по модулю двaj подключенного вторым входом к выходу знакового разряда уравновешивающего кода второго аналого-цифрово го преобразователя следящего типа с переменным шагом ура1вновешивания, соединенного выходом знака рассогласования с вторьм входом первого сумматора по модулю два, информацион ным входом - с шиной ввода второго сомножителя, а тактирующим входом с выходом триггера, и блок сдвига.

138202

подключенный выходами к первой группе, входов комбинационного сумматора, соединенного второй группой входОв с выходами выходного регистра, 5 подключенного управляющим входом к шине ввода тактовых импульсов и к управляющим входам первого и второго аналого-цифровых преобразователей, а информационными входами - к выходам комбинационного сумматора, соединенного управляющим входом с выходом первого коммутатора, подключенного информационными входами к выходам сумматоров по модулю два, а управляющие ми входами - к управляющим входам второго и третьего коммутаторов и к выходам триггера, причем блок сдвига соединен информационными и управляющими входами с выходами второго и третьего коммутаторов соответственно, первая и вторая группы информационных входов второго коммутатора подключены к выходам уравновешивающего кода первого и второго аналого-цифровых преобразователей соответственно, кроме их знаковых разрядов, а первая и вторая группы информационных входов третьего коммутатора соединены с выходами кодов приращения первого и второго аналого-цифровых преобразователей, каждый из которых содержит группу пороговых элементов, подключенных входами к выходу вычитающего узла, а выходами - к информационным входам приоритетного бло-г ка, соединенного тактирующим входом с тактирующим входом накапливающего Сумматора, а выходами - с выходами кода приращения аналого-цифрового преобразователя и с информационными входами накапливающего сумматора, подключенного управляющим входом к выходу нуль-органа, а выходами разрядов - к входам цифроаналогового преобразователя, соединенного выходом с первым входом вычитающего узла, второй вход которого является информационным входом аналого-цифрового преобразователя, а выход подключен к входу нуль-органа, выход которого является выходом знака рассогласования аналого-цифрового преобразователя, а выходы разрядов накапливающего сумматора, включая его знаковый разряд, являются выходами уравновешивающего кода аналого-цифрового преобразователя .

3

Недостатком прототипа является пониженное быстродействие, обусловле ное тем, что на получение одного результата умножения затрачивается два такта работы.

Цель, изобретения - повышение быстродействия инкрементного умножителя .

Поставленная цель достигается тем, что в инкрементный умножитель аналоговых сигналов, содержащий два аналого-цифровых преобразователя следящего типа с переменным шагом уравновешивания, первьй из которых соединен информационным входом с шиной ввода первого сомножителя, тдктирующим входом - с шиной ввода тактовых импульсов и с входом триггера,

выходом знакового разряда уравновешивающего кода - с первьгм входом первого сумматора по модулю два, а выходом знака рассогласования - с пер.вым входом второго сумматора по модулю два, подключенного вторым входом к выходу знакового разряда уравновешивающего кода второго аналогоцифрового преобразователя следящего типа с переменным шагом уравновешивания, соединенного выходом знака рассогласования с вторым входом первого сумматора по модулю два, информационным входом - с шиной ввода второго сомножителя, а тактирующим входом - с выходрм триггера, и блок сдвига, подключенный выходами к первой группе входов сумматора, соединенного второй группой входов с выходами выходного регистра, введены дополнительные сумматор и блок сдвига, подключенные информационными входами к выходам уравновешивающего кода второго аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, кроме его знакового разряда, управляющими входами - к выходам кода приращения первого аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, а выходами к первой группе входов дополнительного сумматора, соединенного второй группой входов с выходами основного сумматора, входом управления режимом работы - с выходом второго сумматора по модулю два, а выходами - с информационными входами выходного регистра, подключенного тактирующим входом к выходу триггера, причем

204

выход первого .сумматора по модулю два соединен с входом управления режимом работы основного сумматора, а выходы уравновешивающего кода первого аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, кроме его знакового разряда, подключены к информационным входам основного блока

сдвига, соединенного управляющими входами с выходами кода приращения второго аналого -цифрового преобразователя следящего типа с переменным шагом уравновешивания.

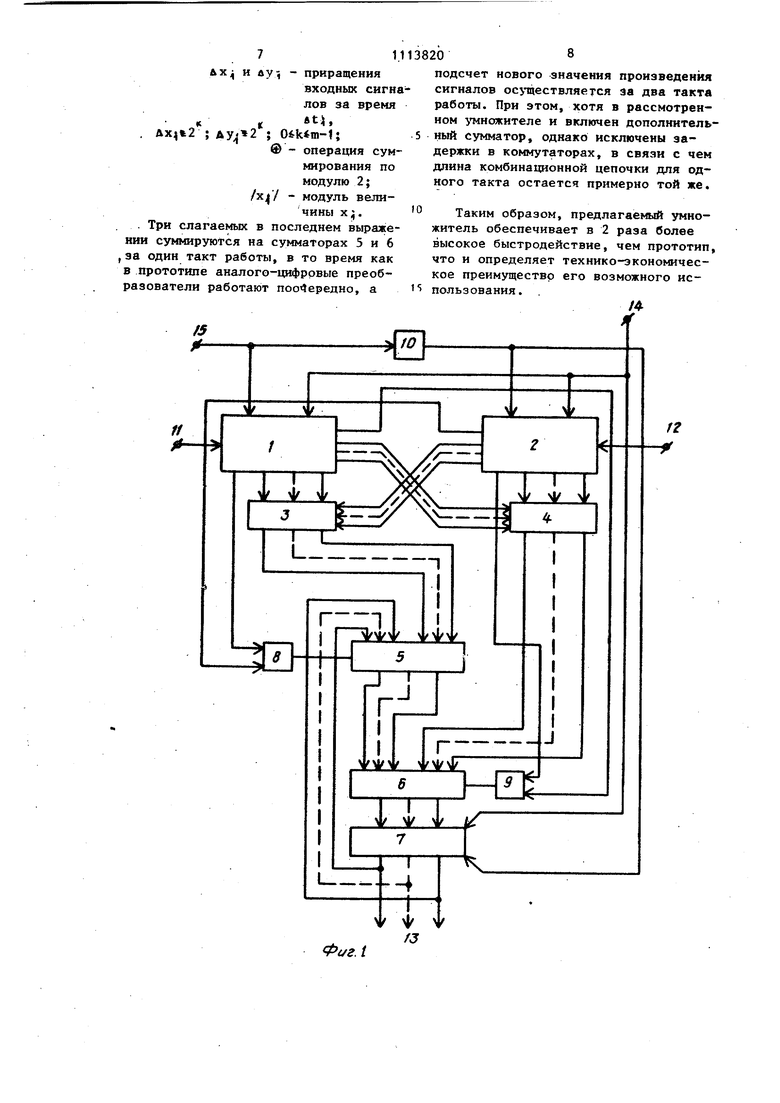

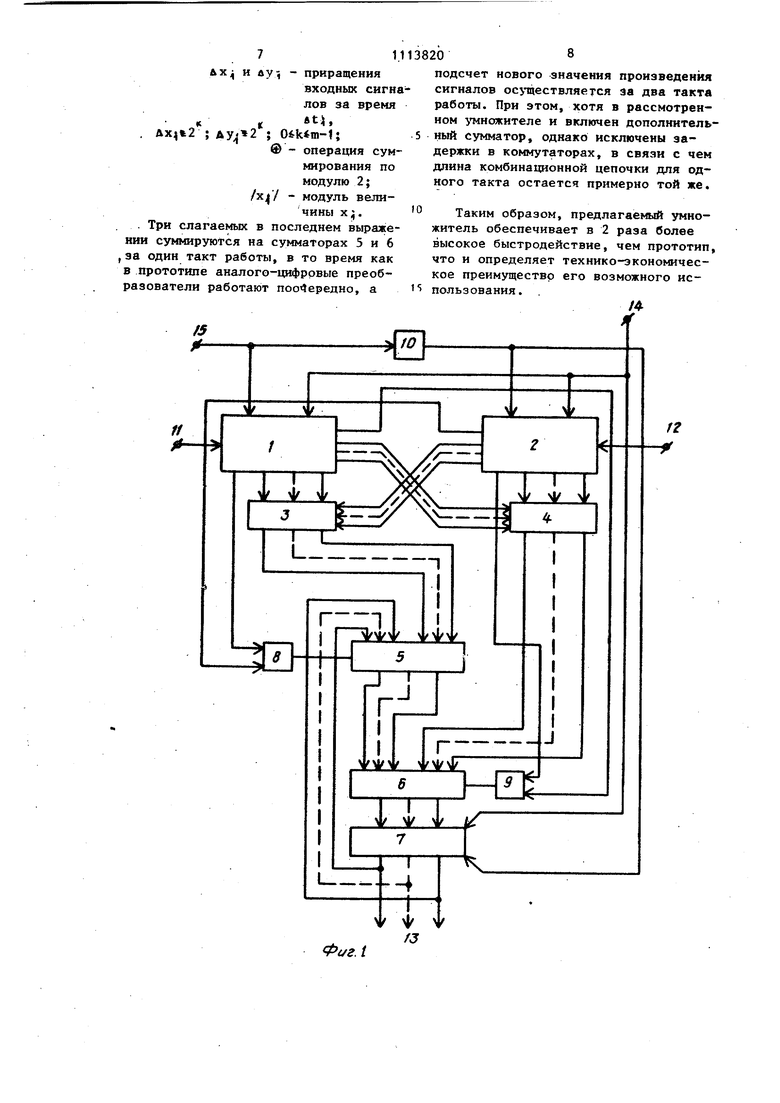

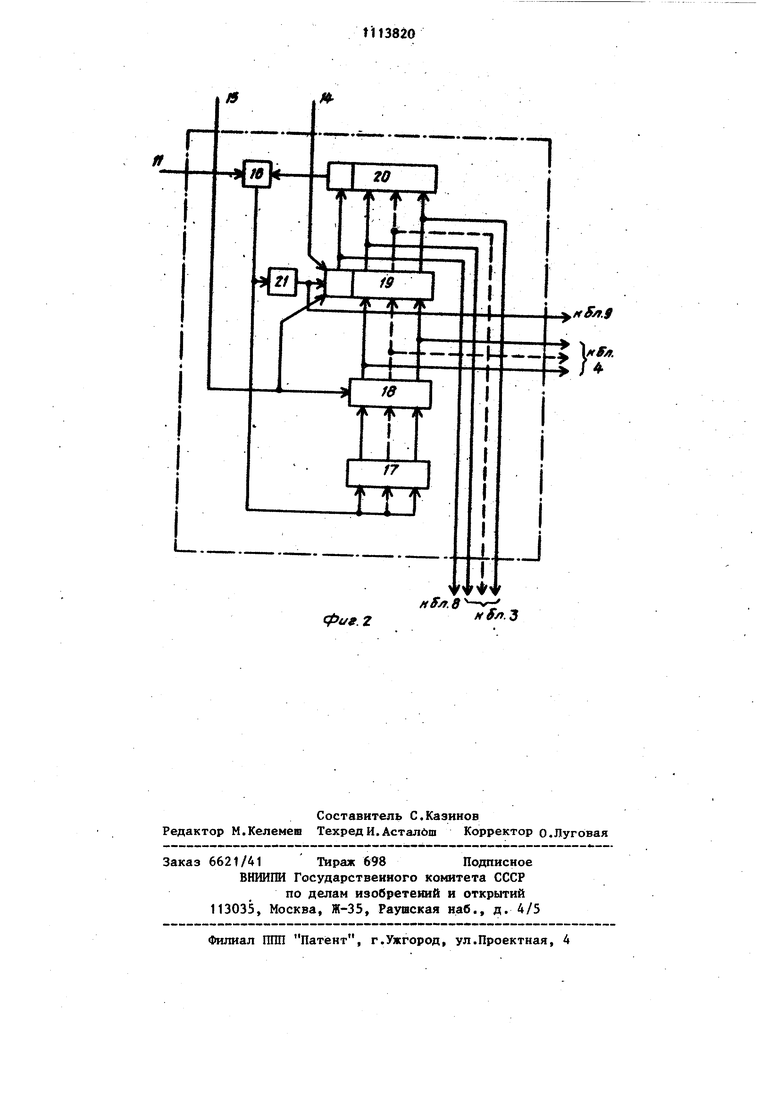

На фиг. 1 приведена блок-схема инкрементного умножителя аналоговых сигналов; на фиг. 2 - возможный вариант выполнения блок-схемы каждого из аналого-цифровых преобразователей

следящего типа с переменным шагом уравновешивания.

Инкрементный умножитель аналоговых .сигналов содержит первый и второй аналого-цифровые преобразователи 1

и 2 следящего типа с переменным шагом уравновешивания, основной и дополнительный блоки 3 и 4 сдвига, основной и дополнительный сумматоры 5 и 6, выходной регистр 7, первый и второй сумматоры 8 и 9 по модулю два, триггер 10, шину 11 ввода первого сомножителя, шину 12 ввода второго сомножителя, выходы 13 инкрементного умножителя, шину 14 начальной установки и шину 15 ввода

тактовых импульсов. Каждый из аналого-цифровых преобразователей 1 и 2 (фиг. 2) содержит (аналогично преобразователям прототипа) вычитающий

узел 16, группу 17 пороговых элементов, приоритетный блок 18, накапливающий сумматор. 19, цифроаналоговый преобразователь 20 и нуль-орган 21. Инкрементный умножитель аналоговых

сигналов работает следующим образом.

Сигналом начальной установки с шины 14 осуществляется сброс в нулевое состояние аналого-цифровых

преобразователей 1 и 2 (накапливающих сумматоров 19, входящих в их состав) и выходного регистра 7. При подключении аналоговых сигналов к шинам 11 и 12 ввода сомножителей и подаче тактирующих импульсов на шину 15 запускается в работу первый аналогоцифровой преобразователь 1 и с задержкой на один такт через триггер 10 51 (типа D) второй аналого-циФровой пре образователь 2. Аналого-цифровой преобразователь (фиг. 2) работает следующим образом. Сигналом Начальная установка с шины 14 осуществляется сброс в О накапливающего сумматора 19. С шины 11 подключается аналоговый сигнал а с шины. 15 - тактирукш ие импульсы, Вычитанедий узел 16 определяет разность между входным напряжением и уравновешивающим напряжением обратно связи с выхода цифроаналогового преобразователя 20, которая приклады- . вается к входу нуль-органа 21 и входам всех пороговых элементов группы 17. Знакочувствительные пороговые элементы срабатывают при достижении напряжением разности значений порогов, на которые настроены (например, по двоичному закону: 1, 2, 4, ...,2 условных единиц, где m - количество элементов группы). Приоритетный блок 18 в моменты времени, определяе мые тактовыми импульсами, вьзделяет старший по весу пороговый элемент из числа сработавших. Нуль-орган 21 в те же моменты времени определяет знак напряжения разности, которьй является сигналом Знак рассогласова ния аналого-цифрового преобразовате ля. Коды с. выхода приоритетного блока 18 представляют собой приращения входного сигнала, скругленные до зна чения кратного степени двойки, т.е.. представляют собой одну единицу в со ответствующем разряде кода (позицион ный код). Коды с выхода приоритетног блока 16 являются сигналом Кода приращения аналого-цифрового преобразователя. Код знака напряжения раз ности с выхода нуль-органа 21 настра ивает накапливающий сумматор 19 по управляющему входу на выполнение опе рации Сложение или Вычитание. В моменты времени, определяемые такт выми импульсами, накапливающий сумматор 19 добавляет к своему содержимому или вычитает из него единицу соответствующего разряда, поступившую с приоритетного блока 18. ВЬЕХОДЫ накапливаннцего сумматора 19 являются выходами уравновешивающего кода аналого-цифрового преобразователя и управляют цифроаналоговым преобразователем 20, стремясь уменьшить величину рассогласования между входным напряжением и напряжением обратной 06 связи с выхода цифроаналогового преобразователя 20. Аналого-цифровой преобразователь 2 вьтолнен полностью аналогично аналого-цифровому преобразователю 1. Уравновешивающие коды с выходов Первого 1 и второго 2 аналого-цифровых преобразователей (кроме знаковьпс разрядов) сдвигаются под управлением выходов величины приращения второго 2 и первого 1 аналого-щ1фровьк преобразователей и поступают на соответствукмцие группы входов основного 5 и дополнительного 6 суьматоров. Первый 8 и второй 9 сумматоры по модулю два анализируют знак выходного кода одного аналого-цифрового преобразователя и знак приращения другого и управляют режимом работы (Сложение или Вычитание) сумматоров 5 и 6. Сумматор по модулю два выдает код О (Сложение) при равенстве знаков и код 1 (Вычитание) при разных знаках. Таким образом, в каждом такте работы умножителя осуществляется добавление к содержимому выходного регистра 7 выходного кода первого аналого-цифрового преобразователя 1., сдвинутого на число разрядов, соответствующее величине приращения второго аналого-цифрового преобразователя 2, и задержанного на один такт выходного кода второго аналогоцифрового преобразователя 2, сдвинутого на число разрядов, соответст-г вующее величине приращения первого аналого-цифрового преобразователя 1 , При этом в выходном регистре 7 после каждого тактирующего импульса фиксируется код текущего значения произведения двух аналоговых сигналов, который и поступает на выходы 13 устройства. Алгоритм работы умножителя может быть описг.н следующими выражениями: X, .х,-axil 4м 4 1 - операции вьтолняют-у. у- i ftV- ( t- f ч ) ся в аналого-цифровых преобразователях 1 и 2 i -У 1 У; (signx,@signfty) /Х4и//4У1 / (signy-@signuXi) /у{//ftx /, где х ,у. и х, у - цифровые значения входньо: сигналов в моменты врем€ ни t и t,;

AX;j И лу - приращения

входных сигналов за время

, tb . ; Ау.2 ; Oik in-1;

® - операция суммирования по модулю 2;

- модуль величины х;.

. Три слагаемых в последнем выражении суммируются на сумматорах 5 и 6 ,за один такт работы, в то время как в прототипе аналого-цифровые преобразователи работают поочередно, а

подсчет нового значения произведения сигналов осуществляется эа два такта работы. При этом, хотя в рассмотренном умножителе и включен дополнительный сумматор, однако исключены задержки в коммутаторах, в связи с чем длина комбинационной цепочки для одного такта остается примерно той же.

Таким образом, предлагаемый умножитель обеспечивает в 2 раза более высокое быстродействие, чем прототип, что и определяет технико-экономическое преимущество его возможного использования.

/А

фие.г

ftS/f.8 tf ОЛ. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1408531A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

ИНКРЕМЕНТНЫЙ УМНОЖИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ, содержащий два аналого-цифровых преобразователя следящего типа с переменным шагом уравновешивания, первый из которых соединен информационным входом с шиной ввода первого сомножителя, тактирующим входом - с шиной ввода тактовых импул.ьсов и с входом триггера, выходом знакового разряда уравновешивающего кода - с первым входом первого сумматора по модулю два, a выходом знака рассогласования - с первым входом второго сумматора по модулю два,, подключенного вторым входом к выходу знакового разряда уравновешивающего кода второго аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, соединенного выходом знака рассогласования с вторым входом первого сумматора по модулю два, информационным входом - с шиной ввода второго сомножителя , a тактирующим входом - с выходом триггера, и блок сдвига. подключенный выходами к первой группе входов сумматора, соединенного второй группой входов с выходами выходного регистра, отличающийся тем, что, с целью повышения быстродействия инкрементного умножителя, в него введены дополнительные сумматор и блок сдвига, подключенный информационными входами к вькодам уравновешивающего кода второго аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, кроме его знакового разряда, управляющими входами - к выходам кода приращения первого аналого-цифрового преобразователя следя(Л щего типа с переменным шагом уравновешивания, a выходами - к первой группе входов дополнительного сумматора, соединенного второй группой входов с выходами основного сумматора, входом управления режимом работы с выходом второго сумматора по модулю два, a выходами - с информационными входами выходного регистра, подключенного тактируюшям входом к вькоду триггера, причем выход первого сумматора по модулю два соединен с входом управления режимом работы основного сумматора, a выходы уравновешивающего К.1да первого аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания, кроме его знакового разряда, подключены к информационным входам основного блока сдвига, соединенного управляющими входами с выходами кода приращения второго аналого-цифрового преобразователя следящего типа с переменным шагом уравновешивания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровое множительное устройство | 1974 |

|

SU499569A1 |

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-15—Публикация

1983-06-27—Подача