транзисторов соединены соответственно с катодом первого и анодом пя- I того прямосмещенных диодов, соединенные соответственно через первый и второй источники тока с положительной и отрицательной шинами источника питаний, причем коллекторы второго и пятого транзисторов соединены с эмиттерами соответственно седьмого и восьмого транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Усилитель | 1980 |

|

SU987795A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Транзисторный ключ | 1985 |

|

SU1283957A1 |

| Усилитель | 1988 |

|

SU1720146A1 |

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2092969C1 |

| Коммутирующее устройство | 1990 |

|

SU1793541A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Интегральный усилитель мощности для магнитофона | 1979 |

|

SU902205A1 |

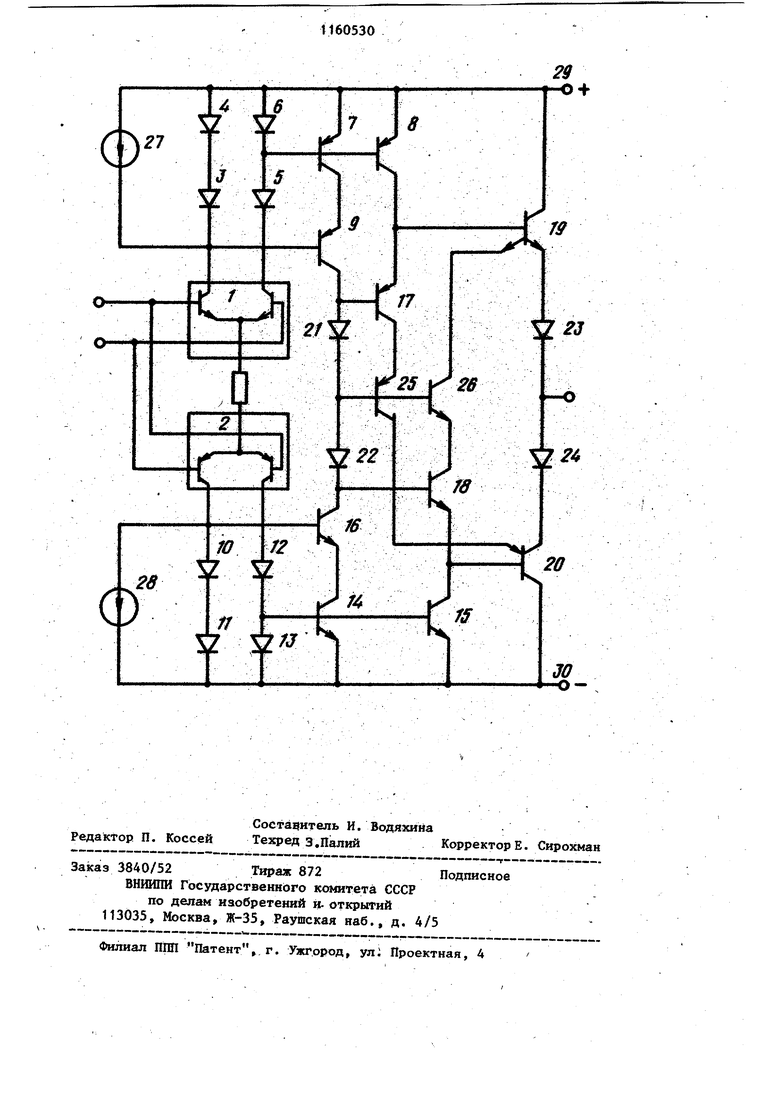

ОПЕРАЦШНЙЫЙ УСЩШТЕЛЬ, срдержапщй первый и второй параллельно включенные дифференциальные каскады, причем первый дифференциальный каскад выполнен на транзисторах, имеющих п-р-п-структуру, коллектор одного иэ которых через последовательно соединенные первый и второй прямдсмещейные диоды, а коллектор другого - через последовательно соединенные третий и четвертый прямосмещённые диоды соединены с положительной шиной источника питания, а второй дифференциальный каскад выполнен на транзисторах, имеюпдах р-п-р-структуруу коллектор одного из которых через последова тельно соединенные пятый и шестой прямосмещенные диоды, а коллектор другого - через похУ1едовательно соединенные седьмой ц восьмой прямосмещенные диоды соединены с отрицательной шиной источника питания, причем катод четвертого прямосмещенного диода соединен с базами первого 9 второго транзисторов, эмиттеры которых подключены к положительной шине источника питания. при этом коллектор первого транзистора соединен с эмиттером третьего транзистора, анод восьйого прямосмещенного диода соединен с базами четвертого и пятого транзисторов, этшттеры которых подключены к отрицательной шине источника питания, 1фи этом коллектор четвертого транзистора подключен к эмиттеру шестого транзистора, причем Коллекторы третьего и шестог о транзисторов Объединены через последовательно соединенные девятый и десятый прямосмещенные Диоды и подключены к соответственно седьмого и восьмого транзисторов, эмиттеры которых соединен с базами соответственно первого и второго выходных двухэмиттерных транзисторов, первые эмиттеры которьк объединены через последовательно соедийеиные одиннадцатый и двенадцатый прямосмещенные диоды, а коллекторы соединены соответственно с.положительной и отрицательной 1пинами источника питания , а также девятый и десятый транзисторы, о т л и ч а ю.щ и Йс я тем, что, с целью повышения стабильности режима работы, в него введены первый и второй источники тока, а базы девятого и десятого транзисторов объединены и подключены к общей точке девятого и десятого прямосмёщенньрс диодов, эьшттеры к коллекторам соответственно седьмого и восьмого транзисторов, а коллект ы - к вторым эмиттерам соответственно второго и первого выходных двухэ 01ттерных. транзисторов, при этом базы третьего и шестого

Изобретение относится к радиотехнике и может использоваться в радиоэлектронных системах я, средствах связи.

Известен быстродействующий опера ционнь } усилитель, содержащий входной дифференциальный каскад, пр1едвыходной и выходной двухтактный каскады, выполненные на транзисторах, имеющих разную структуру |3J .

Однако в операционном усилителе при примененш транзисторов разной .структуры имеются дополнительное ограничение на допустимые отклонени между усилительными свойствами транзисторов разной структуры.

Наиболее близким к изобретению по технической сущности является операционный усилитель, содержащий первый и второй параллельно включен ные дифферен1щальные каскады, (причем первый дифференциальный каскад выполнен на транзисторах, имекидих п-р-п-структуру, коллектор одного из которых через последовательно соединенные первый и второй прямосмещенные диоды, а коллектор другого - через последовательно соединенные третий и четвертый прямосмещенные диоды соеданеиы с положительной шиной источника питают, а второй дифференциальный каскад выполнен на транзисторах, имеющих р-п-р-струтуру, коллектор одного из которых через последовательно соединенные пятый и шестой прямосмещенные диоды, а коллектор другого - через последовательно соеданенные седьмой и восьмой прямосмещенные диоды соединены с отрицательной шиной источника питания, причем катод четвертого прямосмещенного диода соединен с базами первого и второго транзисторов, эмиттеры которых подключены к положительной шине источника totтания при этом коллектор первого транэисто{ а соединен с эмиттером третьего транзистора, анод восьмого прямосмещенного диода соединен с базами четвертого и пятого транзисторов, эмиттеры которых подключены к отрицательной шине источника питания,- при этон коллектор четвертого транзистора подключен к эмиттеру шестого транзистора, причем коллекторы третьего и шестого транзисторов объеданены через последовательно соединенные девятый и десятый прямосмецеиные диоды и . подключены к базам соответственно . и восьмого транзисторов, эмиттеры которых соеданены с база1ми соответственно первого и второго выходных двухэмитте{жых транзисторов, первые эмиттеры которых объединены через последовательно соединенные одиннадцатый и двенадцатый прямосмещенные диоды, а коллекторы соединены соответственно с положительной и отрицательной шинами источника штания, а также . Девятый и десятый транзисторы } .

Однако в известном устройстве проявляется зависимость напряжения смещения от усилительных свойств транзисторов п-р-п- и р-п-р-структуры, что снижает стабильность реясима работы операционного усилителя.

.Цель изобретения - повьшхение стабильности режима работы операциного усилителя.

Цель достигается тем, что в операционный усилитель, содержащий первьШ и второй параллельно включенные дифференциальные каскады, причем первый дифференциальный каскад выполнен на транзисторах, имею1Е91х п-р-п-структуру, коллектор одного из которых-через последовательно соединенные первый и второй прямосмещенные дноды, а коллектор другого - через последовательно соединенные третий и четвертый прямосмещенные диоды соединены с положитель ной шиной источника питания, а второй дифференциальный каскад 8ыпол ней на транзисторах, имеющих р-п-рструктуру,,коллектор одного из кото рых через .последовательно соединенные пятый и шестой прямосмещенные диоды, а коллектор другого - через последовательно соединенные седьмой и восьмой прямосмещенные диоды соединены с отрицательной шиной источника питания, причем четвертого, пряносмещенного диода соединен с базами первого и второго гран зисторов, эмиттеры которых подключены к положительной шине источника питания, при этом коллектор пе вого транзистора .соединен с эмиттр ром третьего транзистора, анод вось мого прямрсмёщенного дирда соединен с четвертого и пятого транзисторов, эмиттеры которых подключены к отрицательной пине источника питания, при этрм коллектор четвертого транзистрра прдключен эмиттеру шестогр транзистора, приче коллекторы третьего:и ирвстрго трзнзисторов через прследо ательно соединенные девятьШ и лес.я тый прямосмещек1шё диоды к подключены к базам сортветстиенно седьмого и врсьнрг } транзисторов, эмиттеры которых еоединёны с базами соответственно первого и второго выходных двухэмиттер11ых транзисторов пе вце эмиттеры . объединейы через последовательно соединенные одиннадцатый и двенадцатый прямосме щенные диоды, а коллекторы соединены сортветственно с положительной и отрицательной шинами источника пита ния, а также девятый и десятый тран зисторы, введешь пбрвь1й и второй источники тока, а базы девятого и десятого транзисторов рбьединены и подключены к общей трчкё девятого и десятого прямосмещенных диодов, эмиттеры - к коллекторам срответственно седьмрго и восьмого тр нзисторрв, а коллекто Ьы - к вторьм терам соответственно второго и пер вого выходных двухэмиттерных транзисторов, при этом базы третьего и шестого транзисторов соединены 304 соответственно с первого и анодом пятого прямосмещенных диодов, соединенные соответственно через пер вый и второй источники тока с поло жительной и отрицательной шинами источника питания, причем коллекторы второго и пятого транзисторов соединены с эмиттерами соответственно седьмого и восьмого транзисторов. На чертеже представлена принципиальная электрическая схема операционного усилителя. Операционный усилитель содержит первый и второй дифференциальные каскады J и 2, первый, второй, третий , четвертый прямосмещенные диоды 3-6, первый, второй, третий транзисторы 7-9, цятый, шестой, седьмой, восьмой прямосмещенные диоды 10-13, четвертый шестой, седьмой, восьмой транзисторы 14-18, первый и второй выходные двухэмиттернме транзисторы 19 и 20, девятый, деся тыЙ, одиннадцатый, двенадцатый прямосмещеяные дирды 21-24, девятый и десятый транзисторы 25 и 26, первый и второй источники 27 и 28 тока, положительную и ртрицательную шины 29 и 30 источника питания. Операционный усилитель работает следукяцим образом, Выходной сигнал вызьгаает изменения коллекторных трков в первом и втором дифференциальных каскадах 1И 2 и через диодные цепи данные изменения отражаются в каскадно соединенных первом, третьем и четвертом, шестом транзисторах 7, 9 и 14, 16 Для получения максимального размаха сигнала, для уменьшения напряжения смещения требуются идентичные значения коллекторных токов в третьем и шестом транзисторах 9 я 16. Однакр, в зависимости от коэффициентов уснпения по току п-р-п-() и р-п-р (/)-транзисторов будет наблюдаться рпределенный разбаланс, который можно выразить ерез приведенный разбаланс, через приведенное Ко входу напряжение смещения Зк« где Ч - температурный потенциал, Чэ/-) оялекторный ток третьего (шестого) транзистора 9 (16);

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шшо В.Л | |||

| Линейные интегральные схемы в радиоэлектронной аппаратуре | |||

| Mi, Советское радио 1979, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

| Верхний многокамерный кессонный шлюз | 1919 |

|

SU347A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-12—Подача