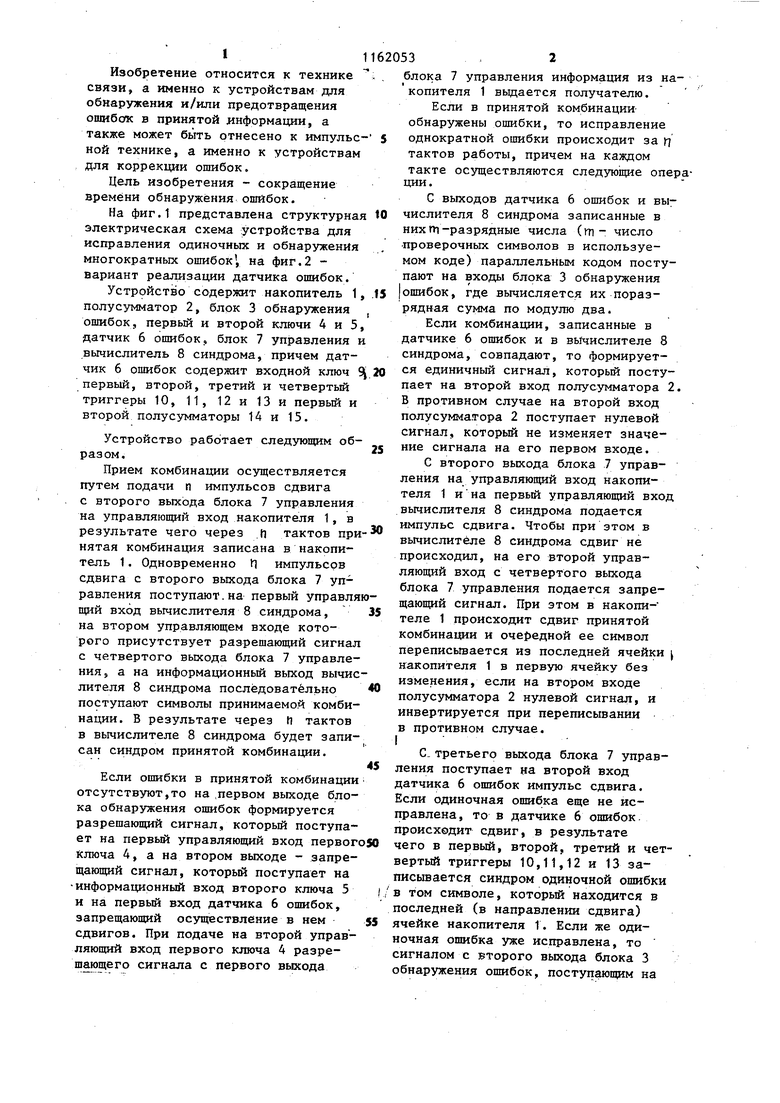

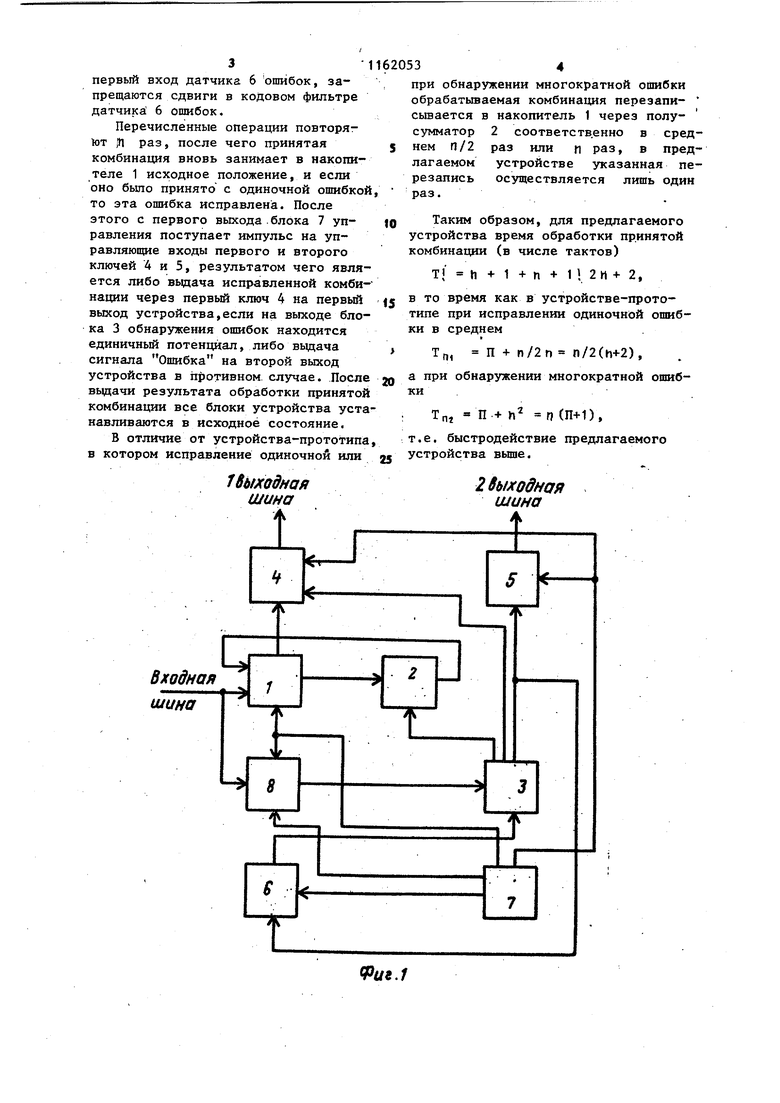

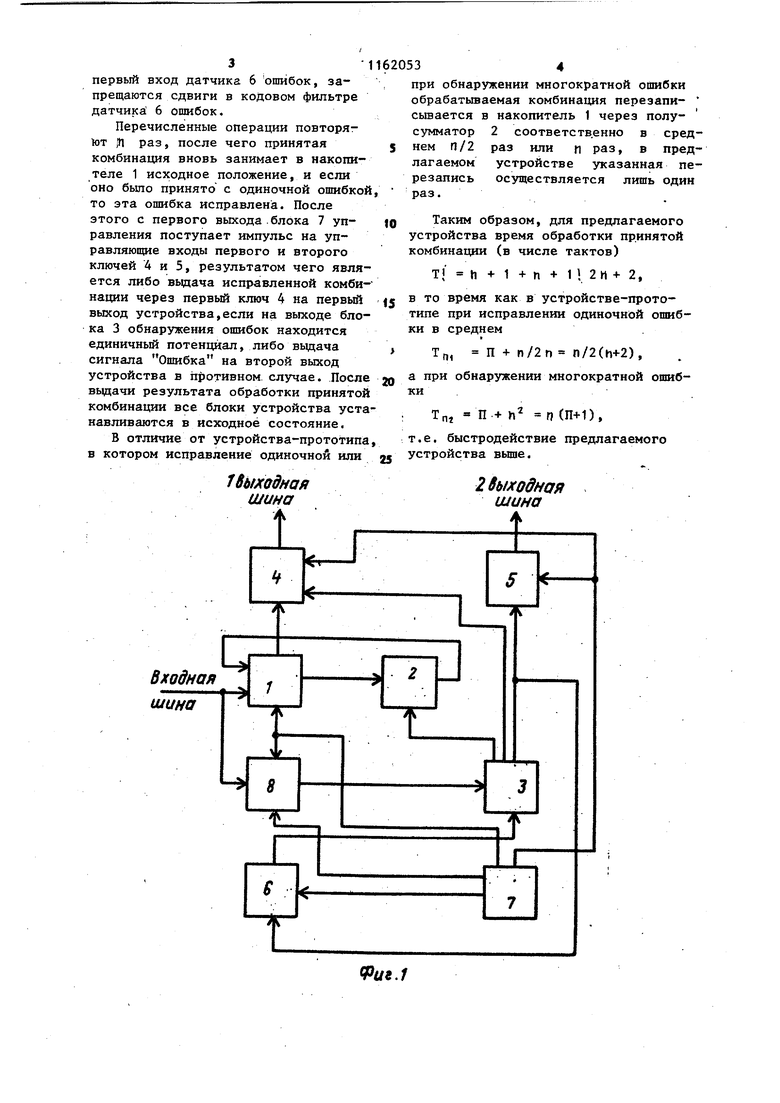

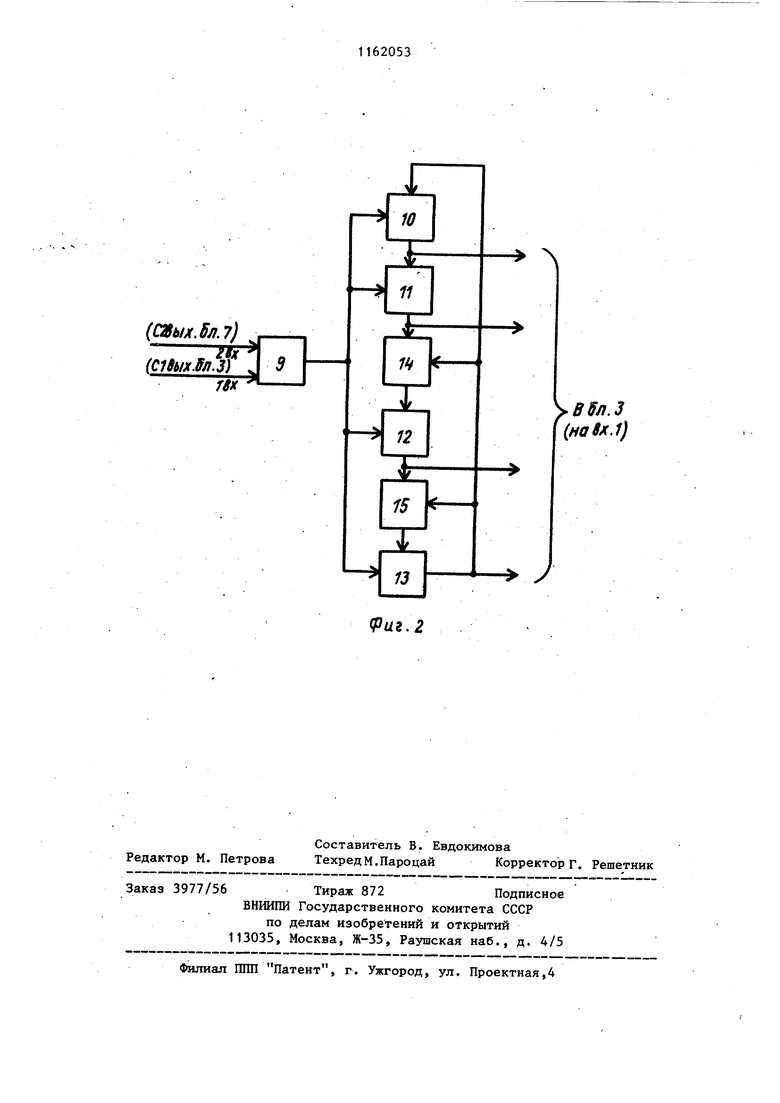

Изобретение относится к технике связи, а именно к устройствам для обнаружения и/или предотвращения ошибсж в принятой информации, а также может быть отнесено к импульс ной технике, а именно к устройствам для коррекции ошибок. Цель изобретения - сокращение времени обнаружения ошибок. На фиг.1 представлена структурная электрическая схема устройства для исправления одиночных и обнаружения многократных ошибок , на фиг.2 вариант реализации датчика ошибок. Устройство содержит накопитель 1 полусумматор 2, блок 3 обнаружения ошибок, первый и второй ключи 4 и 5 датчик 6 ошибок, блок 7 управления и вычислитель 8 синдрома, причем датчик 6 ошибок содержит входной ключ первый, второй, третий и четвертьй триггеры 10, 11, 12 и 13 и первый и второй полусутчматоры 14 и 15. Устройство работает следуюпщм образом. Прием комбинации осуществляется путем подачи п импульсов сдвига с второго выхода блока 7 управления на управляющий вход накопителя 1, в результате чего через .Ц тактов при нятая комбинация записана в накопитель 1. Одновременно II импульсов сдвига с второго выхода блока 7 управления поступают.на первый управля щий вход вычислителя 8 синдрома, на втором управляющем входе которого присутствует разрешающий сигнал с четвертого выхода блока 7 управления, а на информационный выход вычис лителя 8 синдрома последовательно поступают символы принимаемой комбинации. В результате через П тактов в вычислителе 8 синдрома будет записан синдром принятой комбинации. Если ошибки в принятой комбинации отсутствуют,то на .первом выходе блока обнаружения ошибок формируется разрешающий сигнал, который поступает на первый управляю1дий вход первог ключа 4, а на втором выходе - запрещающий сигнал, который поступает на -информационный вход второго ключа 5 и на первый вход датчика 6 ошибок, запрещающий осуществление в нем сдвигов. При подаче на второй управляющий вход первого ключа 4 разрешающего сигнала с первого выхода блока 7 управления информация из накопителя 1 выдается получателю. Если в принятой комбинацииобнаружены ошибки, то исправление однократной ошибки происходит за п тактов работы, причем на каждом такте осуществляются следуюш;ие операции. С выходов датчика 6 ошибок и вычислителя 8 синдрома записанные в нихm-разрядные числа (щ - число проверочных символов в используемом коде) параллельным кодом поступают на входы блока 3 обнаружения ошибок, где вычисляется их поразрядная сумма по модулю два. Если комбинации, записанные в датчике 6 ошибок и в вычислителе 8 синдрома, совпадают, то формируется единичный сигнал, который поступает на второй вход полусумматора 2. В противном случае на второй вход полусумматора 2 поступает нулевой сигнал, который не изменяет значение сигнала на его первом входе. С второго выхода блока 7 управления на управляющий вход накопителя 1 ина первый управляющий вход вычислителя 8 синдрома подается импульс сдвига. Чтобы при этом в вычислителе 8 синдрома сдвиг не происходил, на его второй управляющий вход с четвертого выхода блока 7 управления подается запрещающий сигнал. При этом в накопителе 1 происходит сдвиг принятой комбинации и очередной ее символ переписьтается из последней ячейки накопителя 1 в первую ячейку без изменения, если на втором входе полусумматора 2 нулевой сигнал, и инвертируется при переписывании в противном случае. I С-третьего выхода блока 7 управления поступает на второй вход датчика 6 ошибок импульс сдвига. Если одиночная ошибка еще не исправлена, то в датчике 6 ошибок, происходит сдвиг, в результате чего в первый, второй, третий и четвертый триггеры 10,11,12 и 13 записывается синдром одиночной ошибки в том символе, который находится в последней (в направлении сдвига) ячейке накопителя 1. Если же одиночная ошибка уже исправлена, то сигналом с второго выхода блока 3 обнаружения ошибок, поступающим на

первый вход датчика 6 ошибок, запрещаются сдвиги в кодовом фильтре датчика 6 ошибок.

Перечисленные операции повторяет у раз, после чего принятая комбинация вновь занимает в накопителе 1 исходное положение, и если оно бьто принято с одиночной ошибкой то эта ошибка исправлена. После этого с первого выхода блока 7 управления поступает импульс на управляющие входы первого и второго ключей 4 и 5, результатом чего является либо вьщача исправленной комбинации через первый ключ 4 на первый выход устройства,если на выходе блока 3 обнаружения ошибок находится единичный потенциал, либо вьщача сигнала Ошибка на второй выход устройства в противном случае. После вьщачи результата обработки принятой комбинации все блоки устройства устанавливаются в исходное состояние.

В отличие от устройства-прототипа в котором исправление одиночной или

Пыходная шина

при обнаружении многократной ошибки обрабатываемая комбинация перезаписывается в накопитель 1 через полусумматор 2 соответственно в среднем П/2 раз или м раз, в предлагаемом устройстве указанная перезапись осуществляется лишь один раз.

Таким образом, для предлагаемого устройства время обработки принятой комбинации (в числе тактов)

ц + 1+п- -112н+2.

Т

в то время как в устройстве-прототипе при исправлении одиночной ошибки в среднем

П + п/2п П/2(и+2),

П4

а при обнаружении многократной ошибки .

, Тп4 П + h Г) (П+1),

т.е. быстродействие предлагаемого устройства вьш1е.

28ыходная шина

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1061275A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1078655A2 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления и обнаружения ошибок | 1984 |

|

SU1205312A2 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1980 |

|

SU886281A2 |

| Устройство для исправления ошибок | 1987 |

|

SU1501283A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для контроля цифровых данных | 1985 |

|

SU1381718A1 |

1. УСТРОЙСТВО Щ1Я ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные накопитель, первьй информационный вход которого является входом устройства, и полусумматор, выход которого подключен к второму информационному входу накопителя, второй выход которого подключен к информационному входу первого ключа, к первому управляющему входу которого подключен первый выход блока обнаружения ошибок,второй выход-которого подключен к первому входу датчика ошибок и к информационному входу второго ключа, управляющий вход которого объединен с вторым управляющим входом первого ключа и соединен с первым выходом блока управления, второй и третий выходы которого подключены соответственно к управляющему входу накопителя и к второму входу датчика ошибок, причем выходы первого и второго ключей являются выходами устройства, отличающееся тем, что, с целью сокращения.времени обнаружения ошибок, в него введен вычислитель синдрома, при этом информационный вход вычислителя синдрома объединен с первым информационным входом накопителя, к первому и второму управляющим вхо- . дам вычислителя синдрома подключены соответственно второй и четвертый выходы блока управления, а выход вычислителя синдрома подключен к первому входу блока обнаружения ошибок, к второму входу которого подключен выход датчика ошибок, а дополнительный выход блока обнару(/) жения ошибок подключен к другому входу полусумматора. 2. Устройство по п.1, о т л ичающееся тем, что датчик ошибок содержит входной ключ и последовательно соединенные первый и второй триггеры, первый полусумматор, третий триггер, второй полусумматор и четвертый триггер, прямой выход которого подключен к СП информационному входу первого триггера и к вторым входам первогои второго полусзп маторов, выход входного ключа подключен к управляющим входам первого, второго, третьего и четвертого триггеров, выходы которых являются выходами датчика ошибок.

Ui.1

Риг. 2

| Устройство для исправления ошибок | 1978 |

|

SU721817A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1976 |

|

SU625312A1 |

| . | |||

Авторы

Даты

1985-06-15—Публикация

1983-04-22—Подача