(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и исправления информации | 1977 |

|

SU696466A1 |

| Устройство для контроля и исправления передаваемой информации | 1975 |

|

SU572829A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1383509A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Устройство для исправления ошибок в корректирующем коде | 1975 |

|

SU592018A1 |

| Устройство для исправления @ -кратных ошибок | 1985 |

|

SU1425849A2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для исправления ошибок в дискретной информации | 1978 |

|

SU860335A1 |

| Устройство для исправления двойных и обнаружения многократных ошибок циклическими кодами | 1983 |

|

SU1185611A1 |

i

Изобретение относится к области цифровой вычислительной техники и передачи информации и может быть использовано в цифровых вычислительных машинах, в которых информация передается и обрабатывается в корректирующем коде.

Известно устройство для исправления ошибок 1, которое содержит корректор, обнаружитель одиночной и двойной ошибок, локализатор одиночной ошибки, причем первые входы корректора, выходы локализатора и обнаружителей ошибок соединены со входными шинами устройства, а выходы локализатора через дешифратор подключены ко вторым входам корректора, выходы которого подключены к выходным шинам устройства.

Недостатком этого устройства являются ограниченные функциональные возможности, поскольку оно не может исправлять двойные ошибки.

Наиболее близким по технической сущности и достигаемому результату к данному изобретению является устройство для исправления ошибок 2, содержашее обнаружители ошибок кратности t и t + 1, локализатор ошибок кратности t, группу элементов И, группу элементов ИЛИ, регистр, блок управления инверсией, причем входы обнаружителей ошибок кратности t и t + 1 подключены к прямым и инверсным входным

шинам, выходы локализатора ошибок кратности t соединены с первыми входами корректора ошибок кратности t, выходы которого являются вы.ходными шинами устройства, первый вход блока управления инверсией соединен с обнаружителем ошибок кратности t + 1, первая и вторая группы выходов соединены с первыми входами первой и второй группы элементов И соответственно, выходы первой и второй групп элементов И соединены с первыми и вторыми входами группы элементов ИЛИ, выходы которых

соединены с входами локализатора ошибок кратности t и с вторыми входами корректора ошибок кратности t, причем выходы локализатора ошибок кратности t соединены с первыми входами регистра, вторые входы

которого соединены с выходами обнаружителя ошибок кратности t, а выходы регистра подключены к вторым входам блока управления инверсией, при этом вторые входы первой и второй групп элементов И соединены

с прямыми и инверсными входными шинами устройства соответственно.

Недостатком такого устройства является недостаточное быстродействие при исправлении двойных ошибок из-за больших задержек.

Целью изобретения является повышение быстродействия.

Для достижения поставленной цели устройство для исправления ошибок, содержашее корректор, блок обнаружения одиночной ошибки, блок обнаружения двойной ошибки, локализатор ошибки, элементы И, регистр, дешифраторы и элементы ИЛИ, причем вход устройства соединен с входом блока обнаружения двойной ошибки и со входом блока обнаружения одиночной ошибки, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом локализатора ошибки, выход первого элемента И соединен со входом регистра, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом блока обнаружения двойной ошибки, выход второго элемента И подключен ко входу первого дешифратора, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго дешифратора, выход элемента ИЛИ подключен к первому входу корректора, выход которого является выходом устройства, содержит сумматор по модулю два, при этом его первый вход подключен к выходу второго элемента И, второй вход сумматора по модулю два соединен с выходом локализатора ошибки, вход которого соединен с-входом устройствами со вторым входом корректора.

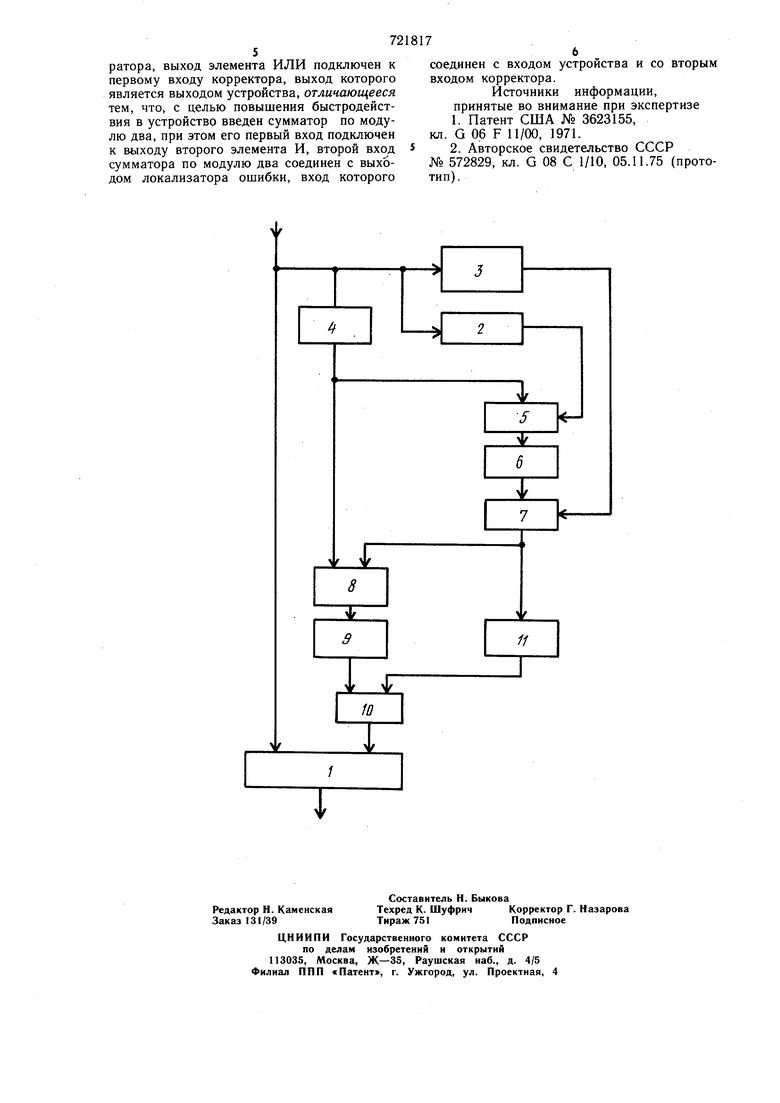

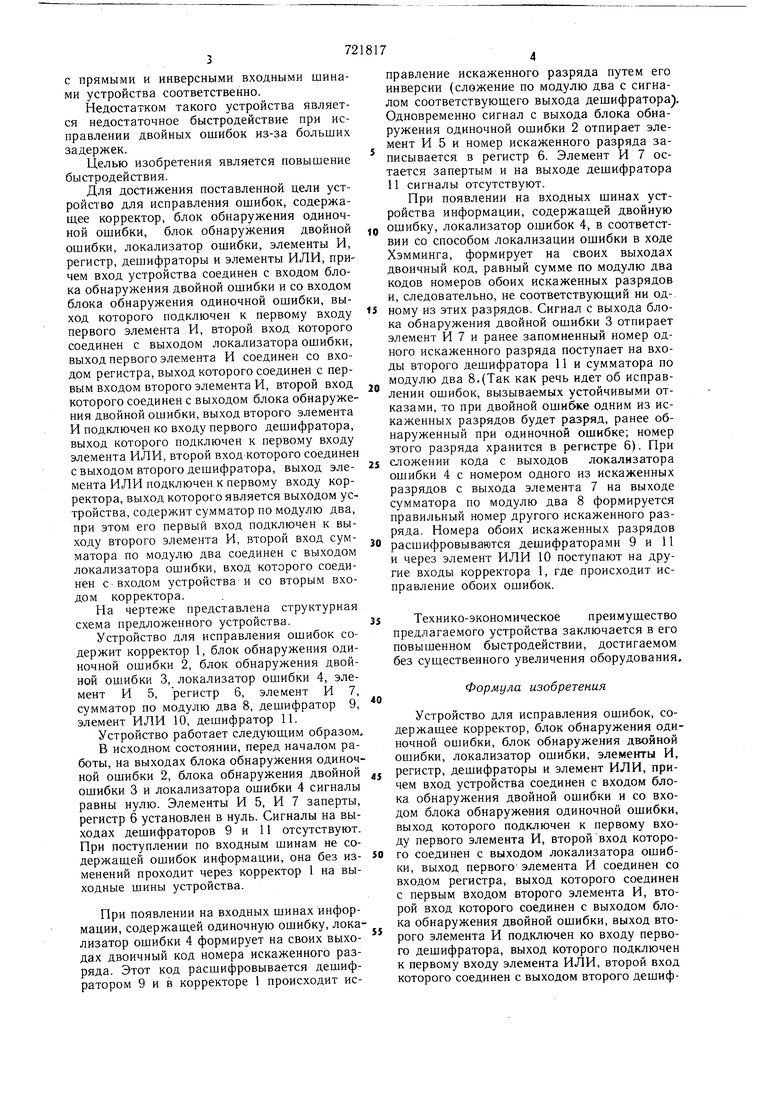

На чертеже представлена структурная схема предложенного устройства.

Устройство для исправления ошибок содержит корректор 1, блок обнаружения одиночной ошибки 2, блок обнаружения двойной ошибки 3, локализатор ошибки 4, элемент И 5, регистр 6, элемент И 7, сумматор по модулю два 8, дешифратор 9, элемент ИЛИ 10, дешифратор 11.

Устройство работает следуюш,им образом, В исходном состоянии, перед началом работы, на выходах блока обнаружения одиночной ошибки 2, блока обнаружения двойной ошибки 3 и локализатора ошибки 4 сигналы равны нулю. Элементы И 5, И 7 заперты, регистр 6 установлен в нуль. Сигналы на выходах дешифраторов 9 и 11 отсутствуют. При поступлении по входным шинам не содержашей ошибок информации, она без изменений проходит через корректор 1 на выходные шины устройства.

При появлении на входных шинах информации, содержаш,ей одиночную ошибку, локализатор ошибки 4 формирует на своих выходах двоичный код номера искаженного разряда. Этот код расшифровывается дешифратором 9 и в корректоре 1 происходит исправление искаженного разряда путем его инверсии (сложение по модулю два с сигналом соответствуюш,его выхода дешифратора). Одновременно сигнал с выхода блока обнаружения одиночной ошибки 2 отпирает элемент И 5 и номер искаженного разряда записывается в регистр 6. Элемент И 7 остается запертым и на выходе дешифратора 11 сигналы отсутствуют.

При появлении на входных шинах устройства информации, содержащей двойную ошибку, локализатор ошибок 4, в соответствии со способом локализации ошибки в ходе Хэмминга, формирует на своих выходах двоичный код, равный сумме по модулю два кодов номеров обоих искаженных разрядов и, следовательно, не соответствующий ни одному из этих разрядов. Сигнал с выхода блока обнаружения двойной ошибки 3 отпирает элемент И 7 и ранее запомненный номер одного искаженного разряда поступает на входы второго дешифратора 11 и сумматора по модулю два 8.(Так как речь идет об исправлении ошибок, вызываемых устойчивыми отказами, то при двойной ошибке одним из искаженных разрядов будет разряд, ранее обнаруженный при одиночной ошибке; номер этого разряда хранится в регистре 6). При сложении кода с выходов локализатора ошибки 4 с номером одного из искаженных разрядов с выхода элемента 7 на выходе сумматора по модулю два 8 формируется правильный номер другого искаженного разряда. Номера обоих искаженных разрядов расшифровываются дешифраторами 9 и 11 и через элемент ИЛИ 10 поступают на другие входы корректора 1, где происходит исправление обоих ошибок.

Технико-экономическое преимущество предлагаемого устройства заключается в его повышенном быстродействии, достигаемом без существенного увеличения оборудования,

Формула изобретения

Устройство для исправления ошибок, содержащее корректор, блок обнаружения одиночной ошибки, блок обнаружения двойной ошибки, локализатор ошибки, элементы И, регистр, дешифраторы и элемент ИЛИ, причем вход устройства соединен с входом блока обнаружения двойной ошибки и со входом блока обнаружения одиночной ошибки, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом локализатора ошибки, выход первого-элемента И соединен со входом регистра, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом блока обнаружения двойной ошибки, выход второго элемента И подключен ко входу первого дешифратора, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго дешиф

ратора, выход элемента ИЛИ подключен к первому входу корректора, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия в устройство введен сумматор по модулю два, при этом его первый вход подключен к выходу второго элемента И, второй вход сумматора по модулю два соединен с выходом локализатора ошибки, вход которого

W

соединен с входом устройства и со вторым входом корректора.

Источники информации, принятые во внимание при экспертизе

№ 572829, кл. G 08 С 1/10, 05.11.75 (прототип).

Авторы

Даты

1980-03-15—Публикация

1978-02-20—Подача