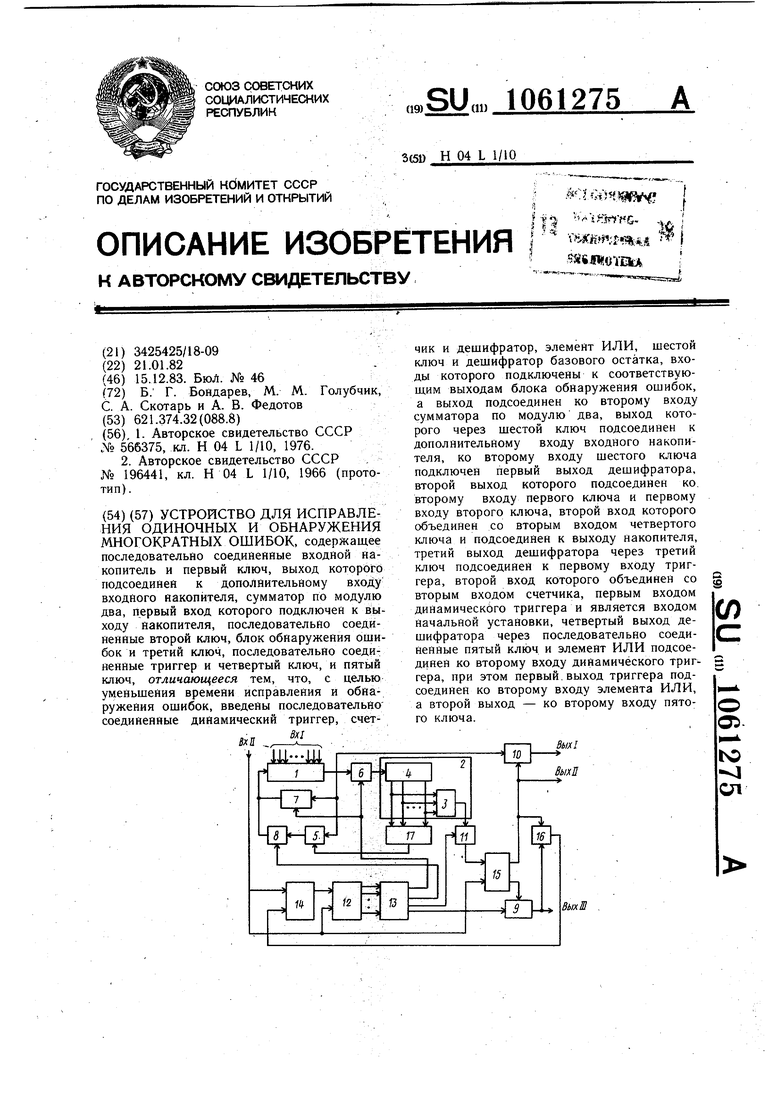

Изобретение относится к технике передачи данных и может использоваться в устройствах повышения достоверности информации. Известно устройство для исправления одиночных и обнаружения многократных ошибок, содержащее последовательно соединенные элемент ИЛИ, накопитель, сумматор но модулю два и блок обнаружения оишбок, выход которого подсоединен ко второму входу накопителя, первому входу и первому входу датчика одиночных ошибок, выход которого подсоединен ко второму входу сумматора по модулю два, выход которого подсоединен ко второму входу ключа, выход которого подсоединен к первому входу элемента ИЛИ, второй вход которого является входом устройства 1. Недостатком данного устройства для исправления одиночных и обнаружения многократных ошибок -является большое количество циклов для исправления одиночной ошибки. Наиболее близким к предлагаемому является устройство для исправления одиноч 1ых и обнаружения многократных ошибок, содержашее последовательно соединенные входной накопитель и первый ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соединенные триггер и четвертый ключ, и пятый ключ, вход которого подсоединен ко входу элемента запрета, а вы.чод подключен ко входу триггера и выходу элемента памяти, ко входу которого подк тючен выход третьего ключа, делитель, . выход которого подсоединен ко второму входу сумматора по модулю два, выход-которого подсоединен ко второму входу блока обнаружения ошибок и входу п-разрядного регистра, выход которого подсоединен ко второму входу четвертого ключа 2. Однако это устройство для исправления одиночных и обнаружения многократных ошибок характеризуется большим количеством циклов, равным п + 1, для исправления одиночной ошибки. Цель изобретения - уменьшение времени исправления и обйаружения ошибок. Поставленная цель достигается тем, что в устройство для исправления одиночных и обнаружения многократных ошибок, содержашее последовательно соединенные входной Накопитель и первый ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соединенные триггер и четвертый ключ, и пятый ключ, введены последовательно соединенные динамический триггер, счетчик и дешифратор, элемент ИЛИ, шестой ключ и дешифратор базового остатка, входы которого подключены к соответствуюшим выходам блока обнаружения ошибок, а выход подсоединен ко второму входу сумматора по модулю два, выход которого через шестой ключ подсоединен к дополнительному, входу входного накопителя, ко второму входу шестого ключа подключен первый выход дешифратора, второй выход которого подсоединен ко второму входу первого ключа и первому входу второго ключа, второй вход которого объединен со вторым входом четвертого ключа и подсоединен к вь1ходу накопителя, третий выход дешифратора через третий ключ подсоединен к первому входу триггера, второй вход которого объединен со вторым входом счетчика, первым входом динамического триггера и является вторым входом начальной установки, четвертый выход дешифратора через последовательно соединенные пятый ключ и элемент ИЛИ подсоединен ко второму входу динамического триггера, при этом первый выход триггера подсоединен ко второму входу элемента ИЛИ, а второй выход - ко второму входу пятого ключа. На чертеже представлена структурная электрическая схема устройства для исправления одиночных и обнаружения многократных ошибок. Устройство для исправления одиночных и обнаружения многократных ошибок содержит входной накопитель 1, блок 2 обнаружения ошибок, содержаший элемент ИЛИ-НЕ 3 и делитель 4, сумматор 5 по модулю два, ключи 6-11, счетчик 12, дешифратор 13, динамический триггер 14, триггер 15, элемент ИЛИ 16, дешифратор 17 базового остатка. Устройство для исправления одиночных и обнаружения многократных ошибок работает следуюшим образом. Со входа I принятая комбинация параллельным кодом записывается в накопитель 1. Одновременно на вход II поступает сигнал, по которому в исходное состояние устанавливается счетчик 12 и триггер 15 и запускается динамический триггер 14, вырабатываюший на своем выходе последовательность импульсов с частотой выше скорости телеграфирования в четыре раза. Счетчик 12 осушествляет подсчет импульсов, поступаюш,их на его вход, а дешифратор 13 выделяет четыре состояния счетчика 12, соответствующие четырем циклам работы устройства и .выдает управляющие сигналы на ключи 8, 6, 11, 9, 7. Процесс исправления одиночных и обнаружения ошибок большей кратности происходит на четыре цикла. В первом цикле сигналом от дешифратора 13 открыты ключи 6 и 7. Поэтому кодовая комбинация из накопителя 1 последовательным кодом

поступает в блок 2 обнаружения ошибок, где осуществляется делейие этой комбинации на образующий полином и одновременно вновь записывается через ключ 7 в накопитель 1.

Если в первом цикле деления ощибка 5 не обнаружена, то на выходе блока 2 обнаружения ощибки будет нулевой остаток, а на выходе элемента ИЛИ-НЕ 3 будет «1 При этом во втором цикле открывается ключ 11 и «1 с его выхода устанавливает Q триггер 15 в единичное состояние, при котором открывается ключ 10. Кодовая комбинация из Накопителя через открытый ключ 10 поступает на выход 1 устройства. Сигнал с выхода II может использоваться как команда «Разрещение ввода для счи- 15 тывания на входы очередной кодовой информации.

Если в первом цикле обнаружена ошибка, то на выходе элемента ИЛИ-НЕ 3 будет «О, при этом ключ 10 будет закрыт, а во втором цикле осуществляется 20 исправление одиночной ощибки.

Известно, что вид остатка от деления (синдрома) кодовой комбинации на образующий полином соответствует номеру ис-25 каженного разряда кодовой комбинации, одновременно после цикла деления происходят сдвиги синдрома. Это обстоятельство используется для исправления ошибки. Во втором цикле ключи 6 и 7 закрыты, а ключ 8 открыт. Перезапись в накопитель 1 осу- зо ществляется через сумматор 5 по модулю два. На второй вход сумматора 5 по модулю два подан выход дешифратора 17 базового остатка. Если одиночная ошибка произощла в i-OM разряде кодовой комбинации, то на i-OM такте, во втором цикле, 35 На выходе дешифратора 17 базового остатка появится единица, которая инвертирует искаженный символ кодовой комбинации.

в результате чего в накопитель 1 будет переписана исправленная комбинация.

В третьем цикле ключи 6 и 7 открыты, а остальные закрыты. Здесь происходит проверка наличия ошибки кратности более единицы в исправленной кодовой комбинации и одновременная ее перезапись в накопитель 1. Если ошибка не о0наружена, то на выходах блока 2 обнаружения ошибок будет Нулевой остаток, а на выходе ИЛИ-НЕ 3 появится «1, которая, как и в предыдущем случае, через открытый ключ 11 устанавливает в единичное состояние триггер 15, в результате чего ключ 10 открывается, и в четвертом цикле кодовая комбинация выводится на выход I устройства.

В-том случае, если имеет место ошибка кратности более единицы, то к Началу четBejpToro цикла блок 2 обнаружения ошибок выдает не нулевой остаток. Следовательно, ключ 10 оказывается закрыт и запрещает вывод комбинации на выход I.

Ключ 9 открыт, а так как на его вход поступает «1 с выхода триггера 15 (триггер находится в исходном состоянии), то на выходе III появляется сигнал «1, используемый как сигнал «Ошибка. Так как единичное состояние триггера 15 или «1 на выходе ключа 9 соответствует окончательному решению (наличие или отсутствие ошибки), то сигнал с выхода элеменна ИЛИ 16, поступаюший на установочный вход динамического триггера 14, останавливает последний до поступления следующей кодовой комбинации.

Технико-экономическая эффективность устройства для исправления одиночных и обнаружения многократных ощибок заключается в том, что оно позволяет в использования циклических кодов в раз уменьшить время анализа принятой кодовой комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления двойных и обнаружения многократных ошибок циклическими кодами | 1983 |

|

SU1185611A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1078655A2 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1115055A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1984 |

|

SU1202057A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1983 |

|

SU1162053A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для исправления ошибок | 1989 |

|

SU1750061A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1991 |

|

SU1830616A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1976 |

|

SU604170A2 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные входной накопитель и первый ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соеди-; ненные триггер и четвертый ключ, и пятый ключ, отличающееся тем, что, с целью уменьшения времени исправления и обнаружения ошибок, введены последовательно соединенные динамический триггер, счетиг/ чик и дешифратор, элемент ИЛИ, шестой ключ и дешифратор базового остатка, входы которого подключены к соответствуюш,им выходам блока обнаружения ошибок, а выход подсоединен ко второму входу сумматора по модулю два, выход которого через шестой ключ подсоединен к дополнительному входу входного накопителя, ко второму входу шестого ключа подключен первый выход дешифратора, второй выход которого подсоединен ко. второму входу первого ключа и первому входу второго ключа, второй вход которого объединен со вторым входом четвертого ключа и подсоединен к выходу накопителя, третий выход дешифратора через третий ключ подсоединен к первому входу триггера, второй вход которого объединен со вторым входом счетчика, первым входом динамического триггера и является входом начальной установки, четвертый выход дешифратора через последовательно соединенные пятый ключ и элемент ИЛИ подсоединен ко второму входу динамического триггера, при этом первый, выход триггера подсоединен ко второму входу элемента ИЛИ, а второй выход - ко второму входу пятого ключа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1976 |

|

SU566375A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОДИНОЧНЫХ и ОБНАРУЖЕНИЯ МЯОЮКРАТНЫХ ОШИБОК | 0 |

|

SU196441A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-12-15—Публикация

1982-01-21—Подача