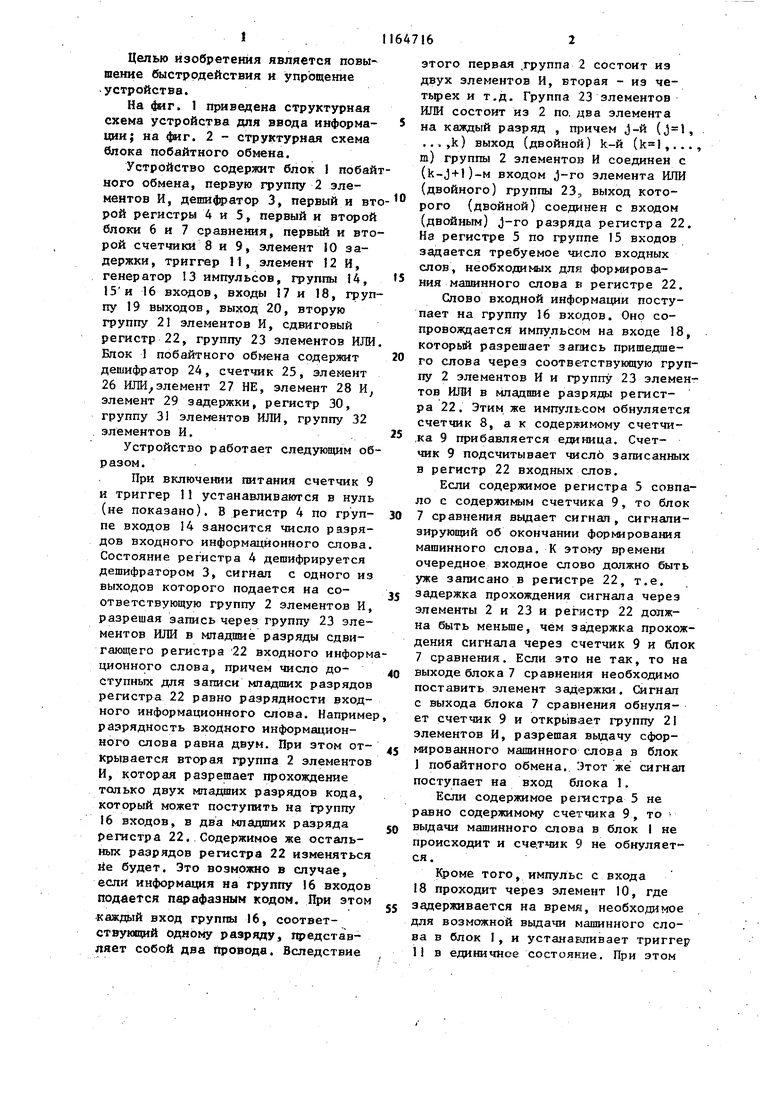

Целью изобретения является повы шение быстродействия и упрощение .устройства. На фиг. 1 приведена структурная схема устройства для ввода информации; на фиг. 2 - структурная схема блока побайтного обмена. Устройство содержит блок I побай ного обмена, первую группу 2 элементов И, дешифратор 3, первый и вт рой регистры 4 и 5, первый и второй блоки 6 и 7 сравнения, первый и вто рой счетчики 8 и 9, элемент 10 задержки, триггер 11, элемент 12 И, генератор 13 импульсов, группы 14, 15и 16 входов, входы 17 и 18, груп пу 19 выходов, выход 20, вторую группу 21 элементов И, сдвиговый регистр 22, группу 23 элементов ИШ Блок 1 побайтного обмена содержит дешифратор 24, счетчик 25, элемент 26 ИЛИ,элемент 27 НЕ, элемент 28 И элемент 29 задержки, регистр 30, группу 3 элементов ИЛИ, группу 32 элементов И, Устройство работает следующим об разом. При включении питания счетчик 9 и триггер 11 устанавливаются в нуль (не показано). В регистр 4 по группе входов 14 заносится число разрядов входного информационного слова Состояние регистра 4 дешифрируется дешифратором 3, сигнал с одного из выходов которого подается на соответствующую группу 2 элементов И разрешая запись через группу 23 элементов ИЖ в младшие разряды сдвигающего регистра 22 входного информ ционного слова, причем число доСтупных для записи кетадших разрядов регистра 22 равно разрядности входного информационного слова. Наприме разрядность входного информационного слова равна двум. При этом открывается вторая группа 2 элементов И, которая разрешает прохождение только двух младших разрядов кода, который может поступить на группу 16 входов, в два младших разряда регистра 22. Содержимое же остальных разрядов регистра 22 изменяться rie будет. Это возможно в случае, если информация на группу 16 входов подается парафаэным кодом. При этом каждый вход группы 16, соответствующий одному разряду, тфедставляет собой два провода. Вследствие этого первая .группа 2 состоит из двух элементов И, вторая - из четырех и т.д. Группа 23 элементов ИЛИ состоит из 2 по. два элемента на каждый разряд , причем J-й (, ...,k) выход (двойной) k-й (,..., m) группы 2 элементов И соединен с (k-J+l)-M входом J-ro элемента ИЛИ (двойного) группы 23,, выход которого (двойной) соединен с входом (двойным) j-ro разряда регистра 22. На регистре 5 по группе 15 входов задается требуемое число входных слов, необходимых для формирования малшнного слова II регистре 22. Слово входной информации поступает на группу 16 входов. Оно сопроволодается импульСом на входе 18, который разрешает запись пришедшего слова через соответствующую группу 2 элементов И и группу 23 элементов ИЛИ в младшие разряды регистра 22. Этим же импульсом обнуляется счетчик 8, а к содержимому счетчи,ка 9 прибавляется единица. Счетчик 9 подсчитывает число записанных в регистр 22 входных слов. Если содержимое регистра 5 совпало с содержимым счетчика 9, то блок 7 сравнения выдает сигнал , сигнализирующий об окончании формирования машинного слова. К этому времени очередное входное слово должно быть уже записано в регистре 22, т.е. задержка прохождения сигнала через элементы 2 и 23 и регистр 22 должна быть меньше, чем задержка прохождения сигнала через счетчик 9 и блок 7 сравнения. Если это не так, то на выходе блока 7 сравнения необходимо поставить элемент задержки. Сигнал с выхода блока 7 сравнения обнуляет счетчик 9 и открывает группу 2I элементов И, разрешая выдачу сформированного машинного слова в блок J побайтного обмена. Этот же сигнал поступает на вход блока 1. Если содержимое pejHCTpa 5 не равно содержимому счетчика 9, то выдачи машинного слова в блок I не происходит и сче.тчик 9 не обнуляется. Кроме того, импульс с входа 18 проходит через элемент 10, где задерживается на время, необходимое для возможной выдачи машинного слова в блок I , и устанан1ливает триггер П в единичное состояние. При этом

3

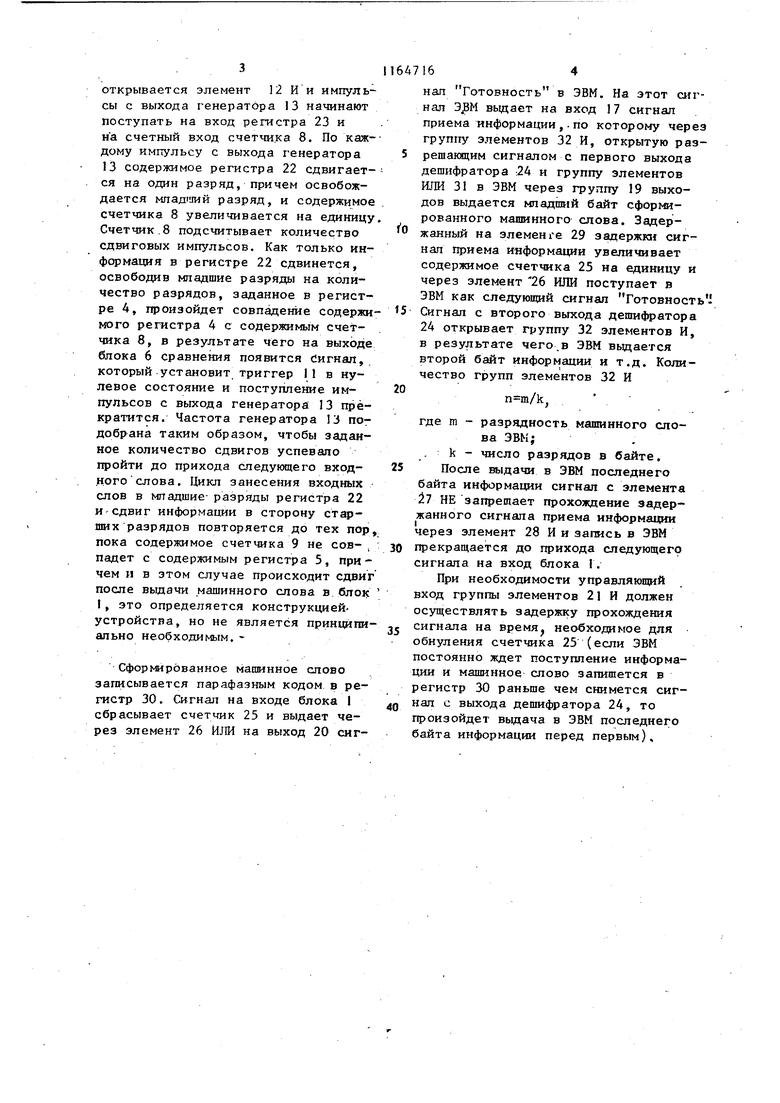

открывается элемент 12 И и импульсы с выхода генератора 13 начинают поступать на вход регистра 23 и на счетный вход счетчика 8. По каждому импульсу с выхода генератора 13 содержимое регистра 22 сдвигается на один разряд, причем освобождается мпадиий разряд, и содержимое счетчика 8 увеличивается на единицу Счетчик.8 подсчитывает количество сдвиговых импульсов. Как только информация в регистре 22 сдвинется, освободив младшие разряды на количество разрядов, заданное в регистре 4, произойдет совпадение содержимого регистра 4 с содержимым счетчака 8, в результате чего на выходе блока 6 сравнения появится Сигнал, который установит, триггер II в нулевое состояние и поступление импульсов с выхода генератора 13 прекратится. Частота генератора 13 подобрана таким образом, чтобы заданное количество сдвигов успевало пройти до прихода следующего входного слова. ГДикл занесения входных слов в младшие- разряды регистра 22 и-сдвиг информации в сторону старших разрядов повторяется до тех пор пока содержимое счетчика 9 не сов-, падет с содержимым регистра 5, причем я в зтом случае происходит сдвиг после вьщачи машинного слова в.блок I, это определяется конструкциейустройства, но не является принципиально необходимым. Сформированное машинное слово записывается парафазным кодом в регистр 30. Сигнал на входе блока 1 сбрасывает счетчик 25 и выдает через элемент 26 ИЛИ на выход 20 сиг47164

нал Готовность в ЭВМ. На этот сигнал выдает на вход 17 сигнал приема информации,.по которому через группу элементов 32 И, открытую раз5 решакщим сигналом с первого выхода дешифратора 54 и группу элементов ИЛИ 31 в ЭВМ через группу 19 выходов выдается младший байт сформированного машинного слова. Задер0 жанный на элементе 29 эадержю сигнал приема информации увеличивает содержимое счетчика 25 на единицу и через элемент 26 ИЛИ поступает в ЭВМ как следующий сигнал Готовность

5 Сигнал с второго выхода дешифратора 24 открывает группу 32 элементов И, в результате чего.в ЭВМ выдается второй байт информации и т.д. Количество групп элементов 32 И

,

где m - разрядность машинного слова ЭВМ; k - число разредов в байте.

5После 1дачи в ЭВМ последнего

байта информации сигнал с элемента 7 НЕ запрещает прохождение задержанного сигнала приема информации через элемент 28 И и запись в ЭВМ

0 прекращается до прихода следующего сигнала на вход блока I.

При необходимости управляющий вход группы элементов 21 И должен осуществлять задержку прохождения

сигнала на время необходимое для обнуления счетчика 25 (если ЭВМ постоянно ждет поступление информации и машинное слово запишется в регистр 30 раньше чем снимется сигQ нал с выхода дешифратора 24, то произойдет выдача в ЭВМ последнего байта информации перед первым).

/

I I 1 I

20

И t

- /;

IT

t f Оf

JT

Ir

,xx.

Д

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1975 |

|

SU551633A2 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

1. УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее блок побайтного обмена, дешифратор, первый и второй регистры, первый и второй блоки сравнения, первый и второй счетчики, элемент задержки, сдвиговый регистр, триггер, элемент И и генератор, импульсов, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом триггера, выход элемента И соединен с счетным входом первого счетчика и с первым входом сдвигового регистра, выходы группы блока побайтного обмена являются выходами группы устройства, выходы первого и второго счетчиков соединены соответственно с входами первой группы первого и второго блоков сравнения, выходы второй группы которых соединены с выходами первого и второго регистров соответственно, входы которых являются входами первой и второй групп устройства соответственно, выходы первого регистра соединены с входами дешифратора, первый вход и выход блока побайтного обмена являются соответственно первым входом и выходом устройства, установочный .вход перво.го счетчика является вторым входом устройства, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введены группа элементов ИЛИ, первая и вторая группы элементов И, выход первого блока сравнения соединен с нулевым входом триггера, единичный вход которого соединен с выходом элемента задержки, вход которого соединен с вторым входом сдвигового регистра, счетным входом второго счетчика и является вторым входом устройства, установоч(Л ный вход второго счетчика соединен с выходом второго блока сравнения, с вторым входом блока побайтного обмена и входами элементов И второй группы, входы группы которых соединены с выходами сдвигового регистра, входы группы которого соединены с выходами элементов ИЛИ группы, вхо2 si ды которых соединены с выходами элементов ИЛИ группы, входы которьпс соединены с выходами дешифратора, входы группы элементов И первой группы являются входами третьей группы устройства, выходы элементов И второй группы соединены с входами группы блока побайтного обмена. Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки экспериментальной информации.

UJ

/

/4

5

Ж

о:

JE

LI:

JL

ixJ

ЛЕ

Ч

(Puf2

| Устройство для обработки и ввода экспериментальных данных в вычислительные машины | 1974 |

|

SU520581A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1975 |

|

SU551633A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-30—Публикация

1983-11-02—Подача