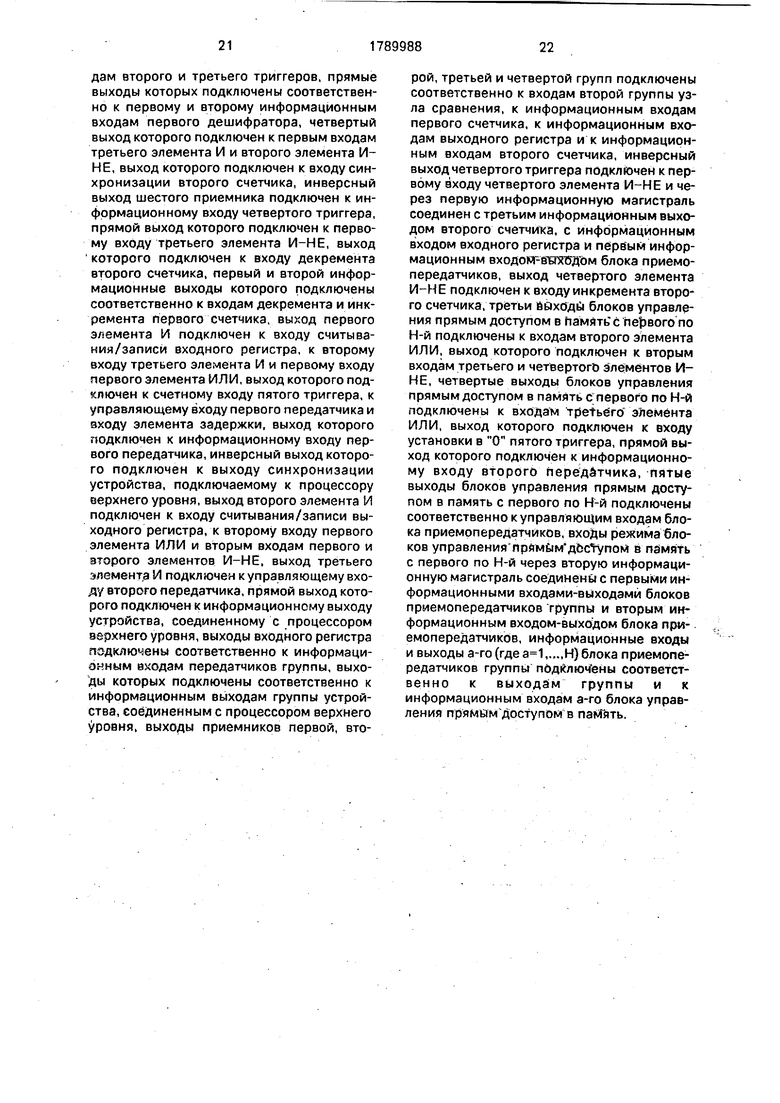

Изобретение относится к вычислительной технике и может быть использовано для организации мультипроцессорной иерархической вычислительной системы.

Известно устройство для организации мультипроцессорной системы, содержащее регистра управления, два регистра данных, два регистра направления и два контрольных регистра, образующие два канала ввода-вывода, позволяет организовать мультипроцессорную систему.Недостатком устройства является ограниченная область применения - только для управления двумя каналами внешних устройств и низкая скорость обмена.

Известно устройство для организации мультипроцессорной системы, содержащее

регистр команд vf состояний, регистр данных, приемники, адресный компаратор, регистр адреса, вентили, два коммутатора, приемопередатчики, четыре триггера, два сдвиговых регистра, генератор импульсов и постоянное запоминающее устройство, по- зволяеторганизовать мультйпроцессорную иерархическую систему.

Недостатком устройства являются боль- uftie аппаратные затраты и низкая скорость обмена информацией.

Известно устройство для организации мультипроцессорной иерархической системы, содержащее дешифратор управляющих сигналов, входной регистр, регистр адреса, блок приемопередатчиков верхнего уровня, триггеры, логические элементы И, ИЛИ,

3 ч о

00

00

коммутатор, постоянное запоминающее устройство и Nfe блоков управления прямым доступом в память, позволяет организовать мультипроцессорную иерархическую систему,

Недостатком устройства являются большие аппаратные затраты и низкая скорость обмена информацией,

Наиболее .(близким по технической сущности к заявляемому устройству является выбранкбе в Шёстве прототипа устройство для ррт-ани#а Ц0&т мультипроцессорной иерархической системы, содержащее дешифратор управляющих сигналов, входной регистр, Kfe блоков управления прямым доступом в память, регистр адреса, блок приемопередатчиков верхнего уровня, регистр управления, дешифратор выбора, блок внутренних приемопередатчиков, выходной регистр и блоки приемопередатчиков нижнего уровня, причем первые информационные входы-выходы входного регистра и регистра адреса подключены к первому информационному входу-выходу блока приемопередатчиков верхнего уровня и к входу дешифратора управляющих сигналов, первый и второй выходы которого подключены к сийхровхоДам йхбдйого регистра и регистра адреса соответственно, второй информационный вход-выход блока приемопередатчиков верхнего уровня является вхбдом-выходом верхнего уровня устройства, третий и четвертый выходы дешифратора управляющих сигналов подключены к синхро входам выходного регистрам регистра управления соответственно, первые информационные входы-выходы которых подключены к первому информационному входу-выходу блока приемопередатчиков верхнего уровня, вторые информационные входы-выходы входного регистра, выходного регистра и регистра адреса подключены к первому информационному входу-выходу блока внутренних приемопередатчиков, второй информационный вход-выход которого подкл ючен к первым информационным входам-выходам блоков приемопередатчиков нижнего уровня, вторые информационные входы-выходы которых являются соответствующими входами-выходами нижнего уровня устройства, выход регистра управления подключен к входу дешифратора выбора, первый выход которого подключен к входам выбора направления обмена блоков управления прямым доступом в память, вход пуска 1-го (, N), блока управления прямы.м доступом в память подключен к J-му (, N+1) выходу дешифратора выбора, выходы окончания цикла блоков управления прямым доступом в память подключены к

0

5

0

5

0

5

0

5

0

5

входу сброса регистра управления, выходы Адрес-данные блоков управления прямым доступом в память подключены к входу Адрес-данные блока внутренних приемопередатчиков, выходы управления выдачей информации блоков управления прямым доступом в память подключены к входам управления выдачей информации соответствующих блоков приемопередатчиков нижнего уровня, выходы управляющих слов обмена блоков управления прямым до- ступом в память подключены к входам управления режимом прямого доступа соответствующих блоков приемопередатчиков нижнего уровня, Недостатком устройства является ограниченное количество подключаемых ЭВМ нижнего уровня и низкая скорость обмена массивами информации,

В прототипе количество подключаемых ЭВМ нижнего уровня ограничено из-за конечной нагрузочной способности внутренней магистрали, а скорость обмена является низкой за счет выполнения множества команд при выполнении операций обмена массивами информацией.

Цель изобретения: расширение количества подключаемых ЭВМ нижнего уровня за счет организации адресации групп каналов для связи с ЭВМ верхнего уровня; повышение скорости обмена массивами информа- ций за счет сокращения множества команд при выполнении операций обмена между ЭВМ верхнего и нижнего уровня.

Поставленная цель достигается тем, что в известное устройство, содержащее дешифратор управляющих сигналов, входной регистр, N блоков управления, дешифратор выбора, блок внутренних приемопередатчиков, выходной регистр и блоки приемопередатчиков нижнего уровня/причем первый и второй выход дешифратора управляющих сигналов подключены соответственно к входам выборки входного и выходного регистра, информационные входы входного регистра и информационные выходы выходного регистра подключены к первому информационному входу-выходу блока внут ёйнйх приемопередатчиков, второй информационный вход-выход которого подключен к первым информационным входам- выходам блоков приемопередатчиков нижнего уровня, вторые информационные входы-выходы которых являются соответствующими входами-выходами нижнего уровня устройства, вход пуска 1-го (, N) блока управления прямым доступом в память подключён к i-му выходу дешифратора выбора, первый и второй выходы управления выдачей информации блоков управления прямым доступом в память подключены к первому и второму входам управления выдачей информации соответствующих блоков приемопередатчиков нижнего уровня, и образующее группу каналов для связи ЭВМ верхнего уровня с N ЭВМ нижнего уровня, введены (М-1) таких групп, причем в каждую из М групп введены два передатчика, шесть приемников, четыре группы приемников, группа передатчиков, элемент задержки, элемент сравнения, два счетчика, пять триггеров, три элемента И, четыре элемента И- НЕ, три элемента ИЛИ, при этом в каждом из М групп каналов, выход передатчика подключен к синхро-входу ЭВМ верхнего уровня, входы первого, второго и третьего приемников подключены к выходам ввода, вывода и синхронизации ЭВМ верхнего уровня соответственно, группа входов первой группы приемников подключены к группе старших разрядов адресного выхода ЭВМ верхнего уровня, младшие разряды адресного выхода которой подключены ко входам четвертого и пятого приемника соответственно, входы второй и четвертой групп приемников и выходы группы передатчиков подключены к группе информационных входов-выходов ЭВМ верхнего уровня, младший разряд которой подключен к входу шестого приемника, входы третьей группы приемников подключены к адресным выходам ЭВМ верхнего уровня, первый вход передатчика соединен с выходом элемента задержки, вход которого соединен с вторым входом передатчика и с выходом первого элемента ИЛИ, первый вход которого соединен с входом управления записью входного регистра, с вторым входом третьего элемента И и с выходом первого элемента И, первый вход которого соединен с выходом первого приемника, второй вход первого элемента ИЛИ соединен с входом управления записью выходного регистра, с выходом второго элемента И и с первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены с третьим и четвертым выходами дешифратора управляющих сигналов, информационные входы которого соединены с выходами первого и второго триггеров, входы синхронизации которых соединены с входом синхронизации третьего триггера и с выходом третьего приемника, выход второго приемника соединен с первым входом второго элемента И, второй вход которого соединен с вторым входом первого элемента И и с прямым выходом третьего триггера, инверсный выход которого соединен с входом выборки дешифратора управляющих сигналов, информационный вход третьего

триггера соединен с выходом элемента сравнения, первая группа входов которого, соединена с выходами первой группы приемников, вторая группа входов элемента 5 сравнения является входами установки номера группы каналов устройства, информационные входы первого и второго триггеров соединены с выходами четвертого и пятого приемников, выход первого элемента И-НБ

0 соединен с входами синхронизации счетчика управления и четвертого триггера, информационный вход которого соединен с выходом шестого приемника, выход второго элемента И-НЕ соединен с входом синхро5 низации счетчика адреса, информационные входы которого соединены с выходами приемников третьей группы, информационные входы дешифратора выбора соединены с информационными выходами счетчика уп0 равления, информационные входы которого соединены с выходами приемников второй группы, входы увеличения и уменьшения счетчика управления соединены с выходами прямого и обратного переноса счетчика ад5 реса, группа информационных выходов которого соединены с первыми информационными входами-выходами блока внутренних приемопередатчиков, первый вход третьего элемента И-НЕ соединен

0 с прямым выходом четвертого триггера и через передатчик блока внутренних приемопередатчиков с входами выбора режима № блоков управления, инверсный выход четвертого триггера соединен с первым вхо5 дом четвертого элемента И-НЕ, второй вход которого соединен с вторым входом третьего элемента И-НЕ и с выходом второго элемента ИЛИ, входы которого соединены с первыми выходами управления № блоков

0 управления соответственно, входы управления блока внутренних приемопередатчиков соединены с вторыми выходами управления № блоков управления, группы информационных входов и выходов которых соединены

5 с группами информационных выходов и входов соответствующих блоков приемопередатчиков нижнего уровня, выходы приемников четвертой группы соединены с .информационными входами выходного ре0 ,гистра, информационные выходы входного регистра соединены с входами группы передатчиков, выход второго передатчика подключен к младшему разряду в группе информационных входов-выходов ЭВМ

5 верхнего уровня, первый вход второго передатчика подключен к выходу третьего элемента И, первый вход которого соединен с четвертым выходом дешифратора управляющих сигналов, второй вход второго передатчика соединен с выходом пятого

триггера, вход синхронизации которого соединен с выходом первого элемента ИЛИ, вход установки в ноль пятого триггера соединен с выходом.третьего элемента ИЛИ, входы которого соединены с третьими выходами управления Ms блоков управления прямым доступом к памяти, выходы третьего и четвертого элементов И-НЕ соединены с входами увеличения и уменьшения счетчика адреса соответственно,.

Сопоставительный анализ с прототипом позволяет сделать вывод, что заявляемое устройство отличается наличием (М-1) групп каналов для связи ЭВМ верхнего уровня с N ЭВМ нижнего уровня и наличием в каждой группе двух передатчиков, шести приемников, четырех групп приемников, группы передатчиков, элемента задержки, элемента сравнения, двух счетчиков, пяти триггеров, трех элементов И, четырех элементов И-НЕ, трех элементов ИЛИ и новой организацией связей.

Таким образом, заявляемое устройство соответствует критерию изобретения новизна.

Устройство обладает существенными отличиями, так как содержит новую совокупность признаков, которая придает ему новые свойства , заключающиеся в увеличении количества подключаемых ЭВМ нижнего уровня и в повышении скорости обмена массивами информации, за счет организации адресации групп каналов и сокращения множества команд при выполнении операций обмена массива информации между ЭВМ. .

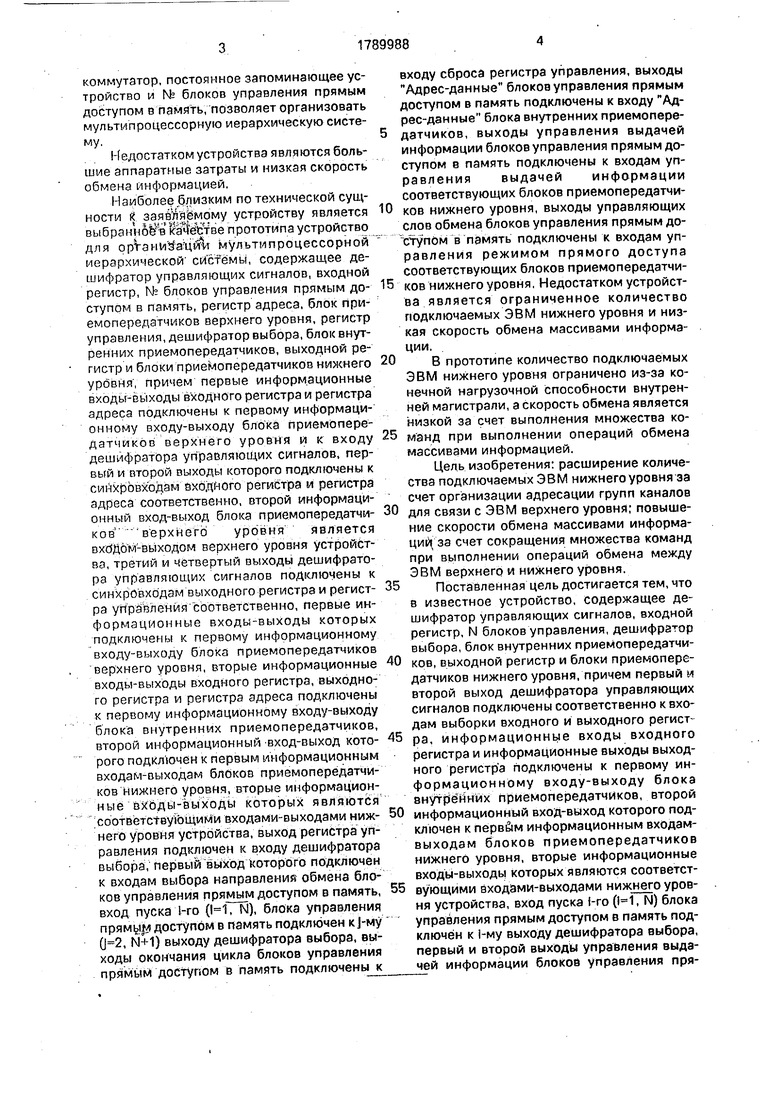

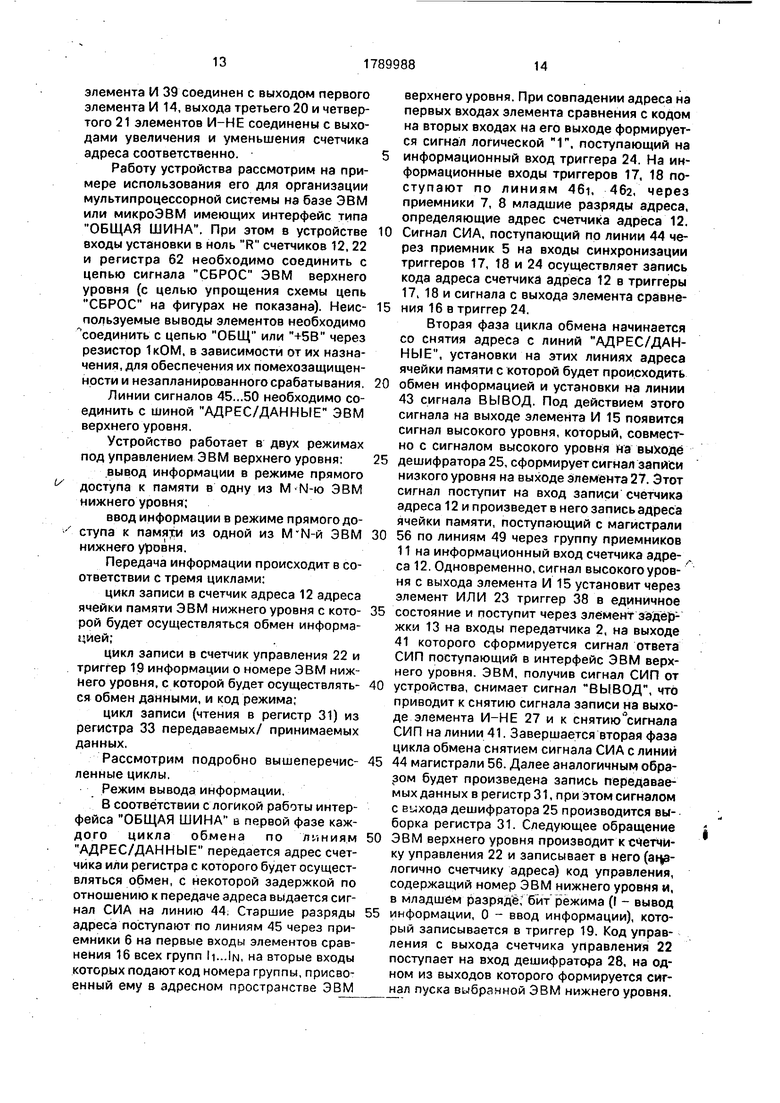

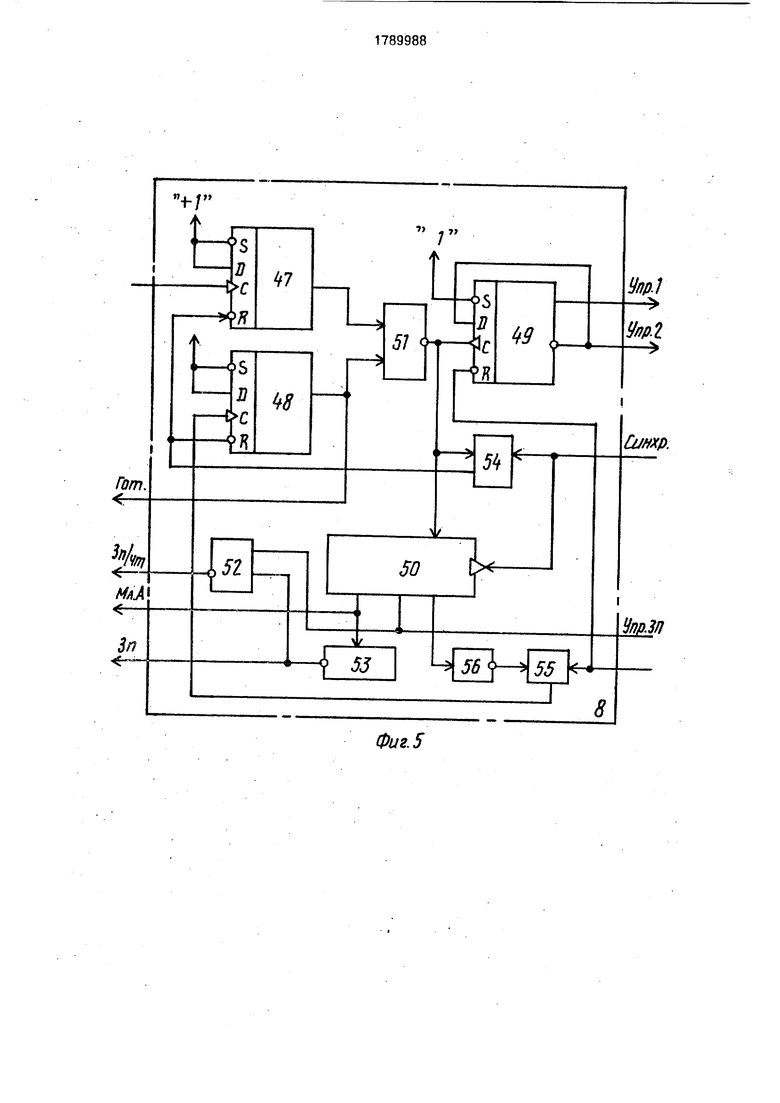

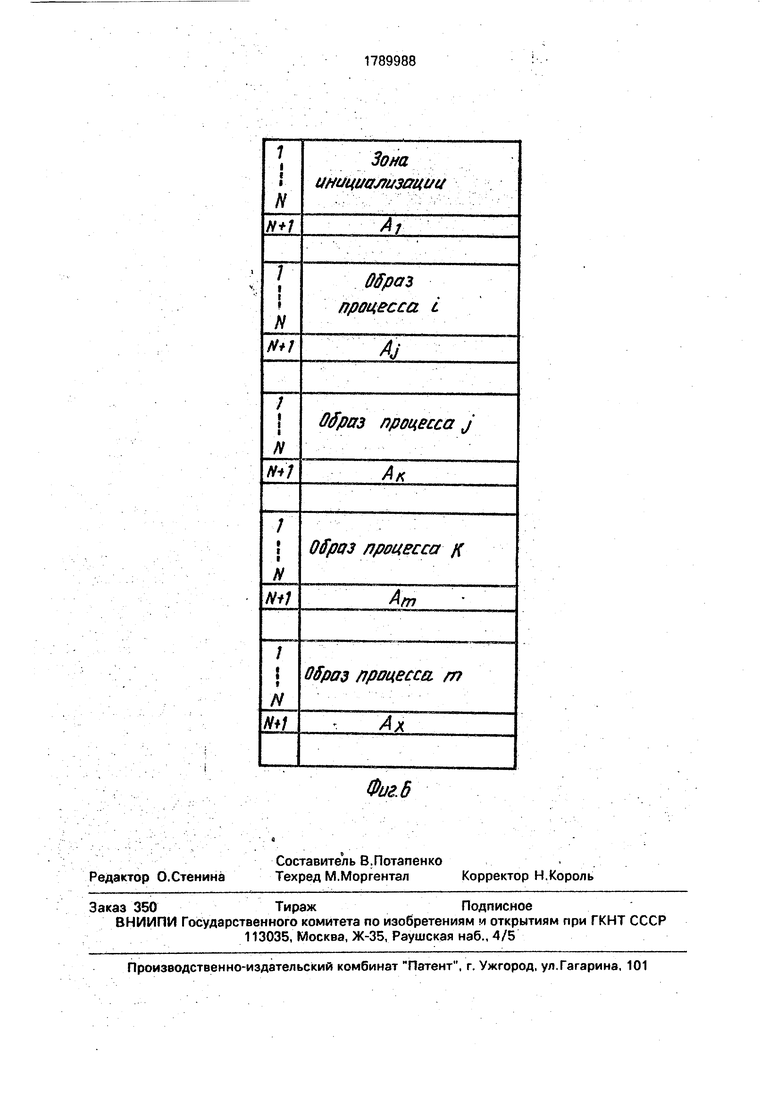

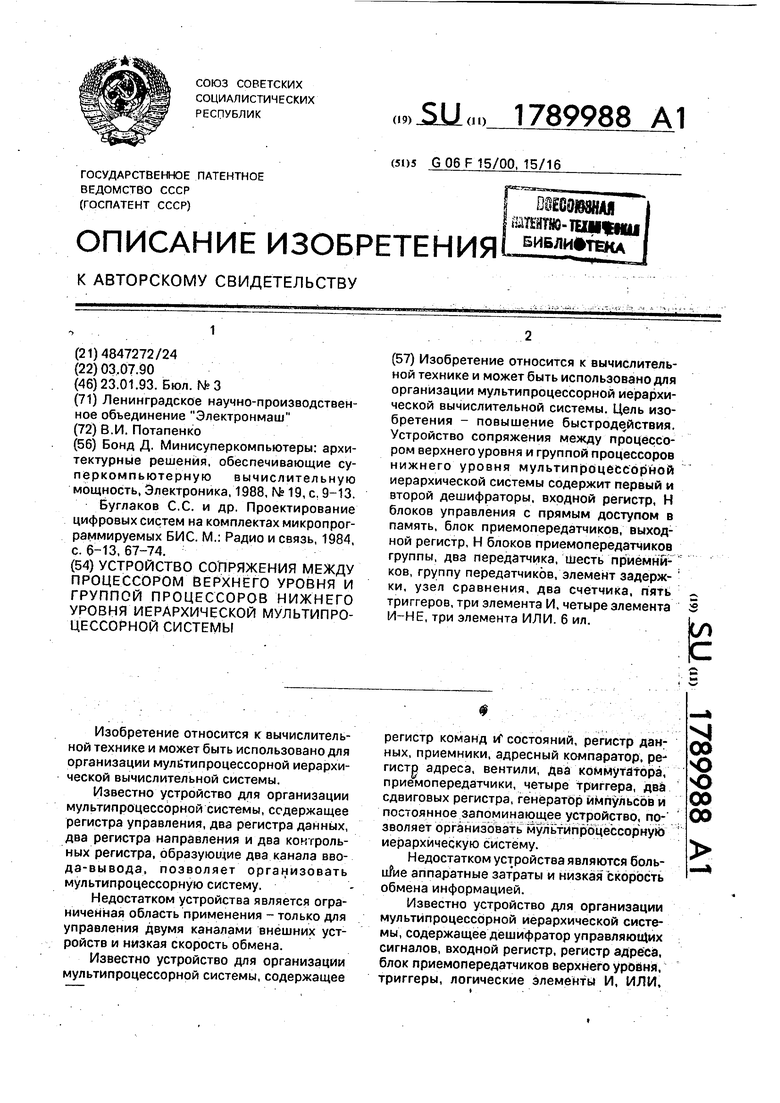

На фиг. 1 приведена структурная схема группы каналов для связи ЭВМ верхнего уровня с N ЭВМ нижнего уровня; на фиг. 2

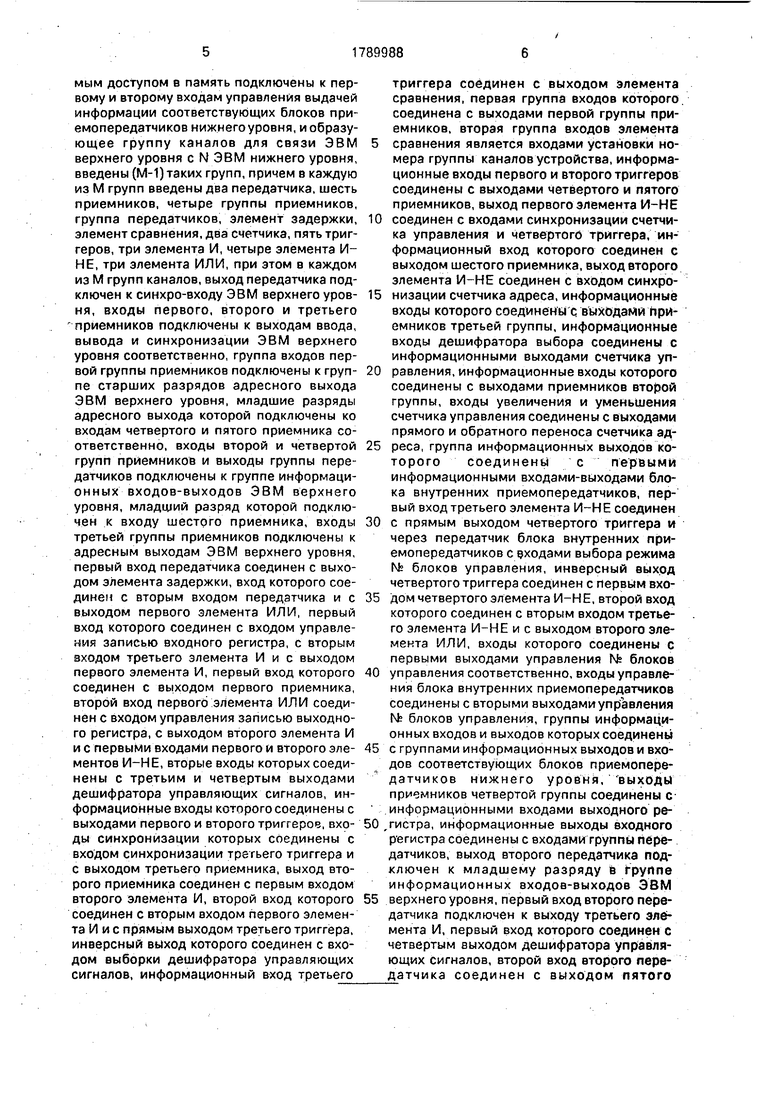

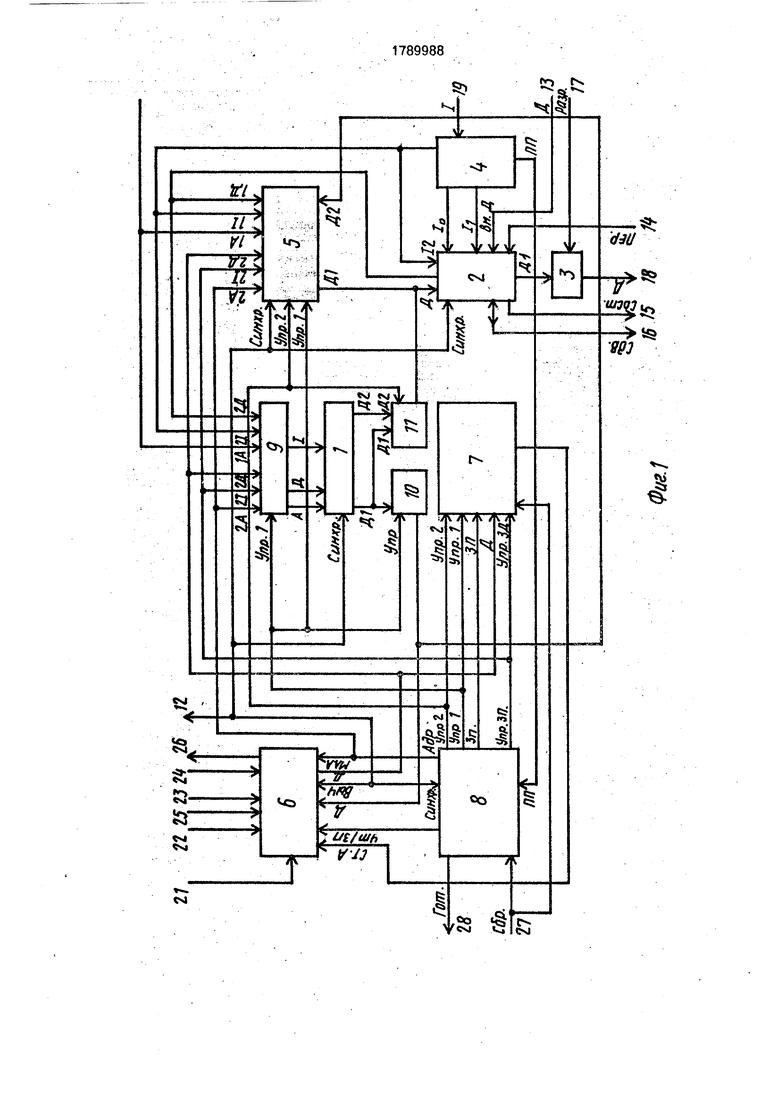

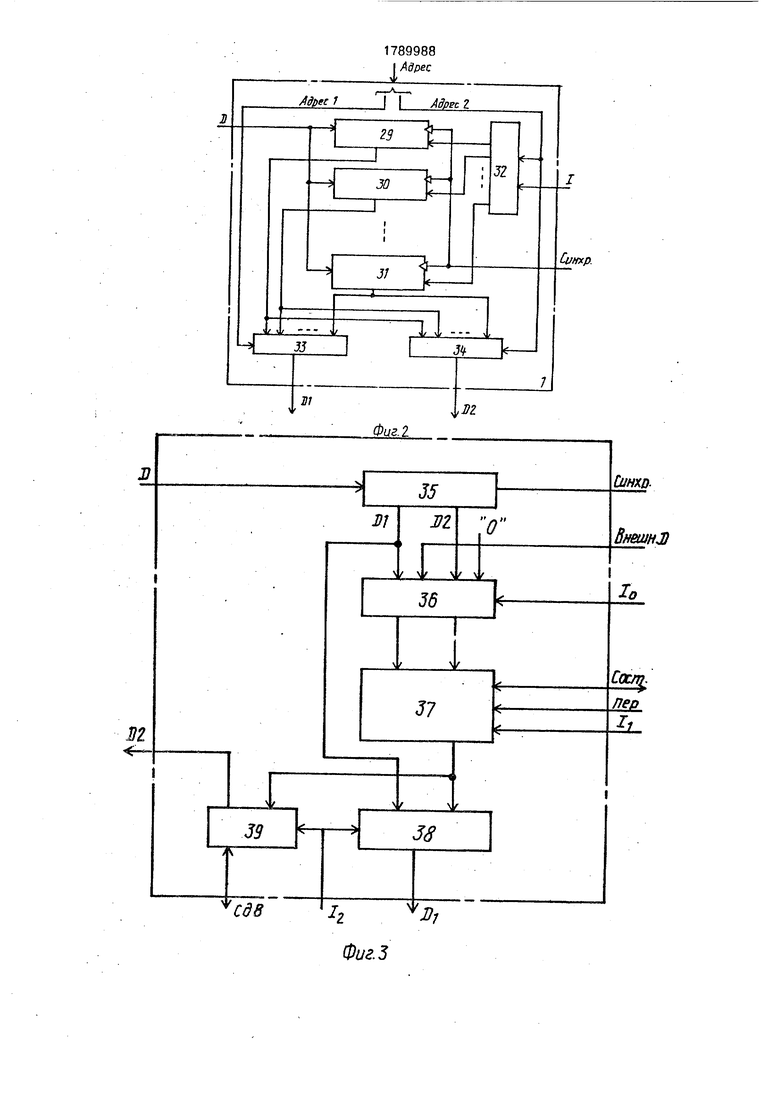

-структурная схема устройства, состоящего из М групп каналов для связи ЭВМ верхнего уровня с N M ЭВМ нижнего уровня; на фиг. 3 - пример реализации блока управления; на фиг, 4 - пример реализации блока при- емопереДатчиков нижнего уровня; на фиг, 5

- пример реализации блока внутренних приемопередатчиков; на фиг. 6 - временные соотношения операций обмена массивами информацией прототипа и заявляемого устройства.

На фиг, 1 позицией 1 обозначена группа каналов для связи ЭВМ верхнего уровня с N ЭВМ нижнёго уровня; 2 - передатчик (например 559МП1); 3, 4, 5 - первый, второй и третий приемники (например 559ИП2); 6 - первая группа приемников; 7,8 - четвертый и пятый приемники; 9 - вторая группа приемников; 10 - шестой приемник; 11 - третья группа приемников; 12 - первый счетчик, например ИЕ7 серии 155,555 или аналогичный; 13 - элемент задержки реализованный на навесных элементах (конденсатор, резистор, диод или набор элементов НЕ; 14, 15

- первый и второй элементы И, например ЛИ1, ЛИЗ серии К155, К555 или аналогичный; 16 - узел сравнения, например 53 ОСП 1 или аналогичный; 17, 18 - первый и второй триггеры, например ТМ2, ТМ5 серии Kl55, К555; 19-четвертый триггер; 20,21 -третий 0 и четвертый элемент И-НЕ, например ЛАЗ, ЛА4 серии К155, К555 или аналогичный; 22

- второй счетчик; 23 - первый элемент ИЛИ например ЛЛ1 серии К155, К555 или аналогичный; 24 - третий триггер; 25 - первый

5 дешифратор, например ИД4 серии К155, К555 или аналогичный; 26, 27 - первый и второй элемент и-НЕ; 28 - второй дешифратор, например ИДЗ серии К155, К555 или аналогичный; 29 - второй элемент ИЛИ; 30

0 -третья группа приемников; 31 - выходной регистр, например К589ИР12 или аналогичный; 32 - группа передатчиков; 33 - входной регистр, например К589ИР12 или аналогичный; 34 - блок приемопередатчиков;

5 З51...35м - блоки приемопередатчиков группы; Зб1,..36ы - блоки управления прямым доступом в память; 37 - второй передатчик; 38 - пятый триггер; 39 - третий элемент И; 40 - третий элемент ИЛИ: 41 - линия сигна0 ла СИП; 42 - линия сигнала ВВОД; 43 - линия сигнала ВЫВОД; 44 - линия сигнала СИА; 45 - группа линий старших разрядов сигналов АДРЕС; 46 - группа линий младших разрядов сигналов АДРЕС; 47 - группа

5 линий сигналов ДАННЫЕ ВХ.; 48 - линия младшего разряда сигналов ДАННЫЕ ВХ.; 49 - группа линий сигналов АДРЕС; 50 - группа линий сигналов ДАННЫЕ ВЫХ.; 51- линия сигнала РЕЖИМ; 52 - группа линий

0 сигналов ДАННЫЕ ЭП.; 53 - группа линий сигналов ДАННЫЕ ЧТ.; 54 - линия сигнала разрешения обмена; 55 - линия сигнала направление обмена; 56 - магистраль для связи с ЭВМ верхнего уровня; 57 - первая

5 внутренняя магистраль; 58 - вторая внутренняя магистраль; 59 - группа линий установки номера (адреса) группы каналов; 60- группа линий сигналов 61 - группа линий сигналов КОНЕЦ ЦИКЛА ; 62 - груп0 па линий сигналов АДРЕС ЯЧЕЙКИ ; 63 - группа линий сигналов УПРАВЛЕНИЕ ОБМЕНОМ ; 64 - группа линий сигналов ПУСК.

На фиг. 3 позицией 65 обозначен муль5 типлексор, например КП1 или КП5 серии К155 или аналогичный; 66 - генератор импульсов реализованный на базе элементов серии К155 или аналогичной; 67 - регистр; 68 - постоянное запоминающее устройство, например РЕЗ серии К155 или аналогичное.

На фиг, 4 позицией 69 обозначен первый элемент НЕ; 70 - группа шинных формирователей, например К589АП16 или К589АП26, 71 - передатчик; 72 - приемник; 73 - элементы НЕ; 74, 75 - элементы И; 76 - группа передатчиков; 77 - группа приемников.

На фиг. 5 позицией 78 и 79 обозначены группы передатчиков; 80 - передатчик; 81 - группа приемников; 82 - элемент ИЛИ; 83 - элемент НЕ.

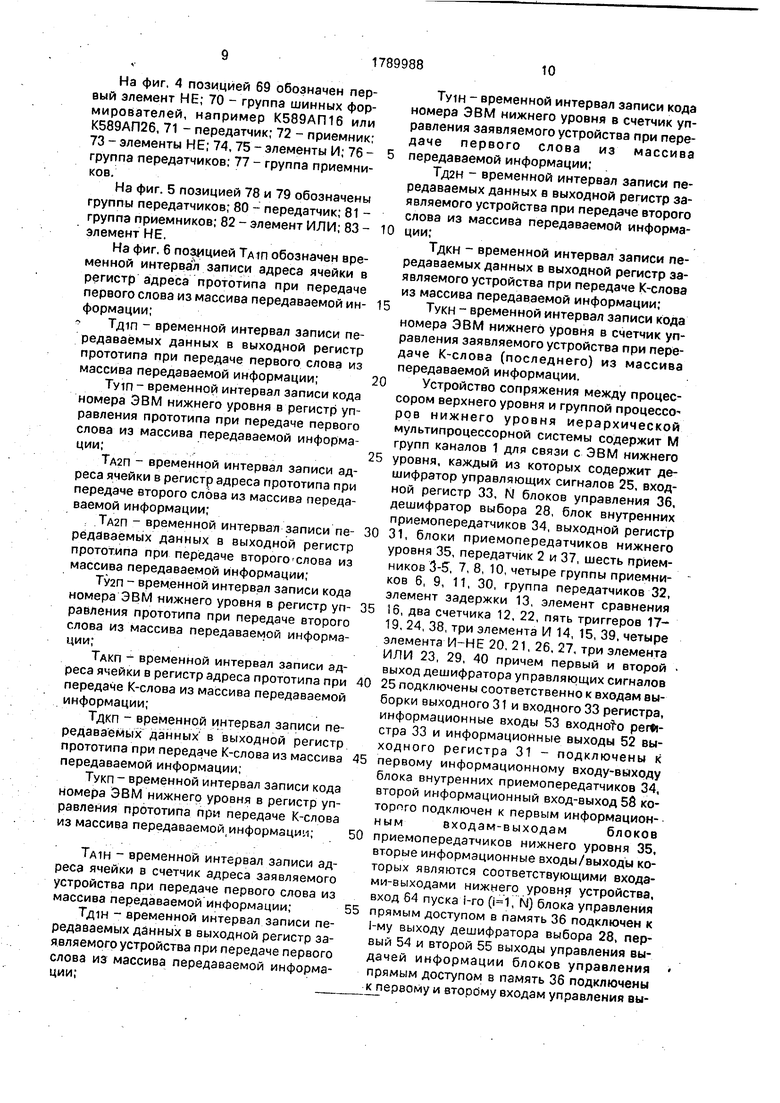

На фиг. 6 позицией ТА in обозначен временной интервал записи адреса ячейки в регистр адреса прототипа при передаче первого слова из массива передаваемой информации;

Тд1п - временной интервал записи передаваемых данных в выходной регистр прототипа при передаче первого слова из массива передаваемой информации;

Tyin - временной интервал записи кода номера ЭВМ нижнего уровня в регистр управления прототипа при передаче первого слова из массива передаваемой информации;

Тд2П - временной интервал записи адреса ячейки в регистр адреса прототипа при передаче второго слова из массива передаваемой информации;

Тдгп - временной интервал записи передаваемых данных в выходной регистр прототипа при передаче второго слова из массива передаваемой информации;

Туап - врем.енной интервал записи кода номера ЭВМ нижнего уровня в регистр управления прототипа при передаче второго слова из массива передаваемой информации;

Тдкп - временной интервал записи адреса ячейки в регистр адреса прототипа при передаче К-слова из массива передаваемой информации;

Тдкп - временной интервал записи передаваемых данных в выходной регистр прототипа при передаче К-слова из массива передаваемой информации;

Тукп - временной интервал записи кода номера ЭВМ нижнего уровня в регистр управления прототипа при передаче К-слова из массива передаваемойгинформации;

TAIH - временной интервал записи адреса ячейки в счетчик адреса заявляемого устройства при передаче первого слова из массива передаваемой информации;

Тдж - временной интервал записи передаваемых данных в выходной регистр заявляем ого устройства при передаче первого слова из массива передаваемой информации;

Туш - временной интервал записи кода номера ЭВМ нижнего уровня в счетчик управления заявляемого устройства при передаче первого слова из массива 5 передаваемой информации;

Тден - временной интервал записи передаваемых данных в выходной регистр заявляемого устройства при передаче второго слова из массива передаваемой информа0 ции;

Тдкн - временной интервал записи передаваемых данных в выходной регистр заявляемого устройства при передаче К-слова из массива передаваемой информации;

5 Туки - временной интервал записи кода номера ЭВМ нижнего уровня в счетчик управления заявляемого устройства при передаче К-слова (последнего) из массива передаваемой информации.

0 Устройство сопряжения между процессором верхнего уровня и группой процессе ров нижнего уровня иерархической мультипроцессорной системы содержит М групп каналов 1 для связи с ЭВМ нижнего

5 уровня, каждый из которых содержит дешифратор управляющих сигналов 25, входной регистр 33, N блоков управления 36, дешифратор выбора 28, блок внутренних приемопередатчиков 34, выходной регистр

0 31, блоки приемопередатчиков нижнего уровня 35, передатчик 2 и 37, шесть приемников 3-5, 7, 8, 10, четыре группы приемников 6, 9, 11, 30, группа передатчиков 32, элемент задержки 13, элемент сравнения

5 16, два счетчика 12, 22, пять триггеров IT- 19, 24, 38, три элемента И 14, 15, 39, четыре элемента И-НЕ 20, 21, 26, 27, три элемента ИЛИ 23, 29, 40 причем первый и второй выход дешифратора управляющих сигналов

0 25 подключены соответственно к входам выборки выходного 31 и входного 33 регистра, информационные входы 53 входного регистра 33 и информационные выходы 52 выходного регистра 31 - подключены к

5 первому информационному входу-выходу блока внутренних приемопередатчиков 34, второй информационный вход-выход 58 которого подключен к первым информацион- нымвходам-выходам блоков

0 приемопередатчиков нижнего уровня 35, вторые информационные входы/выходы которых являются соответствующими входами-выходами нижнего уровня устройства, вход 64 пуска i-го (, N) блока управления

5 прямым доступом в память 36 подключен к 1-му выходу дешифратора выбора 28, первый 54 и второй 55 выходы управления выдачей информации блоков управления прямым доступом в память 36 подключены к первому и вторбму входам управления выдачей информации соответствующих блоков приемопередатчиков нижнего уровня 35, выход 41 передатчика 2 подключен к синхровходу ЭВМ верхнего уровня, входы 42, 43, 44 первого 3, второго 4 и третьего 5 приемников подключены к выходам ввода, вывода и синхронизации ЭВМ верхнего уровня соответственно, труппа входов 45 первой группы приемников 6 подключены к группе старших разрядов адресного выхода ЭВМ верхнего уровня, младшие разряды адресного выхода которой подключены ко входам 46i, 462, четвертого 7 и пятого 8 приемника соответственно, входы 47 второй 9 и четвертой 30 групп приемников и выходы 50 группы передатчиков 32 подключены к группе информационных входов-выходов ЭВМ верхнего уровня, младший разряд 48 которой подключен к входу шестого приемника 10, входы 49 третьей группы приемников 11 подключены к адресным выходам ЭВМ верхнего уровня, первый вход передатчика 2 соединен с выходом элемента задержки 13, вход которого соединен с вторым входом передатчика 2 и с выходом первого элемента ИЛИ 23, первый вход которого-соединен с входом управления записью входного регистра 33 и с выходом первого элемента И 14, первый вход которого соединен с выходом первого приемника 3, второй вход первого элемента ИЛИ 23 соединен с входом управления записью выходного регистра 31, с выходом второго элемента И 15 и с первыми входами первого 26 И второго 27 элементов И-НЕ, вторые входы которых соединены с третьим и четвертым входами дешифратора управляющих сигналов 25, информационные входы которого соединены с выходами первого 17 и второго 18 триггеров, входы синхронизации кото- рых соединены с входом синхронизации третьего триггера 24 и с выходом третьего приемника 5, выход второго приемника 4 соединен с первым входом элемента И 15, второй вход которого соединен с вторым входом первого элемента И 14 и с прямым выходом третьего триггера 24, инверсный выход которого соединен с входом выборки дешифратора 25 управляющих сигналов, информационный вход третьего триггера 24 соединен с выходом элемента сравнения 1 б, первая группа входов которого соединена с выходами первой группы приемников 6, вторая группа входов 59 элемента сравнения 16 является входами установки номера группы каналов устройства, информационные входы первого 17 и второго 18 триггеров соединены с выходами четвертого 7 и пятого 8 приемников, выход первого элемента И-НЕ 26 соединен с входами синхронизации счетчика управления 22 и четвертого триггера 19, информационный вход которого соединен с выходом шестого приемника 10, выход второго элемента И- НЕ 27 соединен с входом синхронизации счетчика адреса 12, информационные входы которого соединены с выходами приемников 11 третьей группы, информационные входы дешифратора выбора 28 соединены с информационными выходами счетчика управления 22, информационные входы которого соединены с выходами приемников второй группы 9, входы увеличения и уменьшения счетчика управления 22 соединены с выходами прямого и обратного переноса счетчика адреса 12, группа информационных выходов 62 которого соединена с информационными входами-выходами 57 блока внутренних приемопередатчиков 34, первый вход третьего элемента И-НЕ 21 соединен с прямым выходом 51 четвертого триггера 19 и через передатчик 80 блока внутренних приемопередатчиков 34 с входами выбора режима № блоков управления 36, инверсный выход четвертого триггера 19 соединен с первым входом четвертого 20 элемента И-НЕ, второй вход которого соединен с вторым входом третьего элемента И-НЕ 21 и с выходом второго элемента ИЛИ 29, входы которого соединены с первыми выходами 60 управления № блоков управления 36 соответственно, входы управления блоков внутренних приемопередатчиков 34 соединены с вторыми выходами 63 управления № блоков управления 36, гёруппы информационных входов и выходов которых соединены с группами информационных выходов и входов соответствующих блоков приемопередатчиков нижнего уровня 35, выходы приемников 30 четвертой группы соединены с информационными входами выходного регистра 31, информационные выходы входного регистра 33 соединены с входами группы передатчиков 32, выход 47 второго передатчика 37 подключен к младшему разряду в группе информационных входов-выходов ЭВМ верхнего уровня, первый вход второго передатчика 37 подключен к выходу третьего элемента И 39, первый вход которого соединен с четвертым выходом дешифратора управляющих сигналов 25, второй вход передатчика 37 соединен с выходом пятого триггера 38, вход синхронизации которого соединен с выходом первого элемента ИЛИ 23, вход установки в ноль Р пятого триггера 38 соединен с выходом третьего элемента ИЛИ 40, входы 61 которого соединены с третьими выходами управления № блоковуправления 36 прямым доступом к памяти, второй вход третьего

элемента И 39 соединен с выходом первого элемента И 14, выхода третьего 20 и четвертого 21 элементов И-НЕ соединены с выходами увеличения и уменьшения счетчика адреса соответственно.

Работу устройства рассмотрим на примере использования его для организации мультипроцессорной системы на базе ЭВМ или микроЭВМ имеющих интерфейс типа ОБЩАЯ ШИНА. При этом в устройстве входы установки в ноль R счетчиков 12, 22 и регистра 62 необходимо соединить с цепью сигнала СБРОС ЭВМ верхнего уровня (с целью упрощения схемы цепь СБРОС на фигурах не показана). Неиспользуемые выводы элементов необходимо соединить с цепью ОБЩ или +5В через резистор 1кОМ, в зависимости от их назначения, для обеспечения их помехозащищенности и незапланированного срабатывания.

Линии сигналов 45...50 необходимо соединить с шиной АДРЕС/ДАННЫЕ ЭВМ верхнего уровня.

Устройство работает в двух режимах под управлением ЭВМ верхнего уровня:

вывод информации в режиме прямого доступа к памяти в одну из M-N-ю ЭВМ нижнего уровня;

ввод информации в режиме прямого до- ступа к памяти из одной из M N-й ЭВМ нижнего уровня.

Передача информации происходит в соответствии с тремя циклами:

цикл записи в счетчик адреса 12 адреса ячейки памяти ЭВМ нижнего уровня с которой будет осуществляться обмен информацией;

цикл записи в счетчик управления 22 и триггер 19 информации о номере ЭВМ нижнего уровня, с которой будет осуществляться обмен данными, и код режима;

цикл Записи (чтения в регистр 31) из регистра 33 передаваемых/ принимаемых данных.

Рассмотрим подробно вышеперечисленные циклы.

Режим вывода информации.

В соответствии с логикой работы интерфейса ОБЩАЯ ШИНА в первой фазе каждого цикла обмена по линиям АДРЕС/ДАННЫЕ передается адрес счетчика или регистра с которого будет осуществляться обмен, с некоторой задержкой по отношению к передаче адреса выдается сигнал СИА на линию 44; Старшие разряды адреса поступают по линиям 45 через приемники 6 на первые входы элементов сравнения 16 всех групп II...IN, на вторые входы которых подают код номера группы, присвоенный ему в адресном пространстве ЭВМ

верхнего уровня. При совпадении адреса на первых входах элемента сравнения с кодом на вторых входах на его выходе формируется сигнал логической 1, поступающий на 5 информационный вход триггера 24. На информационные входы триггеров 17, 18 поступают по линиям 46i, 462, через приемники 7, 8 младшие разряды адреса, определяющие адрес счетчика адреса 12.

0 Сигнал СИА, поступающий по линии 44 через приемник 5 на входы синхронизации триггеров 17, 18 и 24 осуществляет запись кода адреса счетчика адреса 12 в триггеры 17, 18 и сигнала с выхода элемента сравне5 ния 16 в триггер 24.

Вторая фаза цикла обмена начинается со снятия адреса с линий АДРЕС/ДАННЫЕ, установки на этих линиях адреса ячейки памяти с которой будет происходить

0 обмен информацией и установки на линии 43 сигнала ВЫВОД. Под действием этого сигнала на выходе элемента И 15 появится сигнал высокого уровня, который, совместно с сигналом высокого уровня на выходе

5 дешифратора 25, сформирует сигнал записи низкого уровня на выходе элемента 27. Этот сигнал поступит на вход записи счетчика адреса 12 и произведете него запись адреса ячейки памяти, поступающий с магистрали

0 56 по линиям 49 через группу приемников 11 на информационный вход счетчика адреса 12. Одновременно, сигнал высокого уров- ня с выхода элемента И 15 установит через элемент ИЛИ 23 триггер 38 в единичное

5 состояние и поступит через элемент задержки 13 на входы передатчика 2, на выходе 41 которого сформируется сигнал ответа СИП поступающий в интерфейс ЭВМ верхнего уровня. ЭВМ, получив сигнал СИП от

0 устройства, снимает сигнал ВЫВОД, что приводит к снятию сигнала записи на выходе элемента И-НЕ 27 и к снятию сигнала СИП на линии 41. Завершается вторая фаза цикла обмена снятием сигнала СИА с линий

5 44 магистрали 56. Далее аналогичным образом будет произведена запись передаваемых данных в регистр 31, при этом сигналом с выхода дешифратора 25 производится выборка регистра 31. Следующее обращение i

0 ЭВМ верхнего уровня производит к счетчику управления 22 и записывает в него ( логично счетчику адреса) код управления, содержащий номер ЭВМ нижнего уровня и, в младшем разряде, бит режима (I - вывод

5 информации, 0 - ввод информации), который записывается в триггер 19. Код управления с выхода счетчика управления 22 поступает на вход дешифратора 28, на одном из выходов которого формируется сигнал пуска выбранной ЭВМ нижнего уровня.

Этот сигнал совместно с сигналом режима на линии 51 поступают на входы 51 и 64 (сигнал режима через передатчик 80 блока внутренних приемопередатчиков 34) блока управления прямым доступом в память 36.

Блок управления 36 работает следующим образом: после включения ЭВМ верхнего уровня формирует сигнал СБРОС который поступает на входы R регистров 67 всех блоков управления 36 м устанавливает их в нулевое состояние. После установки в нулевое состояние из ПЗУ 68 .выбирается первая микрокоманда формирующая следующие сигналы:

линии 54, 55 - код 10 обеспечивается отключение передатчиков 70 от магистралей ЭВМ нижнего уровня;

линия 63 - логический О - обеспечивается подключение групп передатчиков 78, 79, 80 и отключение группы передатчиков 81 от магистралей 58 и 57;

линии 60, 61 ЛОГИЧЕСКАЯ 1 - отсутствие управляющих сигналов.

Выполнение микропрограммы защитой в ПЗУ 68 начинается с анализа сигналов на-входах 51 и 64. При обнаружении кода И (ВЫВОД, ПУСК)один из блоков 36 осуществляют выдачу из ПЗУ через передатчики 76 сигнала ТПД, обеспечивая требование на доступ к интерфейсу выбранной ЭВМ нижнего уровня. Поступление сигнала подтверждение ППД от ЭВМ нижнего уровня через приемники 77 на входы мультиплексора 65 обеспечивает ветвление микропрограммы и установку-на выходе ПЗУ 68 сигнала ПВ поступающего через передатчики 76 в интерфейс ЭВМ нижнего уровня. Данный сигнал сохраняется блоком . управления до завершения операций передачи информации в/из память ЭВМ нижнего уровня. -;- ------

Передача информации в ЭВМ нижнего уровня начинается с установки на выходах 54 и 55 кода 11 поступающего на входы блока приемопередатчиков 35 и разрешающего передачу содержимого счетчика адреса 12 с выходов передатчиков 79 блока внутренних приемопередатчиков 34 через передатчики 70 и 78 в магистраль ЭВМ нижнего уровня и интерпретируется ЭВМ как адрес. После этого блок управления через мультиплексор 65 осуществляет анализ ти- режима на линии 51 и переходит к выполнению операции ВЫВОД или ВВОД.

При обнаружении кода 1 на входе 51 блок управления формирует на выходах 54 и 55 код 01 закрывающий передатчики 70 и открывающий (через элемент И 74) передатчики 71. При этом содержимое регистра 31 данных поступает через передатчики 79 и 71 в магистраль ЭВМ нижнего уровня. Одновременно из ПЗУ 68 через передатчики 76 в

магистраль ЭВМ нижнего уровня выдается сигнал ВЫВОД, а затем блок управления осуществляет ожидание от ЭВМ нижнего уровня сигнала подтверждения СИП, который поступает от ЭВМ нижнего уровня че0 рез приемник из группы приемников 77 на мультиплексор 65. При поступлении сигнала СИП блок управления снимает с выхода ПЗУ 68 ранее сформированный сигнал ВЫВОД на выходах передатчиков 76, а на вы5 ходах 60 и 61 формируются сигналы логической 1, поступающие через элементы ИЛИ 29 и 40 на входы элементов И-НЕ 20, 21 и вход установки в ноль триггера 38, соответственно. При этом триггер 38 перей0 дет в нулевое состояние, а счетчик 12 увеличит код содержимого на 1. Затем блок управления 36 осуществляет анализ сигнала СИП, поступающего из интерфейса ЭВМ нижнего уровня. При сборе в интерфейсе

5 ЭВМ сигнала СИП блок управления осуществляет сброс всех ранее сформированных сигналов (конец выполнения цикла) и воз- вращае-гся в исходное состояние. При передаче второго слова из передаваемого

0 массива информации достаточно поместить в регистр 31 передаваемые данные и выполнить фазу ВЫВОД, т.к. адрес ячейки памяти установлен и код операции не изменился. При заполнении информацией всех ячеек

5 памяти ЭВМ нижнего уровня счетчика адреса 12 установится в нулевое состояние и на его выходе прямого переноса сформируется импульс который поступит на вход увеличения счетчика управления 22 и увеличит код

0 его состояния на 1. При этом на выходе дешифратора 28, соединяющем со входом пуска следующей ЭВМ нижнего уровня, появится сигнал ПУСК для этой ЭВМ. Код режима (ВЫВОД) не изменился, поэтому

5 ЭВМ верхнего уровня может продолжать операцию ВЫВОД в следующую ЭВМ нижнего уровня, Емкость счетчика 22 соответствует количеству ЭВМ нижнего уровня подключенных к магистрали 58, поэтому

0 при заполнении информацией последней . ячейки последней ЭВМ нижнего уровня счетчики 12 и 22 обнулятся и на выходах дешифратора 28 установятся низкие уровни сигналов, что соответствует отсутствию сиг5 налов ПУСК и окончанию ввода информации в первую группу Ыканалов для связи с L, ЭВМ нижнего уровня. Далее ЭВМ верхнего уровня производит обмен информацией со - следующей группой, например 2, каналов для связи с ЭВМ нижнего уровня.,

ВЫВОД ИНФОРМАЦИИ.

Первая фаза обмена (адресный цикл) аналогична операции ВЫВОД ИНФОРМАЦИИ с записью в счетчик адреса 12 - адреса ячейки памяти из которой будет происходить чтение информации, в счетчик управления - номера ЭВМ нижнего уровня с которой будет происходить обмен (в младшем разряде код режима ВВОД О) и установки на магистраль адреса регистра данных 32.

Вторая фаза цикла обмена начинается со снятия адреса с магистрали 56 и поступления сигнала ВВОД из интерфейса ЭВМ верхнего уровня по линии 42 через приемник 3 на вход элемента И 14, на второй вход которого поступает сигнал высокого уровня с прямого выхода триггера 24. При этом на выходе элемента И 14 формируется сигнал высокого уровня который поступает на входы:

, регистра 33, где совместно с сигналом с дешифратора 25 производит чтение его содержимого;

элемента И 39, где на его выходе, совместно с сигналом с выхода дешифратора 25, формируется сигнал высокого уровня позволяющий вывести на магистраль через передатчик 37 бит готовности с выхода триггера 38;

элемент ИЛИ 23 для формирования сигнала СИП.

При обнаружении на входах 51 и 64 кода 01 (ВВОД, ПУСК) блок управления осуществляет выдачу из ПЗУ 68 через передатчики 76 сигнала ВВОД и магистраль выбранной ЭВМ нижнего уровня. Поступление от ЭВМ нижнего уровня сигнала СИП по одной из цепей через передатчик группы 77 к мультиплексору 65 означает что на линиях ДАННЫЕ магистрали ЭВМ нижнего уровня подана требуемая информация (содержимое адресуемой ячейки памяти ЭВМ нижнего уровня), Блок управления осуществляет формирование на выходах ПЗУ 68 следующего кода:

линии 54 и 55 - 00;

линии 60, 61, 63-011

обеспечивающего открывание передатчиков 72, 81 и прохождение через них информации из магистрали ЭВМ нижнего уровня на входы 53, откуда она по сигналу ВВОД от ЭВМ верхнего уровня передается в ее магистраль. Далее блок управления завершает выполнение операции ВВОД аналогично операции ВЫВОД, но с поступлением импульсов по линии 60 через элемент ИЛИ 29 и элемент И-НЕ 21 на вход уменьшения счетчика адреса 12 и уменьшающего код его состояния на 1. Т.е. устройство, позволяет

организовать последовательное чтение информации из ЭВМ нижнего уровня с наибольшим номером без выполнения множества операций занесения адреса 5 ячейки памяти номера ЭВМ нижнего уровня. Передача (прием данных) в/из ЭВМ нижнего уровня производится ЭВМ верхнего уровня после чтения и анализа бита готовности на линии 47, передатчика 37, Таким 0 образом использование заявляемого изобретения позволяет, сохраняя все функции прототипа, увеличить количество ЭВМ нижнего уровня, подключаемых к ЭВМ верхнего уровня, и повысить скорость обмена масси- 5 вами информации между ними за счет групповой адресации и исключения множества операций занесения адреса ячейки памяти и номера ЭВМ нижнего уровня.

Для определения количественного зна- 0 чения повышения быстродействия используем временные соотношения приведенные на фиг, 6 и следующие выражения:

Топ(ТД+Тд+ТУ)К-М

Тоз ТА1+Ту1+Тук+Тд- СМ, 5 где ТА - время передачи адреса ячейки памяти в регистр адреса прототипа или в счетчик адреса заявляемого устройства;

Тд - время пе 1дачи данных в регистр данных прототип ши заявляемого устрой- 0 ства;

Ту - время передачи кода номера ЭВМ нижнего уровня и кода режима в регистр управления прототипа;

К - количество слов передаваемого мас- 5 сива информации;

N - количество ЭВМ нижнего уровня участвовавших в обмене;

Tyi - время передачи кода номера ЭВМ нижнего уровня и кода режима в счетчик 0 управления заявляемого устройства при передаче первого слова из массива информации;

Тук - время передачи кода номера ЭВМ нижнего уровня и кода режима в счетчик 5 управления заявляемого устройства при передаче К-го (последнего) слова из массива информации (в случае окончания обмена по инициативе ЭВМ верхнего уровня);

Топ - время обмена массивом информа- 0 ции из К-слов между ЭВМ верхнего уровня и N ЭВМ нижнего уровня в прототипе;

Тоз время обмена массивом информации из К-слов между ЭВМ верхнего уровня и N ЭВМ нижнего уровня в заявляемом уст- 5 ройстве.

Топ (Тд + Тд + Ту) К N

Тоз Тд + ТУ1 -НГуК +Тд К N

т.к. Тд+Ту 1 + Тук« Тд К N, а ТА . Тд. Ту

$

Топ ( К

Тоз Гд К-N

Тд1д 1у +1

ТдТд Тд

N

3,

т.е. быстродействие заявляемого устройства в три раза больше, чем прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения двух ЭВМ | 1987 |

|

SU1499360A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации мультипроцессорной иерархической вычислительной системы. Цель изобретения - повышение быстродействия. Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня мультипроцессорной иерархической системы содержит первый и второй дешифраторы, входной регистр, Н блоков управления с прямым доступом в память, блок приемопередатчиков, выходной регистр, Н блоков приемопередатчиков группы, два передатчика, шесть приёмников, группу передатчиков/элемент задержки, узел сравнения, два счетчика, пять триггеров, три элемента И, четыре элемента И-НЕ, три элемента ИЛИ. 6 ил.

Формула изобретения Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы, содержащее входной И выходной регистры, первый и второй дешифраторы, блок приемопередатчиков, с первого по Н-й блоки управления прямого доступа в память (где Н - число процессоров нижнего уровня иерархической мультипроцессорной системы) и с первого по Н-й блоки приемопередатчиков группы, причем первый и второй выходы первого дешифратора подключены соответственно к входам синхронизации входного и выходного регистров, с первого по Н-й выходы второго дешифратора подключены соответственно к входам синхронизации входного и выходного регистров, с первого по Н-й выходы второго дешифратора подключен соответственно к входам запуска блоков управления прямым доступом с первого по Н-й, первые и вторые выходы которого подключены соответственно к первым и вторым управляющим входам блоков приемопередатчиков с первого по Н-й группы, информационный вход входного регистра чзреэ первую информационную магистраль подключен к выходу выходного регистра и первому информационному входу-выходу блока приемопередатчиков, второй информационный вход-выход которого через вторую информационную магистраль подключен к первым информационным входам-выходам блоков приемопередатчиков с первого по Н-й группы, вторые информационные входы-выходы которых подключены соответственно к информационным входам-выходам с первого по Н-й группы устройства, подключаемым к группе про- цессоров нижнего уровня, отличающе- е с я тем, что, с целью повышения быстродействия нижнего уровня, оно содержит первый и второй передатчики, с первого по шестой приемники, с первой по четвертую группы приемников, группу передатчиков, элемент задержки, узел сравнения, первый и второй счетчики, с первого по пятый триггеры, с первого по третий элементы И, с первого по четвертый элементы И-НЕ и с

первого по третий элементы ИЛИ, причем информационные входы первой группы устройства, соединенные с процессором верхнего уровня, подключены соответственно к информационным входам приемников первой группы, информационные входы второй группы устройства, соединенные с процессором верхнего уровня, подключены соответственно к информационным входам приемников второй группы и соответственно к информационным входам приемников третьей группы, информационные входы третьей группы устройства, соединенные с процессором верхнего уровня, подключены к информационным входам приемников четвертой группы, первый и второй входы режима устройства, соединенные с процессором верхнего уровня, подключены соответственно к информационным входам первого и второго приемников, инверсные выходы которых подключены соответственно к первым входам первого и второго элементов И, входы номера группы канала устройства, соединенные с процессором верхнего уровня, подключены соответственно к Информационным входам первой группы узла сравнения, выход которого подключен к информационному входу первого триггера, прямой выход которого подктз- чен к вторым входам первого и- второго элементов И, управляющий, первый и второй1 адресный и информационный входы устройства, соединенные с процессором верхнего уровня, подключены соответственно к информационным входам приемников с третьего по шестой, инверсный выход третьего приемника подключен к входам синхронизации первого, второго и третьего триггеров, инверсный выход первого триггера подключен к входу синхронизации первого дешифратора, третий выход которого подключен к первому входу первого элемента И-НЕ, выход которого подключен к входу синхронизации четвертого триггера и входу синхронизации первого счетчика, информационные выходы которого подключены соответственно к информационным входам второго дешифратора, инверсные выходы четвертого и пятого приемников подключены соответственно к информационным эходам второго и третьего триггеров, прямые выходы которых подключены соответственно к первому и второму информационным входам первого дешифратора, четвертый выход которого подключен к первым входам третьего элемента И и второго элемента И- НЕ, выход которого подключен к входу синхронизации второго счетчика, инверсный выход шестого приемника подключен к информационному входу четвертого триггера, прямой выход которого подключен к первому входу третьего элемента И-НЕ, выход которого подключен к входу декремента второго счетчика, первый и второй информационные выходы которого подключены соответственно к входам декремента и инкремента первого счетчика, выход первого элемента И подключен к входу считывания/записи входного регистра, к второму входу третьего элемента И и первому входу первого элемента ИЛИ, выход которого подключен к счетному входу пятого триггера, к управляющему входу первого передатчика и входу элемента задержки, выход которого подключен к информационному входу первого передатчика, инверсный выход которого подключен к выходу синхронизации устройства, подключаемому к процессору верхнего уровня, выход второго элемента И подключен к входу считывания/записи выходного регистра, к второму входу первого элемента ИЛИ и вторым входам первого и второго элементов И-НЁ, выход третьего элемента И подключен к управляющему входу второго передатчика, прямой выход которого подключен к информационному выходу устройства, соединенному с процессором верхнего уровня, выходы входного регистра подключены соответственно к информационным входам передатчиков группы, выходы которых подключены соответственно к информационным выходам группы устройства, соединенным с процессором верхнего уровня, выходы приемников первой, второй, третьей и четвертой групп подключены соответственно к входам второй группы узла сравнения, к информационным входам первого счетчика, к информационным входам выходного регистра и к информационным входам второго счетчика, инверсный выход четвертого триггера подключен к первому входу четвертого элемента И-НЕ и через первую информационную магистраль соединен с третьим информационным выходом второго счетчика, с информационным входом входного регистра и первым информационным входом втжЗДЬм блока приемопередатчиков, выход четвертого элемента И-НЕ подключен к входу инкремента второго счетчика, третьи выходы блоков управления прямым доступом в память с первого по Н-й подключены к входам второго элемента ИЛИ, выход которого подключен к вторым входам третьего и четвертого элементов И- НЕ, четвертые выходы блоков управления прямым доступом в память спервого по Н-й подключены к входам третьего элемента ИЛИ, выход которого подключен к входу установки в О пятого триггера, прямой выход которого подключен к информационному входу второго передатчика, пятые выходы блоков управления прямым доступом в память с первого по Н-й подключены соответственно к управляющим входам блока приемопередатчиков, входы режима блоков управления прямым доступом в память с первого по Н-й через вторую информационную магистраль соединены с первыми информационными входами-выходами блоков приемопередатчиков группы и вторым информационным входом-выходом блока при- емопередатчиков, информационные входы и выходы а-ro (где ,.,.,Н) блока приемопередатчиков группы подключены соответст- венно к выходам группы и к информационным входам а-го блока управления прямым4доступом в память.

1789988 I Адрес

Фиг.З

со оо о о со 1

Фиг. 5

| Бонд Д | |||

| Минисуперкомпьютеры: архитектурные решения, обеспечивающие суперкомпьютерную вычислительную мощность, Электроника, 1988, № 19, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Буглаков С.С | |||

| и др | |||

| Проектирование цифровых систем на комплектах микропрог- раммируемых БИС | |||

| М.: Радио и связь, 1984, с | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-07-03—Подача