преобразователя, подключенного цифровым входом к выходу первого блока .памяти и к цифровым входам второго и седьмого цифроаналоговых преобразователей, а стррбирующие входы третего, четвертого, пятого и восьмого цифроаналоговых преобразователей соединены с выходами второго дешифратора, подключенного первым информационным входом к выходу старшего разряда первого реверсивного регистра сдвига, первому информационному входу первого дешифратора, первому адресному входу первого блока памяти и к информационному входу первого разряда первого реверсивного, регистра сдвига, соединенного выходом первого разряда с информационным входом своего старшего разряда, входом управления сдвигом - с выходом переноса первого счетчика, входом управления сдвиг.ом вправо второго реверсивного регистра сдвига, вторым входом первого элемента ИЛИ и с первым входом шестого элемента ИЛИ, а , входом управления сдвигом влево с выходом второго элемента И, входом второго элемента НЕ, счетным -входом второго счетчика и с входом управления сдвигом влево второго реверсивного регистра сдвига, подключенного выходом первого разряда к информационному входу своего старшего разряда, а вьтходом старшего разряда - к информационному входу своего первого разряда, вторым информационным входам первого и второго дешифраторов и к второму адресному входу первого блока памяти, причем адресные входы второго блока памяти соединены с выходами разрядов первого и второго счетчиков, первый счетчик подключен счетным входом к выходу переноса второго счетчика и к второму входу шестого элемента ИЛИ, а. входом.обнуления - к выходу первого элемента НЕ, входу обнуления второго счетчика и к входу обнуления третьего счетчика, соединенного счетным входом с выходом шестого элемента И1Ш, выходами разрядов с соответствующими адресными входами первого блока памяти, а выходом переноса - со стробируюцим входом первого триггера, подключенного входом установки в 1 к шине сброса устройства, а инверсным выходом - к второму входу первого элемента И, соединенного выходом с первым входом второго элемента И и с первым входом второго элемента -И-НЕ, подключенного выходом к стробирующему входу первого дешифратора и к входу установки в 1 второго триггера, соединенного входом обнуления, с вькодом первого элемента ИЛИ, прямьгм выходом - с вторым входом второго элемента И, а инверсным выходом - с вторым входом второго элемента И-НЕ, причем стробирутощий вход второго дешифратора подключен к выходу второго, элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Аналого-цифровой логарифмический преобразователь | 1984 |

|

SU1236511A1 |

| Устройство для отделения хроматографического микропика от склона основного пика | 1985 |

|

SU1256047A1 |

| Аналого-цифровой нелинейный процессор | 1988 |

|

SU1575194A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

| Функциональный генератор | 1981 |

|

SU1019464A1 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ФУНКЦИЙ, содержащее два блока памяти, первый из которых соединен выходом с цифровым входом первого цифроаналогового преобразователя, подключенного аналоговым входом к выходу двухпо лярного источника опорного нааряжения и к аналоговому входу второго цифроаналогового прео.бразователя, а выходом к аналоговому входу третьего цифроаналогового пpeoбpaзoвafeля, соединенного выходом с входом выходного операционного усилителя и с выходом четвертого цифроаналогового преобразователя, подключенного цифровым входом к вьрсоду второго блока памяти, причем выход второго цифроаналогового преобразователя соединен с аналоговым входом пятого цифроаналогового преобразователя, отличающееся тем, что, с целью повьшения точности аппроксимации функций, в него дополнительно введены ,.с шестого по восьмой цифроаналоговые преобразователи, элементы И, ИЛИ и И-НЕ, триггеры, реверсивные регистры сдвига, счетчики, дешифраторы и генератор тактовых импульсов, соединенньй выходом с первым входом первого элемента И и с первым входом первого элемента И-НЕ,, подключенного вторым входом к шине запуска, устройства, третьим входом - к прямому выходу первого триггера, а выходом - к входу обнуления первого триггера, входу первого элемента НЕ, первому входу первого элемента ИЛИ, входам начальной установки первого и второго реверсивных регистров сдвига и первого блока памяти и к первым входам с второго по пятый элементов ИЛИ, соО) единенньгх вторыми входами с выходами первого дешифратора, а выходами со стробирующими входами первого, второго, шестого и седьмого цифроаналоговых преобразователей соответственно, причем седьмой цифроаналоговьй преобразователь подключен аналоо: . говьм входом к вьосоду двухполярного 4: источника опорного напряжения и к аналоговому входу шестого, цифроана логового преобразователя, а выходомсл к аналоговому входу восьмого цифроаналогового преобразователя, соединенного выходом с входом выходного операционного усилителя, и с выходом пятого цифроаналогового преобразователя подключенного цифровым входом к выходу второго блока памяти и к цифровым входам третьего и восьмого цифроаналоговых преобразователей, а аналоговый вход четвертого цифроаналогового преобразовагеля соединен с выходом шестого цифроаналогового

-. . 1

Изобретение относится к автоматике и вычислительной технике и может найти применение для воспроизведения функций одной переменной.

Известно устройство для воспроизведения функций, содержащее блок компараторов, блок памяти, коммутирующую матрицу, блоки возведения в степень, блоки умножения, источник сигнала развертки и выходной сумматор ij .

Недостатками устройства являются пониженная инструментальная точность

.

воспроизведения функций и относительная конструктивная сложность.

Известно также устройство для воспроизведения функций, содержащее генератор импульсов, делитель частоты, триггер, элементы И, элементы задержки, счетчики, блоки памяти и интегра. торы 2.

Недостатком данного устройства является сложность технической реализации.

Наиболее близким к изобретению является устройство для воспроизведения функций, содержащее два блока па мяти, первьй из которых соединен выходом с цифровым входом первого циф- роаналогового преобразователя, подкл ченного аналоговым входом..к выходу .двухполярного источника опорного напряжения и к аналоговому в.ходу второ го цифроаналогового преобразователя, а выходом - к аналоговому входу третьего цифроаналонового преобразователя, соединенного выходом с входом выходного операционного усилителя и с выходом четвертого цифроанало гового преобразователя, подключенног цифровым входом к выходу второго бло ка памяти, причем выход второго цифроаналогового преобразователя соединен с аналоговым входом пятого цифро аналогового преобразователя, подключенного цифровым входом к выходу младших разрядов регистра кода развертки и к цифровому входу третьего цифроаналогового преобразователя, соединенного аналоговым входом с выходом пятого цифроаналогового преобразователя, причем цифровой вход вто рого цифроаналогового -преобразователя подключен к выходу третьего блока памяти, соединенного адресным входом с адресными входами первого и второ-го блоков памяти и с выходами старших разрядов регистра кода развертки а аналоговый вход четвертого цифроаналогового преобразователя подключен к выходу двухполярного источника опорного напряжения з. . Недостатком устройства является пониженная точность воспроизведения функций, обусловленная квадратичным характером представления аппроксимирукщих функций на подинтервальных разбиениях. Цель изобретения - повьдпение точности аппрокси; 1ации функций. Поставленная цель достигается тем что в устройство для воспроизведения функций, содержащее два блока памяти, первый из которых соединён выходом с цифровым входом первого цифроаналогового преобразователя, подключенного аналоговым входом к вы ходу двухполярного источника опорного напряжения и к аналоговому входу второго цифроаналогового преобразователя, а выходом - к аналоговому входу третьего цифроаналогового пре- образователя, соединенного выходом с входом выходного операционного усилителя и с выходом четвертого цифроаналогового преобразователя, подключенного цифровым входом к выходу второго блока памяти, причем выход второго цифро&налогового преобразователя соединен с аналоговым входом пятого цифроаналогового преобразователя, дополнительно введены с шестого по восьмой цифроаналоговые преобразователи, элементы И, ИЛИ, НЕ и И-НЕ, триггеры, реверсивные регистры сдвига, счетчики, дешифраторы и генератор тактовых импульсов, соединенный выходом с первым входом первого элемента И и первым входом первого элемента И-НЕ, подключенного вторым входом к шине запуска устройства, третьим входом - к прямому выходу первого триггера, а выходом - к входу обнуления первого триггера, входу первого элемента НЕ, первому входу первого элемента ИЛИ, входом начальной установки первого и второго реверсивных регистров сдвига и первого блока памяти и к первым входам с вто рого по пятый элементов ИЛИ, соединенных вторыми входами с выходами первого дешифратора, а выходами со стробирующими входами первого, второго, шестого и седьмого цифроаналоговых преобразователей соответственно, причем седьмой цифроаналоговьй преобразователь подключен аналоговым входом к выходу двухполярного источника опорного напряжения и к аналоговому входу шестого цифроаналогового преобразователя, а выходом к аналоговому входу восьмого цифро- аналогового преобразователя, соединенного выходом с входом выходного операционного усилителя и с выходом пятого цифроаналогового преобразователя, подключенного цифровым входом к выходу второго блока памяти и к цифровым входам третьего и восьмого цифроаналоговых. преобразователей, а аналоговьм вход четвертого цифроаналогового преобразователя соединен с выходом шестого цифроаналогового преобразователя, подключенного-цифровым входом к выходу первого блока, памяти и к цифровым входам второго и седьмого цифроаналогового преобразователей, а стробирукяцие входы третьего, четвертого, пятого и восьмого цифроаналоговых преобразователей соединены с выходами второго дешифратора, подключенного первым ин-

ормациоиным входом к выходу старшего разряда первого реверсивного регистра сдвига, первому информационному входу первого дешифратора, первому адресному входу первого блока памяти и к информационному входу первого разряда первого реверсивного

регистра сдвига, соединенного выхоом первого разряда с информационным входом своего старшего разряда, входом управления сдвигом - с выхоом переноса счетчика, входом управления сдвигом вправо второго-реверсивного регистра сдвига, вторьЫ входом первого элемента ИЛИ и с первым входом шестого элемента ИЛИ, а входом управления сдвигом влево с выходом второго элемента И, входом второго элемента НЕ, счетным входом второго счетчика и с входом управления сдвигом влево второго реверсивного регистра сдвига, подключенного выходом первого разряда к информационлому входу своего старшего разряда, а выходом старшего разряда к информационному входу своего первого разряда, вторым информационным входам первого и второго дешифраторов и к второму адресному входу первого блока памяти, причем адресные входы второго блока памяти соединены с. выходами разрядов первого и второго счетчиков,.первый счетчик подклю)Че« счетным входом к вьЬсоду переноса второго счетчика и к вт-орому входу шестого элемента ИЛИ, а входом обнуления - к выходу первого элемента НЕ, входу обнуления второго счетчика и к входу обнуления третьего

счетчика, соединенного-счетным входом с выходом шестого элемента ИЛИ, выходами разрядов - с соответствуклцими адресными входами первого блока памяти, а выходом переноса - со стробирующим входом цервого триггера, подключенного входом установки

в единицу К; шине сброса устройства, а инверсным выходом - к второму входу первого элемента И, соединенного

выходом с первым входом второго элемента И и с первым входом второго элемента. И-НЕ, подключенного выходом к стробирующему входу первого дешифратора и .к входу установки; в 1 второго триггера, соединенного входом обнуления с выходом первого элемента ИЛИ, прямым выходом - с вторым входом второго элемента И, а инверс-j

ным вЬкодом - с вторым входом второго элемента И-НЕ, причем стробирующий вход второго дешифратора подключен к выходу второго элемента НЕ.

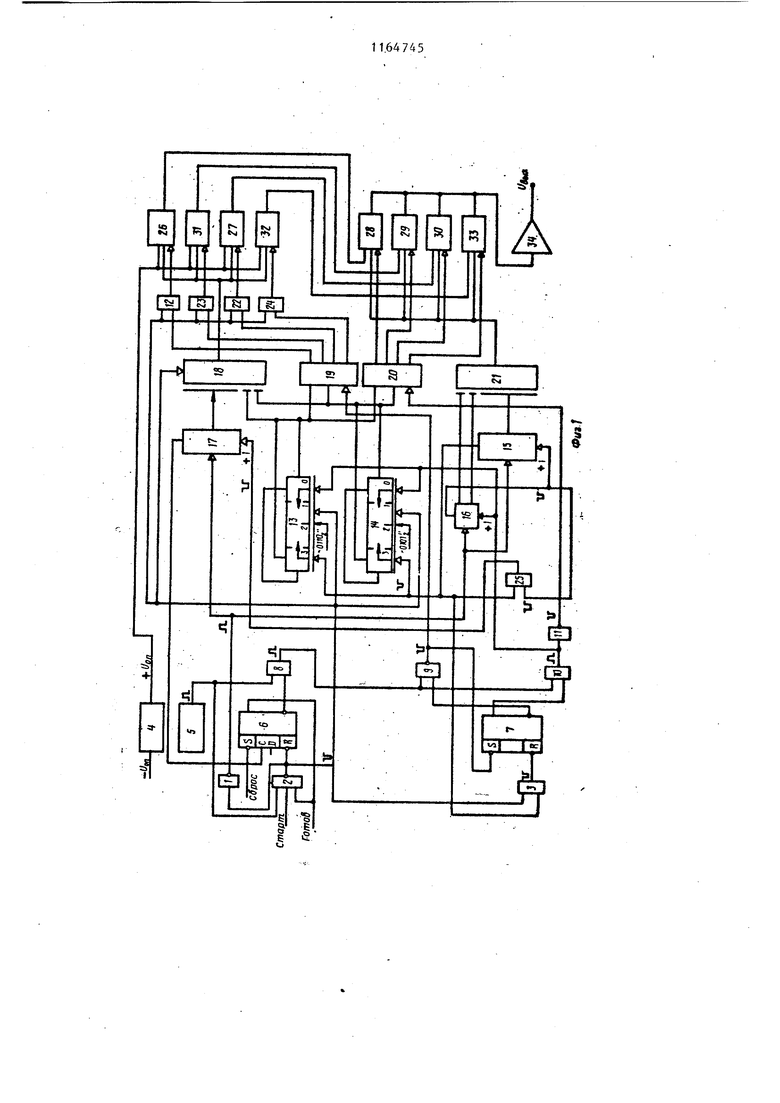

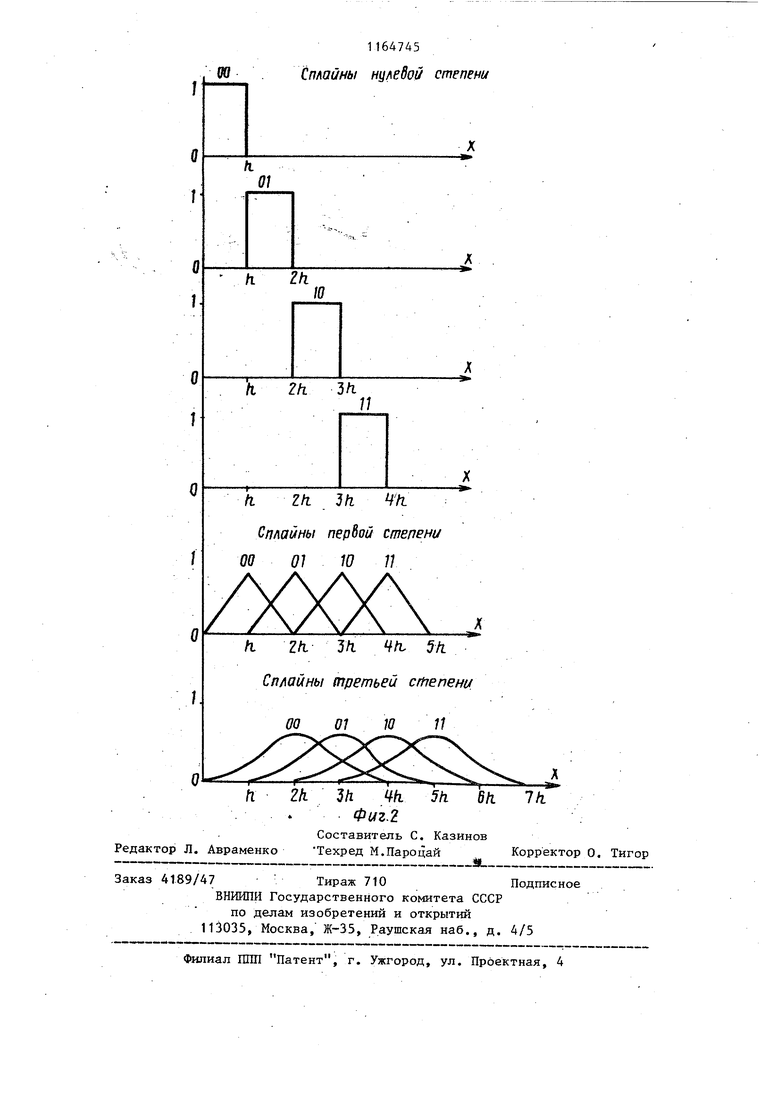

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - графики, поясняюшие его работу.

Устройство для воспроизведения функций содержит первый элемент НЕ 1, первый .элемент И-НЕ 2, первьй элемент ИЛИ 3, цвухполярный источник-4 опорного напряжения, генератор 5 тактовых импульсов, первый триггер 6 (D-типа), второй триггер 7 (RS-типа). первьй элемент И 8, второй элемент И-НЕ -9, второй элемент И 10, второй элемент НЕ 11, второй элемент ИЛИ 12, а также состоит из перворо и второго реверсивных регистров 13 и 14 сдвига, первого, второго и третьего счетчиков. 15, 16 и 17, -первого блока 18 памяти (постоянного запоминающего устройства ординат сплайна), первого ивторого дешифраторов 19 и 20, второго блока 21 памяти (постоянного запоминающего Устройства, формы сплайна), третьего, четвертого, пятого и шестого элементов ИЛИ 22-, 23, 24 и 25, а также включает с первого по восьмой цифроаналоговый преобразователи 26-.33 и вькодной операционный усилитель 34.

Устройство работает следующим образом. I

Внешнее устройство (например, ЭВМ) подает на шину сброса устройства сигнал, по которому триггер 6 устанавлйвается в единичное состояние. На прямом выходе триггера 6 появляется сигнал, свидетельствующий, о готовности Кработе. По этому сигналу -внешнее устройство подает на шину запуска, подключенную ,к второму входу элемента И-НЕ 2, сигнал запуска. Сигналом с выхода элемента И-НЕ 2 устройство устанавливается в исходное состояние: триггер 7 устанавливается в единичное состо-т яние, триггер 6 и счетчики 15-17

обнуляются, в регистре 13 устанавтливается код 0110, в регистре 14 устанавливается код сигнал с выхода элемента И-НЕ 2 устанавл-ивает на выходе всех разрядов блока

памяти нули и через элементы ИЛИ 12, .24-25 стробируют запись нулевого кода в цифроаналоговые.преобразователи 26, 27, 31 и 32. Выходное напряжение этих преобразователей становится равным нулю, что приводит к установке нулевого напряжения на выходе операционного усилителя 34. Сигнал с инверсного выхода трнггеpa 6 отпирает элемент И 8 для прохождения импульсов генератора 5. Первый импульс с выхода элемента И установит триггер 7 в единичное состояние и одновременно запишет инфо нацию с выхода блока 18 памяти в цифроанал.оговый преобразователь 26 за счет прохождения стробирующего импульса через элемент ИЛИ 12, так как на информационные входы дешифра тора 19 (стробирующего сигна лом с в хода элемента И-НЕ 9) в этот момент подается код 00 с выходов третьих разрядов регистров 13 и 14, Таким о разом, на выходе преобразователя 26 установится напряжение, соответству ющее ординате максимума сплайна третьего порядка с номером 00. Поскольку триггер 7 находится в единичном состоянии, то второй импульс с выхода элемента И 8 через элемент И 10 и элемент-НЕ 11 стробирует через дешифратор 20 запись кода с выхода блока 21 памяти в цифроаналоговый преобразователь 28, так как на выходах третьих разрядов регистров 13 и 14 еще сохраняется код 00, Задний фронт этого же импульса с выхода элемента И 10 устанавливает код 01 в счетчике 16 (этот счетчик выполнен двухразрядным) и сдвигает влево на один разряд содержимое регистров 13 и 14. На выходах третьих разрядов этих регистров устанавливается единичный сигнал. Счетчик 16 служит для выбора одного из четырех участков (О, h), (h, 2h), (2h, 3h) и (3h, 4h) в форме сплайна (фиг, 2, где h - шаг аппроксимации). Так как в счетчике 16 теперь установлен код 01, то на выходе блока 21 памяти устанавливается код ординаты формы сплайна для начал ной точки участка. Второй импульс с выхода элементна НЕ 11,- стробируя дешифратор 20, запишет этот код в . цифроаналоговьй преобразователь 33, так как на информационных входах дешифратора 20 установлен код 11. Задний фронт импульса с выхода элемента И 10 установит в счетчике 16 код 10, соответствующий участку формы сплайна (2h, 3h), и сдвинет влево на один разряд содержимое регистров 13 и 14, На выходе третьего разряда регистра 13 устанавливается логическая единица, а на выходе третьего разряда регистра 14 - логический нуль, Третий импульс с выхода элемента НЕ 11, стробируя дешифратор 20, запишет код свыхода блока 21 памяти, соответствующий начальной точке участка (2h, 3h) в цифроаналоговьй преобразователь 30, тик как на информационных входах дешифратора 20 установлен код 10, Задний фронт третьего импульса с выхода элемента И 10 установит в счетчике 16 код 11, соответствующий участку сплайна (3h,. 4h), и сдвигает влево на один разряд содержимое регистра 13 и 14, На выходах тр.етьих разрядов регистров. 13 и 14 теперь установятся логичес- жив сигналы 1 соответственно. Четвертый импульс с выхода элемента НЕ 11, стробируя дешифратор 20, запишет код с выхода блока 21 памяти, соответствующий начальной точке участка (3h, 4h).формы сплайна, в цифроаналоговьй преобразователь 29. Задний фронт четвертого импульса с выхода элемента И 10 вызовет переполнение счетчика 16, Сигнал переполнения счетчика 16 добавит единицу в счетчик 15 и переведет таким образом текущую ординату внутри участка формы сплайна из нулевого в первое положение. В-результате вьш1еописан ных процессов на выходе операционного усилителя 34 появится напряже- . ние, соответствующее начальной точке первого участка аппроксимации заданной функции. Следующие четыре импульса с .выходов элемент-ов НЕ 11 и И 10 вызовут повторение описанных процессов для нового состояния счетчика 15 и на выходе усилителя 34 появится напряжение, соответствующее второй точке первого участка аппроксимации заданной функции. На выходе усилителя 34 после ; каждых четщ)ех импульсов с выходов элементов НЕ 11 и И 10 будет появляться напряжение, соответствую15ее очередной точке первого участка аппроксимации заданной функции, до тех пор, пока не переполнитсясчетчик 15. В этот момент сигналы переполнения с выхода счетчиков 15 и 16 через элемент ИЛИ 25 добавят единицу в счетчик 17 (участков аппроксимации) кода, указьшающего теперь на второй 5 участок аппроксимации заданной функции. В то же самое время сигнал переполнения счетчика 15 сдвинет вправо на один разряд содержимое регистров 13 и 14 и на выходах третьлх раэря- fo дов этих регистров установятся О и 1 соответств.енно. Такой сдвиг необходим при каждом увеличении но мера участка аппроксимации, так как при изменении этого номера меняется 15 соответствие номеров участков формы сплайна и номеров преобразователей 28-30, 33, хранящих код точки соответствующего участка формы сплайна. Кроме этого, сигнал переполнения 20 счетчика 15 через элемент ИЛИ 3 установит триггер 7 в О, разрешив тем самым стробирование дешифратора 19 новым импульсом с выхода элемента И-НЕ 9. В результате код с выхода 25 блока 18 памяти, соответствующий ординате максимума сплайна со следуинцим по порядку номером 01, запишется в преобразователь 31 сигналом с выхода элемента ИЛИ 23, так как зо на информационных входах дешифратора 19 установлен код 01. Тот же импульс с выхода элемента И-НЕ 9 устаг новит триггер 7 в 1, и описанные 1164745 вь до сч ге ст вы по гд 1.СТ зу сп мы е процессы будут продолжаться появления сигнала переполнения тчика 17, который установит триг6 в 1. На этом работа устройа закончена. В произвольный момент времени на оде операционного усилителя 34 держивается напряжение (CB,JO-B , On + Вэ,г в и ; В коды ординат формы BV соответствующихсплайнов третьей степени в данньй момент временя, на данном участке аппроксимации;И.о в ,1 коды ординат максимумов соответствующих сплайнов третьей степени на данном участке аппроксимации;опорное напряжение на выходе источника 4 Таким образом, предлагаемое устройО по сравнению с прототипом реалит аппроксимацию заданных функций айнами третьего порядка, тем саповышая точность воспроизведения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Верлань А.Ф | |||

| и др | |||

| Электронные функциональные преобразователи систем автоматики, Киев, Техника, 1961, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Функциональные преобразователи информации, Л., Энергоиздат, 1982, с | |||

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-09—Подача