ел j ел

со

4ь

Изобретение относится к автоматике и вычислительной технике и может бцть использовано в гибридных вычис- л тельных системах для выполнения функциональных преобразований.

Цель изобретения - увеличение точности за счет аппроксимации функций кубическими сплайнами.

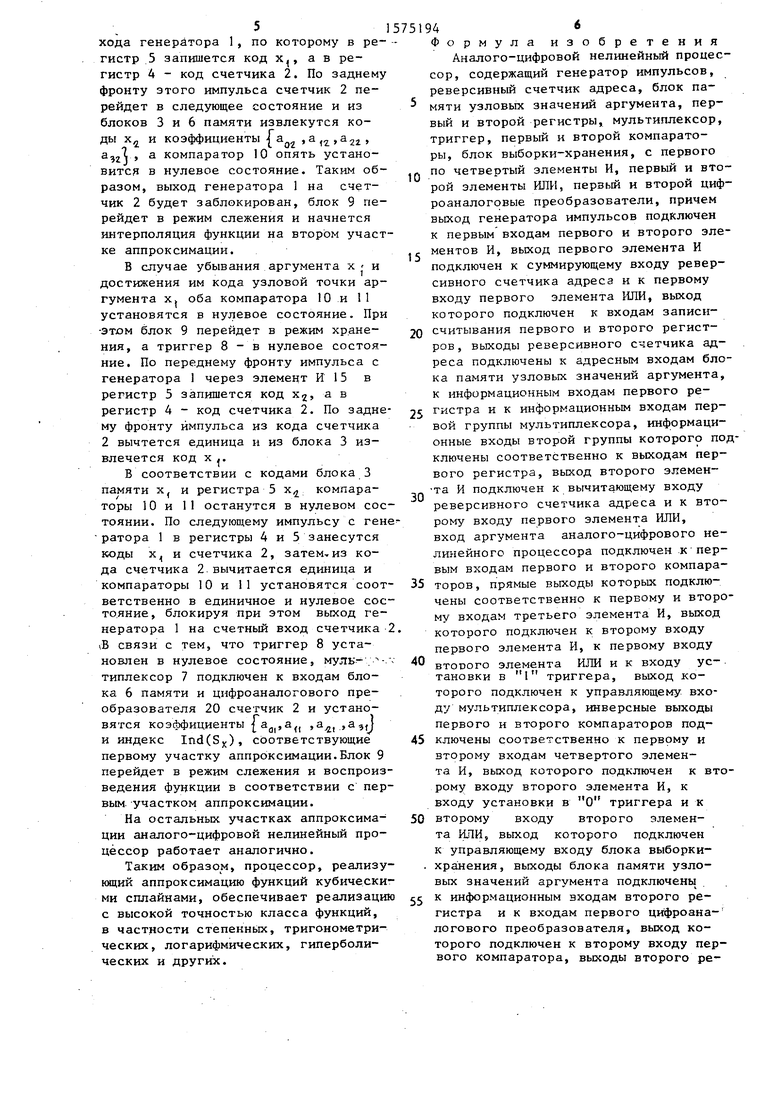

На чертеже изображена схема предлагаемого аналого-цифрового нелинейне

го процессора.

Процессор содержит генератор 1 импульсов, реверсивный счетчик 2 адре- ci, блок 3 памяти узловых значений аргумента, первый и второй регист- рвд 4 и 5, блок 6 памяти коэффициен- тфв сплайна, мультиплексор 7, триг- гфр 8, блок 9 выборки-хранения, первый и второй компараторы 10 и И, первый и второй элементы ИЛИ 12 и 13 с первого по четвертый элементы И1 14-17, с первого по седьмой цифро- аралоговые преобразователи 18-24, с первого по третий суммирующие усили- тели 25-27, с первого по четвертый аналоговые перемножители 28-31.

Аналого-цифровой нелинейный профессор осуществляет аппроксимацию функциональных зависимостей на осно- ее кубических сплайнов, описываемых На основе скобок Горнера следующим выражением:

m

У(х) (x - х- ,) - xj) х

j, jI j

х Laoj + x( + xa,j))l , Где х 0 Ј х х„,

1, если х х ,

(О

G(x -Xj.,)

О, если х х ,.

На каждом участке х х -с х : , выбирая соответствующие коэффициенты

aoj ;

,3 ,« многочлен

Ч

можно вычислить

S-(x)

ао +

х(ам + х(а2; + )). (2)

Выбор коэффициентов осуществляется

на основании условия

т.

Ind(Sx) 51 (х-х-.,) -б(х x-)J ,

(3)

или

.

1,если х0 4 х х, ;

2,если х tЈ -х х2;

j, если х j ч х х j; m, если x xm.

0

5 0 5

0

5

0

45

50

5

Процессор работает следующим образом.

Перед началом работы в блоки 3 и 6 памяти заносятся рассчитанные предварительно коды узловых значений аргумента х j и коэффициенты fa0. ,а , сплайна соответственно,причем в нулевую ячейку блока 6 занесены нулевые коэффициенты.

В исходном состоянии реверсивный счетчик 2, регистры 4 и 5, а также триггер 8 установлены в нуль. Нулевое значение на выходе триггера 8 подключает к адресным входам блока 6 памяти и входам цифроаналогового преобразователя 20 выходы счетчика 2, а единичное - выходы регистра 4.

По нулевому коду счетчика 2 из блоков 3 и б памяти извлечены коды хо и нулевые коэффициенты. При этом компараторы 10 и 11 установятся в единичное состояние, по которому триггер 8 переводится в единичное состояние, блок 9 переводится в режим хранения, а на выходе элемента И 14 формируется импульс с генератора 1. По переднему фронту импульса через элемент ИЛИ 12 в регистр 5 заносится код х , а в регистр 4 - нулевой код счетчика 2. По заднему фронту импульса с генератора 1 счетчик 2 установится в следующее состояние и из блоков 3 и 6 памяти извлекутся коды х{ и коэффициенты а0| ,а1( ,а2, ,а31| . При этом компаратор 10 установится в нулевое состояние, а компаратор 11 останется в единичном состоянии. В результате этого выход генератора 1 будет заблокирован, а блок 9 перейдет в режим слежения.

При поступлении аргумента х , лежащего в пределах участка процессор осуществляет воспроизведение функциональной зависимости в соответствии с выражением (1),причем значение кода счетчика 2, поступающее на адресные входы блока 6 и цифровые входы цифроаналогового преобразователя 24,соответствует Ind(Sx) для данного участка аппроксимации в соответствии с условием (3). В момент достижения аргументом xj значения первой узловой точки х блок 9 перейдет в режим хранения, на время переходных процессов, возникающих при смене кодов на выходах блоков 3 и 6. На выходе элемента И 14 сформируется передний фронт импульса с вы5

хода генератора 1, по которому в ре- гистр 5 запишется код х, а в регистр 4 - код счетчика 2. По заднему фронту этого импульса счетчик 2 перейдет в следующее состояние и из блоков 3 и 6 памяти извлекутся коды х, и коэффициенты {а ,а(г,а22, азгЯ , а компаратор 10 опять установится в нулевое состояние. Таким образом, выход генератора 1 на счетчик 2 будет заблокирован, блок 9 перейдет в режим слежения и начнется интерполяция функции на втором участке аппроксимации.

В случае убывания аргумента х и

достижения им кода узловой точки аргумента х( оба компаратора 10 и 11 установятся в нулевое состояние. При -этом блок 9 перейдет в режим хране- ния, а триггер 8 - в нулевое состояние. По переднему фронту импульса с генератора 1 через элемент И 15 в регистр 5 запишется код xj а в регистр 4 - код счетчика 2. По задне- му фронту импульса из кода счетчика 2 вычтется единица и из блока 3 извлечется код х .

В соответствии с кодами блока 3 памяти х( и регистра 5 х компараторы 10 и 11 останутся в нулевом состоянии. По следующему импульсу с генератора 1 в регистры 4 и 5 занесутся коды х,, и счетчика 2, затем,из кода счетчика 2 вычитается единица и компараторы 10 и 11 установятся соот- ветственно в единичное и нулевое состояние, блокируя при этом выход генератора 1 на счетный вход счетчика 2 В связи с тем, что триггер 8 установлен в нулевое состояние, мулк- л- типлексор 7 подключен к входам блока 6 памяти и цифроаналогового преобразователя 20 счетчик 2 и установятся коэффициенты |аа|,а(( а( аэп и индекс Ind(Sx), соответствующие первому участку аппроксимации.Блок 9 перейдет в режим слежения и воспроизведения функции в соответствии с первым участком аппроксимации.

На остальных участках аппроксима- ции аналого-цифровой нелинейный процессор работает аналогично.

Таким образом, процессор, реализующий аппроксимацию функций кубическими сплайнами, обеспечивает реализацию с высокой точностью класса функций, в частности степенных, тригонометрических, логарифмических, гиперболических и других.

0

5

0 5

5 0 5

0

94

Формула изобретения

Аналого-цифровой нелинейный процессор, содержащий генератор импульсов, реверсивный счетчик адреса, блок памяти узловых значений аргумента, первый и второй регистры, мультиплексор, триггер, первый и второй компараторы, блок выборки-хранения, с первого по четвертый элементы И, первый и второй элементы ИЛИ, первый и второй циф- роаналоговые преобразователи, причем выход генератора импульсов подключен к первым входам первого и второго элементов И, выход первого элемента И подключен к суммирующему входу реверсивного счетчика адреса и к первому входу первого элемента ИЛИ, выход которого подключен к входам записи- считывания первого и второго регистров , выходы реверсивного счетчика адреса подключены к адресным входам блока памяти узловых значений аргумента, к информационным входам первого регистра и к информационным входам первой группы мультиплексора, информационные входы второй группы которого подключены соответственно к выходам первого регистра, выход второго элемен- та И подключен к вычитающему входу реверсивного счетчика адреса и к второму входу первого элемента ИЛИ, вход аргумента аналого-цифрового нелинейного процессора подключен к первым входам первого и второго компараторов, прямые выходы которых подключены соответственно к первому и второму входам третьего элемента И, выход которого подключен к второму входу первого элемента И, к первому входу

ВТОРОГО элемента ИЛИ и к входу установки в 1 триггера, выход которого подключен к управляющему входу мультиплексора, инверсные выходы первого и второго компараторов подключены соответственно к первому и второму входам четвертого элемента И, выход которого подключен к второму входу второго элемента И, к входу установки в О триггера и к второму входу второго элемента ИЛИ, выход которого подключен к управляющему входу блока выборки- хранения, выходы блока памяти узловых значений аргумента подключены к информационным входам второго регистра и к входам первого цифроана- лотового преобразователя, выход которого подключен к второму входу первого компаратора, выходы второго регистра подключены к входам второго цифроаналогового преобразователя, выход которого подключен к второму входу второго компаратора, отличающийся тем, что, с целью увеличения точности за счет аппроксимации функций кубическими сплайнами, он содержит блок памяти коэффициен- тоЬ сплайна, с третьего по седьмрй цифрозналоговые преобразователи, с первого по третий суммирующие усилители и четыре аналоговых перемножителя, причем выходы мультиплексора подключены к входам третьего цифро- ан логового преобразователя и к адрес ньф входам блока памяти коэффициен- тоЈ сплайна, выходы групп с первой по четвертую которого подключены соответственно к входам цифроаналого- вьф преобразователей с четвертого по седьмой, выходы которых подключены соответственно к первым входам первого аналогового перемножителя, первого суммирующего усилителя, второго суммирующего усилителя и третьего сум0

5

0

5

мирующего усилителя, выход первого аналогового перемножителя подключен к второму входу первого суммирующего усилителя, выход которого подключен к первому входу второго аналогового перемножителя, выход которого подключен к второму входу второго суммирующего усилителя, выход которого подключен к первому входу третьего аналогового перемножителя, выход которого подключен к второму входу третьего суммирующего усилителя, выход которого подключен к первому входу четвертого аналогового пер множи- теля, выход которого подключен к выходу аналого-цифрового нелинейного процессора, вход.аргумента которого подключен к информационному входу блока выборки-хранения, выход которого подключен к вторымвходам первого, второго и третьего аналоговых пере- множителей, выход третьего цифроаналогового преобразователя подключен к второму входу четвертого аналогового перемножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1987 |

|

SU1462369A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1709355A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в гибридных вычислительных системах для выполнения функциональных преобразований. Цель изобретения - повышение точности за счет аппроксимации функций кубическими сплайнами. Поставленная цель достигается тем, что процессор содержит генератор 1 импульсов, реверсивный счетчик 2 адреса, блок 3 памяти узловых значений аргумента, первый и второй регистры 4 и 5, блок 6 памяти коэффициентов сплайна, мультиплексор 7, триггер 8, блок 9 выборки-хранения, первый и второй компараторы 10 и 11, первый и второй элементы ИЛИ 12 и 13, с первого по четвертый элементы И 14-17, с первого по седьмой цифроаналоговый преобразователи 18-24, с первого по третий суммирующие усилители 25-27, с первого по четвертый аналоговые перемножители 28-31. 1 ил.

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1987 |

|

SU1462369A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-05-04—Подача