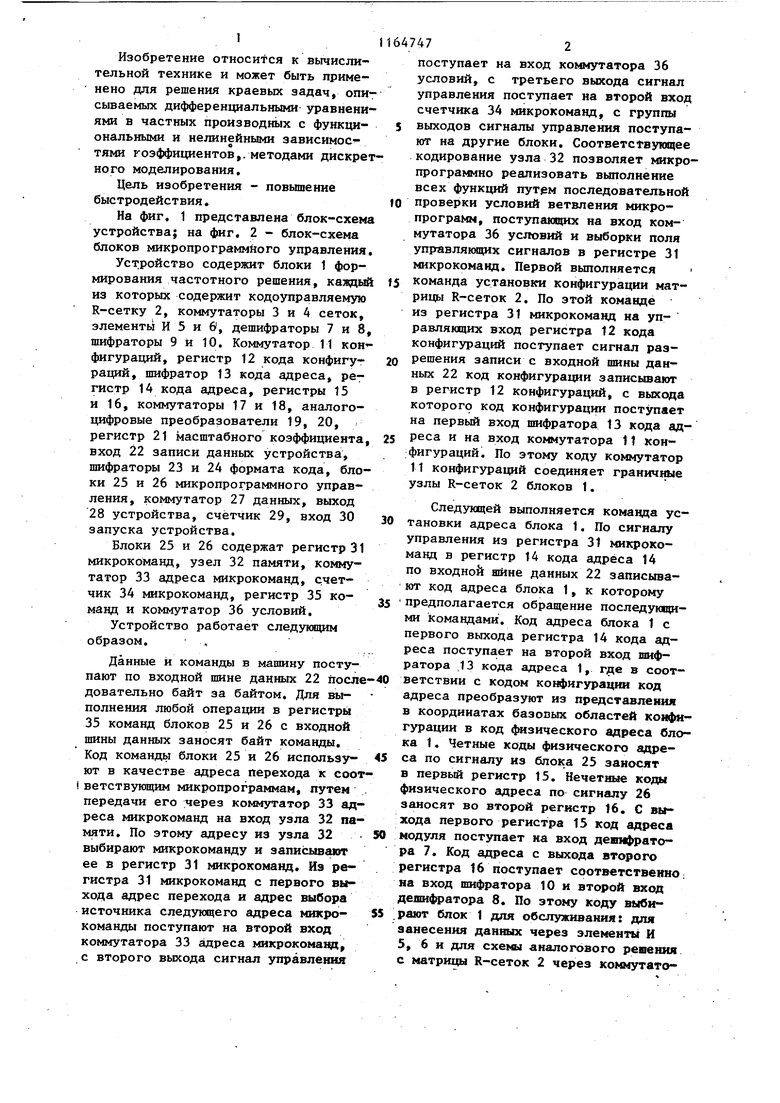

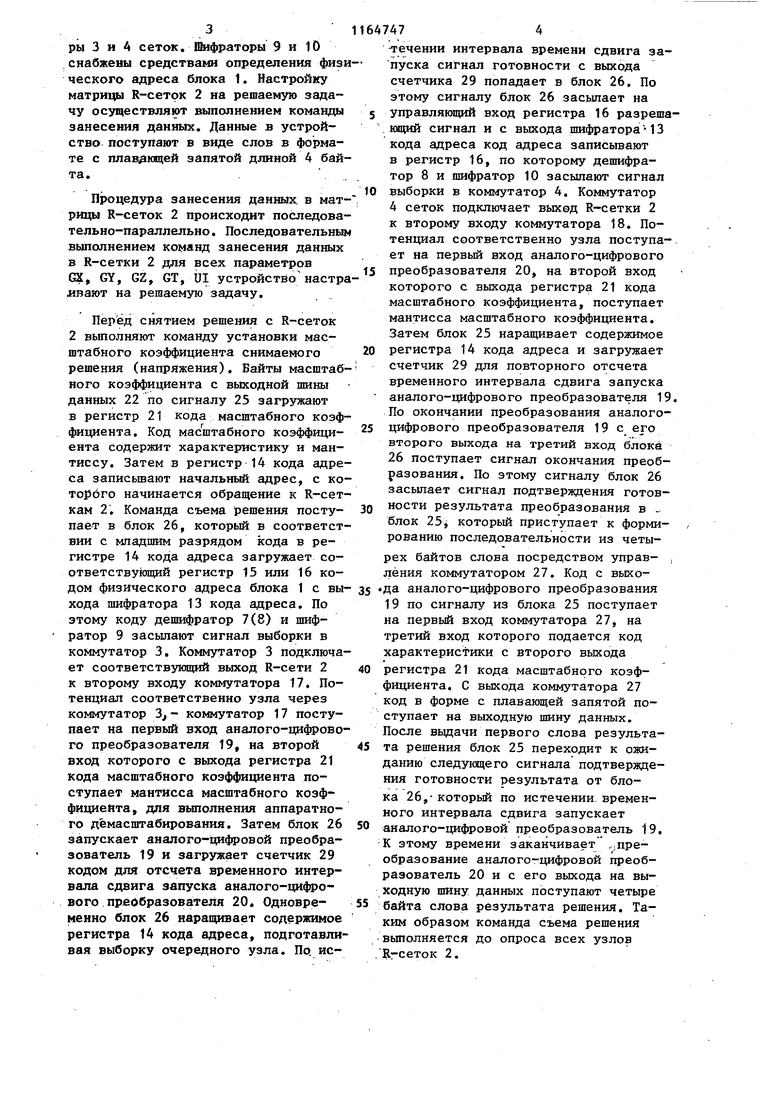

jIHOHHbiMH входами регистра кода адре са и регистра кода конфигураций и с входом регистра команд первого блока микропрограммного управления, вькод поля микроопераций регистра микрокоманд первого блока микропрограммного управления подключен к входам записи регистра кода адреса и регистра кода конфигураций, выход которого соединен с управлякящм BXO дом шифратора кода адреса и с управ ляюнщм входом коммутатора конфигураций, первая группа выходов которо го подключена к первой группе грани ных узлов кодоуправляемой R-сетки первого блока формирования частного решения, вторая группа граничных узлов которой соединена с первой группой информационных входов коммутатора конфигураций, вторая группа выходов которого подключена к первой группе граничных узлов кодоуправляемой R-сетки второго блока формирования частного решения, вторая группа граничных узлов которой соединена с второй группой информационных входов коммутатора конфигур дни, выходы первого коммутатора сеток первого и второго блоков формирования частного решения подключены соответственно к первому и второму информационным входам первого коммутатора, выходы второго коммутатора сеток первого и второго блоков формирования частного решения соеди нены соответственно с первым и втор информационными входами второго ком мутатора, о т л и. ч а ю щ е е с я тем, что, с целью повьшгения быстродействия, в него введены два регист ра, два шифратора формата кода, регистр кода масштабного коэффициента коммутатор данньзх, счетчик и второй блок микропрограммного управления, выход поля микроопераций регистра микрокоманд второго блока микропрограммного управления подключен к третьим входам элементов И обоих блоков формирования частного решени к управляющим входам обоих регистров, к управляющему входу регистра кода адреса, к входам разрешения преобразования первого и второго , аналого-цифровых преобразователей , и к первому информационному входу коммутатора условий первого блока микропрограммного управления, вто47рой информационный вход которого соединен с выходом счетчика, с йхода; ми конца преобразований аналогоцифровых преобрйзователей и регистра кода адреса и с вторым информаЦИОНИЫ24 входом. коммутатора условий второго блока микропрограммного управления, первый информационный вход которого соединен с входом записи регистра конфигураций, с управляющими входами регистра кода масштабного коэффициента, первого и второго шифраторов формата кода и коммутатора данных, выход которого является выходом устройства, вход записи данных которого подключен к входу регистра команд второго блока микропрограммного управления, к информационным входам первого и второго шифраторов формата кода и к информационному входу регистра кода масштабного коэффициента, первьй выход которого подключен к -входам управления аналого-цифровых преобразователей, второй выход регистра кода масштабного коэффициента подключен к первому информационному дходу коммутатора данных, второй и третий информационные входы которого соединены с выходами соответственно первого и второго аналого-цифровых преобразователей, выход регистра кода адреса подключен к информационному входу шифратора кода адреса, выход которого соединен с информационными входами первого и второго регистров, первьй выход первого регистра подключен к управлякщим входам первых дешифраторов, второй выход первого регистра соединен с входами шифраторов и с управляющим входом первого коммутатора, первый выход второго регистра подключен к управлянищм входам вторых дешифраторов, второй выход второго регистра соединен с входами вторых шифраторов и с уп.равляющим входом второго крммутатора, вьщод первого шифратора формата кода подключен к четвертым входам первых элементов И, а выход второго шифратора формата кода соединен с четвертыми входами вторых элементов И, вход запуска устройства подключен к счетному входу счетчика микрокоманд и к входу записи регистра микрокоманд BTojporo блока микропрограм;много управления. Изобретение относится к вычислительной технике и может быть применено для решения краевых задач, опи сываемых дифференциальными уравнени ями в частных производнь1х с функциональными и нелинейными зависимостями коэффициентов,, методами дискре ного моделирования. Цель изобретения - повышение быстродействия, На фиг, 1 представлена блок-схем устройства; на фиг, 2 - блок-схема блоков микропрограммйого управления Устройство содержит блоки 1 формирования частотного решения, катщъ из которых содержит кодоуправляемзпо R-сетку 2, коммутаторы 3 и 4 сеток, элементы И 5 и 6, дешифраторы 7 и 8 шифраторы 9 и 10, Коммутатор 11 кон фигураций, регистр 12 кода конфигураций, шифратор 13 кода адреса, регистр 14 кода адреса, регистры 15 и 16, коммутаторы 17 и 18, аналогоцифровые преобразователи 19, 20, регистр 21 масштабного коэффициента вход 22 записи данных устройства, шифраторы 23 и 24 формата кода, бло ки 25 и 26 микропрограммного управления, коммутатор 27 данных, выход 28 устройства, счётчик 29, вход 30 запуска устройства. Блоки 25 и 26 содержат регистр 3 микрокоманд, узел 32 памяти, коммутатор 33 адреса микрокоманд, счетчик 34 микрокоманд, регистр 35 команд и коммутатор 36 условий. Устройство работает следующим образом, . Данные и команды в машину поступают по входной шине данных 22 посл довательно байт за байтом. Для выполнения любой операции в регистры 35 команд блоков 25 w 26 с входной шины данных заносят байт команды. Код командь блоки 25 и 26 испольэуют в качестве адреса перехода к соо ветствукнцим микропрограммам, путем передачи его через коммутатор 33 ад реса микрокоманд на вход узла 32 па мяти. По этому адресу из узла 32 выбирают микрокоманду и записывают ее S регистр 31 микрокоманд. Из регистра 31 микрокоманд с первого выхода адрес перехода и адрес выбора источника следующего адреса микрокоманды поступают на второй вход коммутатора 33 адреса микрокоманд с второго выхода сигнал управления 472 поступает на вход коммутатора 36 условий, с третьего выхода сигнал управления поступает на второй вход счетчика 34 микрокоманд, с группы выходов сигналы управления поступают на другие блоки. Соответствующее кодирование узла 32 позволяет микропрограммно реализовать выполнение всех функций путэм последовательной проверки условий ветвления микропрограмм, поступающих на вход коммутатора 36 условий и выборки поля управлянщих сигналов в регистре 31 микрокоманд. Первой выполняется команда установки конфигурации матрицы R-сеток 2, По этой команде из регистра 31 микрокоманд на управляющих вход регистра 12 кода конфигураций поступает сигнал разрешения записи с входной шины данных 22 код конфигура1щи записывают в регистр 12 конфигураций, с выхода которого код конфигурации поступает на первый вход шифратора 13 кода адреса и на вход коммутатора 11 конфигураций. По этому коду коммутатор 11 конфигураций соединяет гранич11Ые узлы R-сеток 2 блоков 1, Следунщей выполняется команда установки адреса блока 1, По сигналу управления из регистра 31 микрокоманд в регистр 14 кода адреса 14 по входной шине данных 22 записывают код адреса блока 1, к которому предполагается обращение последующими Командами, Код адреса блока 1 с первого выхода регистра 14 кода адреса поступает на второй вход шифратора 13 кода адреса 1, где в соответствии с кодом конфигурации код адреса преобразуют из представления в координатах базовых областей KOH Iгурации в код физического адреса блока 1, Четные коды физического адреса по сигналу из блока 25 заносят в первый регистр 15, Нечетные кода физического адреса по сигналу 26 заносят во второй регистр 16. С выхода первого регистра 15 код адреса модуля поступает на вход дешифратора 7, Код адреса с выхода второго регистра 16 поступает соответственно: на вход шифратора 1О и второй вход дejшифpaтopa 8, По этому коду выбирают блок 1 для обслуживания; для занесения данных через элементы И 5, 6 и для cxebfij аналогового решения с матрицы R-сеток 2 через коммутато3ры 3 и 4 сеток. Шифраторы 9 и 10 снабжены средствами определения физ ческого адреса блока 1. Настройку матрицы R-сеток 2 на решаемзпо задачу осуществляют выполнением команда занесения данных. Данные в устройство поступают в виде слов в формате с плавднщей запятой длиной 4 бай та.. Процедура занесения данных в мат рицы R-сеток 2 происходит последова тельно-параллельно . Последовательны выполнением команд занесения данных в К-сетки 2 для всех параметров GS, GY, GZ, GT, UI устройствонастр ивают на решаемую задачу. Перёд снятием решения с R-сеток 2 вьтолняют команду установки масштабного коэффициента снимаемого решения (напряжения). Байты масштаб ного коэффициента с выходной шины данных 22 по сигналу 25 загружают в регистр 21 кода масштабного коэф фициента. Код масштабного коэффициента содержит характеристику и мантиссу. Затем в регистр 14 кода адре са записьшают начальный адрес, с ко торого начинается обращение к R-сет кам 2. Команда съема решения поступает в блок 26, который в соответст вии с младшим разрядом кода в регистре 14 кода адреса загружает соответствующий регистр 15 или 16 кодом физического адреса блока 1 с вы хода шифратора 13 кода адреса. По этому коду дешифратор 7(8) и шифратор 9 засылают сигнал выборки в коммутатор 3. Коммутатор 3 подключа ет соответствующий выход R-сети 2 к второму входу коммутатора 17. Потенциал соответственно узла через коммутатор коммутатор 17 поступает на первый вход аналого-цифрово го преобразователя 19, на второй вход которого с выхода регистра 21 кода масштабного коэффициента поступает мантисса масштабного коэффициента , для выполнения аппаратного дёмасштабирования. Затем блок 26 запускает аналого-цифровой преобразователь 19 и загружает счетчик 29 кодом для отсчета временного интервала сдвига запуска аналого-цифрового преобразователя 20. Одновременно блок 26 наращивает содержимое регистра 14 кода адреса, подготавли вая выборку очередного узла. По. ис474-течении интервала времени сдвига запуска сигнал готовности с выхода счетчика 29 попадает в блок 26. По этому сигналу блок 26 засьшает на управляющий вход регистра 16 разрешающий сигнал и с выхода шифратора 13 кода адреса код адреса записьгаают в регистр 16, по которому дешифратор 8 и шифратор 10 засылают сигнал выборки в коммутатор 4. Коммутатор 4 сеток подключает выход R-сетки 2 к второму входу коммутатора 18. Потенциал соответственно узла поступает на первый вход аналого-цифрового преобразователя 20, на второй вход которого с выхода регистра 21 кода масштабного коэффициента, поступает мантисса масштабного коэффициента. Затем блок 25 наращивает содержимое регистра 14 кода адреса и загружает счетчик 29 для повторного отсчета временного интервала сдвига запуска аналого-цифрового преобразователя 19. По окончании преобразования аналогоцифрового преобразователя 19 с его второго выхода на третий вход блока 26 поступает сигнал окончания преобразования. По этому сигналу блок 26 засылает сигнал подтверждения готовности результата преобразования в блок 25i которьй приступает к формированию последовательности из четырех байтов слова посредством управ- , лёния коммутатором 27. Код с выхоДа аналого-цифрового преобразования 19 по сигналу из блока 25 поступает на первый вход коммутатора 27, на третий вход которого подается код характеристики с второго выхода регистра 21 кода масштабного коэффициента. С выхода коммутатора 27 код в форме с плавающей запятой поступает на выходную шину данных. После выдачи первого слова результата решения блок 25 переходит к ожиданию следующего сигнала подтверждения готовности результата от блока 26,-которьй по истечении временного интервала сдвига запускает аналого-хщфровой преобразователь 19. К этому времени заканчивает .;Преобразование аналого-цифровой преобразователь 20 и с его выхода на выходную шину данных поступают четыре байта слова результата решения. Таким образом команда съема решения выполняется до опроса всех узлов R-сеток 2.

ue. i

29 26

25

-JL-

36

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство микропрограммного управления | 1981 |

|

SU960815A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ КРАЕВЫХ ЗАДАЧ, содержащее два блока формирования частного решения, каждый из которых содержит кодоуправляемую R-сетку, два коммутатора сеток, два элемента И, два дешифратора и два шифратора, выход первого из которых подключен к первому входу первого дешифратора и к первому входу первого элемента И, выход которого соедигйен с первым входом задания проводимостей кодоуправляемой R-сетки, первая группа внутренних и граничных узлов которой подключена к группе информационных входов первого коммутатора сеток, управлянщий вход которого соединен с вьпсодом первого дешифратора и с вторым входом первого элемента И, выход второго шифратора подключен к первому входу второго дешифратора и к первому входу второго зле мента И, выход которого соединен с вторым входом задания проводимостей кодоуправляемой R-сетки, вторая труп- : па внутренних и граничных узлов которой подключена к группе информационных входов первого коммутатора сеток управляняций вход которого соединен с выходом первого дешифратора и с вторым входом второго элемента И, первый и второй коммутаторы, выходы которых подключены соответственно к входам первого и второго аналого-цифровых преобразователей, коммутатор конфигураций, шифратор кода адреса, регистр кода адреса, регистр кода конфигураций, первьй лок микропрограммного управления, состоящий из регистра микрокоманд, узла памяти, коммутатора адреса микрокоманд, счетчика микрокоманд, регистра команд и коммутаторд условий, выход которого подключен к управляюп ему входу коммутатора адреса микрокоманд, выход ко(Л торого соединен с входом разрешения ,счета счетчика микрокоманд и с вхо- дом узла памяти, группа выходов которого подключена к группе входов регистра микрокоманд, адресный выход /которого соединен с входом предварительной записи кода счетчика микрокоманд, быход которого подключен к первому информационному входу комму05 татора адреса микрокоманд, второй ин4;; формационный вход которого соединен с выходом безусловного перехода реJiik гистра микрокоманд, выход условного Kl перехода которого подключен к управляющему входу коммутатора условий, выход регистра команд соединен с третьим информационным входом коммутатора микрокоманд, вход запуска устройства подключен к счетному входу счетчика микрокоманд и к входу регистра микрокоманд первого блока микропрограммного управления, вход записи даншлх устройства соединен с информа

VU8. 2

| Устройство для решения нелинейных краевых задач | 1977 |

|

SU661566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-30—Публикация

1983-11-05—Подача