(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления микропрограммных процессоров управляющих или вычислительных систем, допускающих мультипрограммную обработку информации.

Известно устройство микропрограммного управления, обеспечивающее надежность функционирования управляющих и вычислительных систем за счет резервирования и перестройки на раэличны х уровнях иерархии соответствующей структуры, начиная от функциональных элементов и кончая процессорами в целом. Это устройство содержит два запоминающих блока, два регистра адреса, два коммутатора, два триггера управления, элементы И и ИЛИ 1 .

Его недостаткс1ми являются низкие функциональные возможности, обусловленные малой гибкостью и универсальностью устройства.

Наиболее близким техническим решением к изобретению является устройство микропрограммного управления, содержащее блок выработки адреса очередной микрокоманды, два блока памя-

ти микрокоманд, два регистра микрокоманд, два дешифратора, коммутатор, регистр состояния, причем входы регистра состояния являются первыми входами устройства, а выходы соединены с управляющими входами коммутатора, первые выходы которого соединены с первыми выходами устройства, вторые выходы соединены с вторыми

10 выходами устройства, первые входы соединены с информационными выходами первого дешифратора микрокоманд, входы которого соединены с выходами первого регистра микрокоманд, входы

15 которого соединены с выходами первого блока памяти микрокоманд, вторые входы коммутатора соединены с информационными выходами второго дешифратора микрокоманд,входы которого

20 соединены с выходами второго регистра микрокоманд, входы которого соединены с выходами второго блока памяти микрокоманд t2j.

Недостатками этого устройства яв25ляются низкие функциональные возможности, обусловленные малой гибкостью и универсальностью его работы. Малая гибкость и универсальность работы объясняются, например, отсутствием

30 возможности обеспечить мультнпрограммную работу управляемых объектов. Кроме того, из-за слабой адаптации устройства к реализуемым программам время их выполнения завышается, что приводит к понижению эффективного быстродействия известного устройства. Цель изобретения - повышение про изводительности устройства. Поставленная цель достигается тем, что в устройство микропрограммного управления, содержащее блок выработки адреса очередной микрокомайды, два блока памяти микрокоманд, два регистра микрокоманд, два доиифратора, коммутатор, регистр со стояния, информационные входы которого являются входами кода состояний устройства, а выходы соединены управляющими входами коммутатора, первый и второй-выходы которого соединены соответственно с первым и вторым информационными выходами уст ройства, первый и второй информационные входы коммутатора соединены с первыми выходами первого и второго дешифратора соответственно, выходы первого блока памяти через первый регистр микрокоманд соединены с информационными входами первого дешиф ратора, выхо№. второго блока памяти через второй регистр микрокоманд соединены с информационными входами второго дешифратора, дополнительно введены-первый и второй регаистры адреса, три группы элементов ИЛИ, два шифратора, счетчик адреса, третий дешифратор, триггер режима, два триггера управления, N узлов хранения признака автономности, три элемента И, четыре элемента ИЛИ, N+4 группы элементов И, причем адресные входы первого блока памяти микрокоманд подключены через первый регистр адреса к выходам элементов ИЛИ первой группы, первые входы которых соединены с первым выходом блока выработки адреса очередной микрокоманды и с первыми входами элементов И первой группы, вторые входы элементов ИЛИ второй группы с выходами элементов И второй группы, а третьи входы элементов ИЛИ первой группы подключены соответственно к выходам первого шифратора, информационные входы которого соеди нены с первыми выходами N узлов хранения признака автономности и, с соответствующими входами первого эл мента ИЛИ, первый управляющий вход шифратора соединен с выходом первог элемента И, первый вход которого со единен с первыми входами элементов второйгруппы, первым входом второг элемента И, первыми входами элементов И третьей и четвертой групп и прямым выходом триггера режима, еди ничный вход которого подключен к вх ду задания режима устройства , а нулевой вход - к входу сброса устройства и к первым входам N узлов хранения признака автономности, нулевой выход триггера режима подключен к второму управляющему входу первого шифратора, к вторым входам элементов И первой группы и к первому управляющему входу второго шифратора, выходы которого соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И третьей группы, третьи входы - с выходами элементов И первой группы, а четвертые входы - с выходами элементов И четвертой группы, вторые входы которых соединены с вторыми выходами блока выработки адреса очередной -микрокоманды, выходы элементов ИЛИвторой группы через второй регистр адреса подключены к адресным входам второго блока памяти микрокоманд, вторые .. входы N узлов хранения признаков автономности соединены с информационными входами второго шифратора, соответствующими входами второго элемента ИЛИ, выход которого подключен к единичному входу первого триггера управления, второй управляющий вход второго шифратора соединен с выходом второго элемента И, второй вход которого соединен с вторым входом первого элемента И и с управляюсдам выходом третьего дешифратора,информационные входы которого соединены с третьими выходами N узлов хранения признака автономности, информационные выходы третьего дешифратора соединены с первыми входами элементов И с пятой по (.4)-ю групп, управляющий вход третьего дешифратора соединен с первым входом третьего элемента И и с вь1ходом третьего элемен-. та ИЛИ, первый, вход которого подключен к прямому выходу первого триггера управления и к первым входам элементов И третьей группы, второй вход третьего элемента ИЛИ подключен к прямому выходу второго триггера управления и вторым входам элементов И второй группы, третьи входы которых соединены с третьими входами элементов И третьей группы и с выходом счетчика адреса, счетный вход 1 оторого соединен с выходом третьего элемента И, второй вход которого является входом тактовых импульсов-устройства, управляющий вход счетчика адреса подключен к выходу четвертого элемента ИЛИ, первый вход которого соединен с управляюгдим выходом второ- го дешифратора и с нулевым входом первого триггера управления, второй вход - с управляющим выходом первого дешифратора и с нулевым входом второго триггера управления,единичный вход которого под5 лючен к выходу первого элемента ИЛИ, информационные входы счетчика адреса соединены с выходами элементов ИЛИ третьей группы, входы которых соединены с выходами элементов И от пятой до (N+4)-ft групп, вторые входы которых подключены к входам записи-кода модификации адреса устройства, первый вход блока вьфаботки адреса очередной команды является входом считывания устройства, второй вход блока выработки адреса очередной команды является входом кода операций устройства, вторые выходы первого и второго дешифраторов соединены соответственно с вторыми и третьими входами N узлов хранения признака автономности...

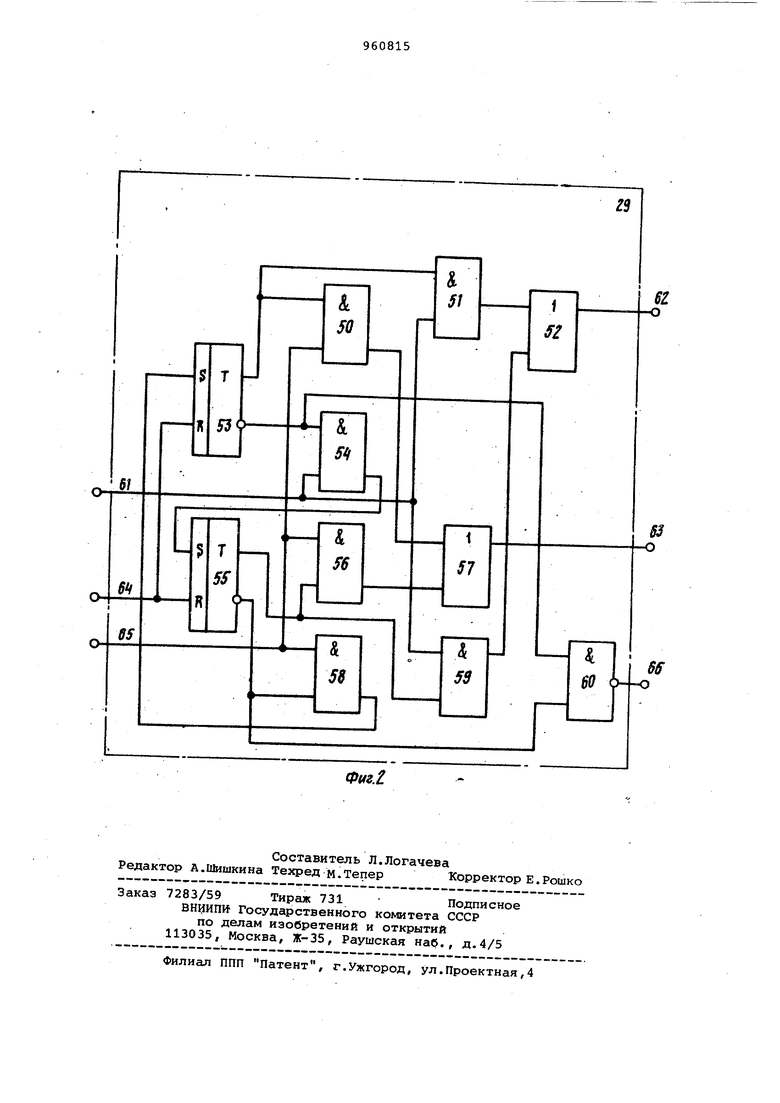

При этом каждый i-й узел хранения признака автономности (i l,..-) содержит два триггера, шесть элементов И, два элемента ИЛИ и элемент И-НЕ, причем первый вход узла соединен с нулевыми входами первого и второго триггеров, единичный выход первого триггера соединен с первыми входами первого и второго элементов И, нулевой выход - с первыми входами элемента И-НЕ и третьего элемента И, второй вход которого соединен с вторым входом узла, вторым входом второго элемента И и первым входом четвертого элементаИ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого с выходом второго элемента И, а выход является первым выходом узла, второй выход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, второй вход которого соединен с первыми входами пятого и шестого элементов И и третьим входом узла, второй вход четвертого элемента И соединен с единичным выходом первого триггера и вторым входом шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход пятого элемента И соединен с единичным входом первого триггера, выход третьего элемента И соединен с единичньзм входом второго триггера, нулевой выход которого соединен с вторыми входами пятого элемента И и элемента И-НЕ, выход которого является третьим выходом узла.

Увеличение производительности предлагаемого устройства достигается за счет работы как в однопрограммном режиме (параллельно выполняется одна программа), так и в трех новых режимах: двухпрограммном (одновременно выполняются две различные программы) двухпрограммном с увеличением эффективного быстродействия (одновременно выполняются две различные проrpaf.iJ№ii, при этом автономные микроnporpaMNtj. выполняются в двух каналах один раз);однопрограммном с увеличением эффективного быстродействия (параллельно выполняется одна про грамма, при этом каждая автономная микропрограмма выполняется один раз|.

На фиг.1 представлена функциональная схема устройства микропрограммного управления; на фиг.2 - функциональная схема узла хранения признака ав0тономности.

Устройство микропрограммного управления содержит блок 1 выработки адреса очередной микрокоманды, состоящий из регистра 2 адреса, блока

5 3 памяти, информационного регистра 4, с полем 5 задания адреса очередной микрокоманды первой программа А, полем б задания адреса очередной микрокоманды второй программы .АЗ. полем 7 задания адреса следующей адресной

0 микрокоманды, группу 8 элементов ИЛИ, регистр 9 адреса, блок 10 памяти микрокоманд, регистр 11 микрокоманд, дешифратор 12 микрокоманд, коммутатор 13, шифратор 14, элемент И 15, ре5гистр 16 состояния, (Ы+4)-ю группу 171 элементов И (i 1,...,N), группу 18 элементов ИЛИ, счетчик 19 адресов, группу 20 элементов И, группу 21 элементов И, группу 22

0 элементов И, группу 23 элементов И, . группу 24 элементов ИЛИ, регистр 25 адреса, блок 26 памяти микрокоманд, регистр 27 микрокоманд, дешифратор 28 микрокоманд, N узлов 29 хранения

5 признака автономности, дешифратор 30, элемент И 31, шифратор 32, элеj eHT И 33, элемент ИЛИ 34, триггер 35 управления, элемент ИЛИ 36, элемент ИЛИ 37, триггер 38 режима,эле0мент ИЛИ 39, триггер 40 управления, Bxojsi 41 и 42, выходы 43 и 44, выходы 45-49 устройства.

Узел 29 хранения признака автономности состоит (фиг.2) из элемен5тов И 50 и 51, элемента ИЛИ 52, триггера 5.3, элемента И 54, триггера 55, элемента И 56, элемента ИЛИ 57, элементов И 58 и 59, элемента И-НЕ 60, входа 61, выходов 62 и 63,вхо0дов 64 и 65, выхода 66.

Устройство программного управления в однопрограммном режиме работает следующим образом.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии. На входы 45 устройства поступают информационные сигналы о состоянии работоспособности функциональных узлов устройства и управляемых им объектов. При этом на выходе регистра 16 формируются соответствующие управляющие сигналы.

Пусть все функциональные узлы устройства и управляемых им объектов работоспособны. Тогда на управляющие входы коммутатора 13 подаются управляющие сигналы, обеспечивающие коммутацию первух выходов 43 коммутатора 13 и устройства с первыми входами, а вторых выходов 44 коммутатора и устройства с вторыми входами.

В блок 1 выработки адреса очередной микрокоманды через шестые входы 42 устройства подается код операции. Код операции задает начальные адреса очередны} микрокоманд первой и второй программ. Адрес очередной микрокоманды первой программы считается с первых выходов (поля 5 регистра 4) блока 1 выработки адреса очередноТй микрокоманды, адрес очередной микрокоманды второй программы с вторых выходов (поля 6 регистра 4) того же блока. Адрес очередной микрокоманды первой программы поступает через первую групп 8 элементов ИЛИ на первый регистр 9, а через четвертую группу 21 элементов И (на первые входы с вторых выходов триггера 38 режима поступает в однопрограммном режиме разрешающий сигнал) и вторую группу 24 элементов ИЛИ на второй регистр 25. Так как в однопрограммном режиме работы устройства на первом-выходе триггера 38 режима сигнал не формируется, то через первую группу 20 элементов И, третью группу 22 элементов.И, вторую группу 23 элементов. И, опервый элемент И 15 и второй элемент И 31 коммутация не производится. Следовательно, на вторые и третьи входы первой группы 8 элементов ИЛИ и на вторые, третьи и четвертые входы второй группы 24 элементов ИЛИ сигналы не поступают.

Адреса сформированных в регистрах 9 и 25 выполняемых очередных микрокоманд поступают соответственно на первый и второй блоки 10 и 26 памяти микрокоманд. В соответствии с адресами выполняемых очередных микрокоманд из первого и второго блоков 10 и 26 выбираются выполняемые микрокоманды первой програмNw, которые поступают соответственно на первый и второй регистры 11 и

27микрокоманд. Далее сигналы с первого и второго регистров 11 и 27 микрокЪманд считываются соответственно на первый и второй дешифраторы 12 и

28микрокоманд, с информационных выходов которых .через ком1 татор 13 сигналы подаются соответственно на первый и второй выходы 43 и 44 устройства. Таким образом, последовательность микрокоманд первой программы поступает .на выходы 43 и 44 устройства, обеспечивает работу соответствующих объектов управления (операционных блоков, например).

в случае необходимости подачи последовательности микрокоманд первой программы только на первые выходы 43 устройства или только на вторые выходы 44 устройства изменяют код состояния работоспособности функциональных узлов устройства и управляемых им объектов, подаваемый на первые входы 45 устройства. При этом на выходах регистра 16 формируются сигналы, обеспечивающие соответствующую коммутацию в коммутаторе 13. После считывания первой микрокоманды i-й автономной микропрограммы из первого и второго блоков 10

5 и 26 памяти микрокоманд на информационных выходах первого и второго дешифраторов 12 и 28 микрокоманд в i-OM разряде поля признака автономности считывается единица. В соответствии с этим на второй и третий входы 61 и 65 i-ro узла 29 хранения признака автономности поступают сигналы, по которым через элементы И 54 и 58 осуществляется установка в единичное состояние триггеров 53 и 55. Если затем в ходе выполнения программ устройство вновь переходит к реализации i-й автономной микропрограммы, то на входы 61 и 65 узпа 29i

Q поступают сигналы, которые проходят через элементы И 51, ИЛИ 52 и И 56, . ИЛИ 57 на выходы 62 и- 63. Сигналы с этих выходов проходят на i-e информационные .входы шифраторов 14 и 32

с соответственно, которые выдают коды модификации адреса второго вида. В результате на регистрах 9 и 25 сформируются адреса очередных микрокоманд, которые определяют .адреса начальных микрокоманд, следующих за

i-й автономной микропрограммой. Следовательно, повторное выполнение ранее встречающейся автономной микропрограммы не происходит, что ускоряет реализацию всей программы в

5 целом. Далее устройство в этом режиме продолжает функционировать аналогично описанному. Если в процессе функционирования выходит из строя один из узлов устройства или управляемого блока, что фиксируется регистром 16, то на выходах коммутатора 13 формируются сигналы, которые блокируют прохождение микрокоманд от отказавшего канала или к отказавшему блоку.

Рассмотрим работу устройства в двухпрограммном режиме.

В этом случае каждый из каналов микропрограммного управления реали0 - зует свою программу. Двухпрограммному режиму соответствует единичное состояние триггера 38,режима, На вход 42 поступает код операции, по которому блок выработки адреса

5 очередной микрокоманды формирует последовательности адресов микрокоманд двух nporpaNiM. Адреса проходят через блок 8 элементов ПЛИ и блоки 23 элементов И, открытых единичным сигналом с первого выхода триггера 38 и элементов ИЛИ 24, в регистры 9 и 25 соответственно. В соответствии с указанными адресами считываются последовательности микрокоманд, которые поступают на выходы 43 и 44 для управления двумя блоками. Таким образом, работа продолжается до тех пор, пока в одном из каналов не сосчитается первая микрокоманда i-й автономной микропрограммы. При этом дешифратор 12(28) формирует сигнал, которыйпоступает на вход 61 (65)i-ro узла 291 хранения признака автономности и через элемент И 54 (И 56) устанавливает триггер 55(53) в единичное состояние, запоминаятем самым факт выполнения i-й автономной микропрограммы. Затем работа устройства продолжается аналогично описанному и в узлах 29 запоминаются номера автономных микропрограмм, выполненных любым из каналов. Если после считывания очередной микрокоманды во втором (йервом) канале оказывается, что эта микрокоманда является началь ной в i-й автономной микропрограмме, тс на соответствующем выходе дешифра тора 28(12) появляется сигнал, который поступает на вход 65(61) узла 291 , Этот сигнал проходит через открытый элемент И 56 (И 51) и элемент OTi 57 (ИЛИ 52) на выход 63 (62) узJifi 29. Далее по этому сигналу через элемент ИЛИ 34 (ИЛИ 39) устанавливается в единичное с&стояние триггер 35 (40) управления. Шифратором 32 (14) код модификации при этом не вырабатывается, поскольку на обоих управляющих входах присутствуют нулевы сигналы. Единичный сигнал с выхода элемента ИЛИ 36 открывает элемент И 133 и дешифратор 30, а сигнал с перво го выхода триггера 35(40) открывает ,блок 22 элементов И (И 20). Дешифратор 30 в соответствии с кодом о выполненных автономных микро програГТмах, формируемым на выходах 66 узлов 291 , открывает соответствую щий блок 17j элементов И, разрешая написать в счетчик 19 начального кода модификации адреса первого вида. Этот код проходит затем через блок 22 элементов И (И 20) и блок 24 злементов ИЛИ (ИЛИ 8) в регистр 25 (9) , определяя начальный адрес одной из невыполненных ранее автономных микропрограмм. Последующие адреса формируются счетчиком 19 по импул caMv. проходящим со входа 47 через элемент И 33. Таким образом, второй первый ) канал реализует вместо выполненной ранее 1-й автономной микропрограммы j-ю автономную микропрограмму (j 1, N; j 1),. сокращая тем самым общее время выполнения программ. После окончания j-й автономной микропрограммы сигналом с выхода дешифратора 28(12) обнуляется триггер 35(40) и через элемент ИЛИ 37 устанавливается в исходное состояние счетчик 19. Работа устройства далее продолжается как описано выше до тех пор, пока однократно не будут выполнены все автономные микропрограммы. При этом на выходах 66 всех узлов 291 устанавливаются единичные сигналы. В результате на единичном выходе дешифратора 30 сформируется единичный сигнал, который, проходя через элементы И 15 и И 31, разрешает формирование шифраторами 14 и 32 кодов модификации адреса второго вида. Если после этого в одном из каналов необходимо вновь выполнить одну из автономных микропрограмм, то по сигналу с соответствующего выхода одного из узлов 29 хранения признака автономности шифратор 14 или 32 сформирует коды модификации с целью обхода выполненной автономной микропрограммы. При этом повышение эффективности . предлагаемого устройства по сравнению с известным характеризуется,например, увеличением производительности. Указанная величина повышения производительности работы устройства может достичь величины: для однопрограммного режима - в Q 1,24 раза; для двухпрограммного режима в Q 1/54 раза. Формула изобретения 1. Устройство микропрограммного управления, содержащее блок вырабо.тки адреса очередной микрокоманды, два блока памяти микрокоманд, два регистра микрокоманд, два дешифратора, коммутатор, регистр состояния, информационные входы которого являются входами кода состояний устройства, а выходы соединены с управ ляющими входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым информационными выходами устройства, первый и второй информационные входы коммутатора соединены с первыми выходами первого-и второго дешифраторов соответственно, выходы первого блока памяти через первый регистр микрокоманд соединены с информационными входами первого дешифратора, выходы второго блока памяти через второй регистр микрокоманд .соединены с информационными входами второго дешифратора, отличающееся тем, что, с целью повышения производительности устройства, оно дополнительно содержит первый и второй регистры адреса, три группы элементов ИЛИ, два шифратора, счетчик адреса, третий дешифратор, триггер режима, два триггера управления,N узлов хранения признака автономности, три элемента И, четыре элемента ИЛИ, N+4 группы элементов И, причем адресные входы первого блока памяти микрокоманд подключены через первый регистр адреса к выходам элементов ИЛИ первой группы, первые входы которых соединены с первым выходом блока выработки адреса очередной микрокоманды и с пер выми входами элементов И первой группы, вторые ВХОДЫ элементов ИЛИ второй группы - с выходами элементов И второй группы, а .третьи входы элементов ИЛИ первой группы подключены соот ветственно к выходам первого шифратора, информационные входы которого соединены с первыми выходами N узлов хранения признака автономности и с соответствующими входами первого -элемента ИЛИ, первый управляющий вход шифратора соединен с выходом первого элемента И, первый вход которого соединен с первыми входами элементов И второй группы, первым входом второго элемента И, первыми входами элементов И третьей и четвертой групп и пря№ам выходом триггера режима, единичный вход которого подключен к входу задания режима устройства, а нулевой вход к входу сброса устройства и к первым входам N узлов хранения признака авто номности , нулевой выход триггера режи ма подключен к второму управляющему входу первого шифратора, к вторым вхо дам элементов И первой группы и к пер вому управляющему входу второго шифра тора, выходы которого соединены с пер выми входами элементов ИЛИ второй гру пы, вторые входы которых соединены с выходами элементов И третьей группы, третьи входы - с выходами элементов И первой группы, а четвертые входы - с выходами элементов И четвертой группы, вторые входы которых соединены с вторыми выходами блока выработки адре са очередной микрокоманды, выходы эле ментов ИЛИ второй группы через второй регистр адреса подключены к адресным входам второго блока памяти микрокоманд, вторые выходы N узлов хранения признаков автономности соединены информационными входами второго шифра тора, соответствующими входами второго; элемента ИЛИ,выходкоторого подключен к единичному входу первого тpиггepaJ управления, второй управляю11Ц{й вход второго шифратора соединен с выходом второго элемента И, второй вход кото(Pofo соединен с вторым входом пер-. вого элемента И и с управляющим выходом третьего-дешифратора, информационные входы которого соединены с третьими выходами узлов хранения признака автономности, информационные выходы третьего дешифратора соединены с первыми входами элементов И с пятой по CN+4)-ю групп, управляющий вход третьего дешифратора соединен с первым входом третьего элемента И и с выходом третьего элемента ИЛИ, первый вход которого подключен к прямому выходу первого триггера управления и к первым входам элементов И третьей группы, второй вход третьего элемента ИЛИ подключен к прямому выходу второго триггера управления и вторым входам элементов И второй группы, третьи входы которых соединены с третьими входами элементов И третьей группы и с выходом счетчика адреса, счетный вход которого соединен с выходом третьего элемента И, второй вход которого является входом тактовых импульсов устройства, управляющий вход счетчика адреса подключен к выходу четвертого элемента ИЛИ, первый вход которого соединен с управляющим выходом второго дешифратора и с нулевым входом первого триггера управления, второй вход с управляющим выходом первого дешифратора и с нулевым входом второго триггера управления, единичный вход которого подключен к выходу первого элемента ИЛИ, информшдионныа входы счетчика адреса соединены с выхоцаг«я-г элементов ИЛИ третьей группы, входы которых соединены с выходш-м элементов И от пятой до (N+4)-ft групп, вторые входы которых подключены к входам записи кода модификации адреса устройства, первый вход блока выработки адреса очередной команды является входом считывания устройства, второй вход блока выработки адреса очередной команды является входом кода операцк. устройства, вторые выходы первого к второго дешифраторов соединены соответственно с вторыми и третьими входами N узлов хранения признака автономности . 2. Устройство по п.1, отличающееся тем, что каждый i-й узел хранения признака автономности (i 1,...,Nj содержит два триггера, шесть элементов И, два элемента ИЛИ и элемент И-НЕ, причем первый вход узла соединен с нулевыми входами первого и второго триггеров, единичный выход первого триггера соединен с первым входом первого и второго элементов И, нулевой выход с первыми входами элемента И-НЕ и третьего элемента И, второй вход которого соединен с вторым входом узла, вторым входом второго элемента И и первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход

которого соединен с выходом второго элемента И, а выход является первым-выходом узла, второй выход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, второй вход которого соединен с первыми входами пятого и шестого элементов И и третьим входом узла, второй; вход четвертого элемента И соединен с единичным выходом первого триггера и вто рым входом шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход пятого элемента И соединен с единичным входом .

первого триггера, выход третьего элемента И соединен с единичным входом второго триггера, нулевой выход которого соединен с вторыми входами пятого элемента И и элемента И-НЕ, выхо которого является третьим выходом узла.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-23—Публикация

1981-02-09—Подача