торого соединен с информационным входом блока кодоуправляемых резисторов, пятый выход дешифратора подключен к стробирующему входу блока кодоуправляемых резисторов, к входу разрешения счета первого счетчика и к счетному входу третьего счетчика выход цифроаналогового преобразовате ля подключен к входу блока умножителей, .выход которого соединен с группой граничных узлов R-сетки, выход коммутатора через блок задания нелинейности типа экспоненты подключен к информационному входу блока умножения, выход которого соединен с информационным входом аналого-цифрового преобразователя и с первым выводом токозадающего резистора, второй вывод которого соединен с шиной нулевого потенциала, которая соединена с второй группой выводов блока кодоуправляемых резисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1229780A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1164747A1 |

| Устройство для решения нелинейных задач теплопроводности | 1986 |

|

SU1363269A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Многоканальное тензометрическое устройство | 1986 |

|

SU1434240A1 |

| Устройство для определения отношения двух напряжений | 1983 |

|

SU1151994A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ НЕЛИНЕЙНЬЩ ЗАДАЧ ТЕОРИИ ПОЛЯ, содержащее коммутатор, цифроаналоговый преобразователь, блок кодоуправляеMbtx резисторов, R-сетку, группа граничных узлов которой соединена с группой информационных входов коммутатора и с первой группой выводов блока кодоуправляемых резисторов, отличающееся тем, что, с целью повышения быстродействия, в неговведены блок умножителей, блок умножения, блок памяти, аналого-цифровой преобразователь, блок задания нелинейности типа экспоненты, токозадающий резистор и блок управления, состоящий из четырех счетчиков, двух регистров, дешифратора, двух блоков сравнения, элемента И, элемента ИЛИ, элемента задержки, триггера и генератора тактовых импульсов, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходом триггера, первый установочный вход которого соединен с выходом элемента ИЛИ, первый вход которого является входом запуска устройства, выход элемента И подключен к счетному входу первого счетчика, группа выходов которого подключена к группе входов дешифратора, первый выход которого соединен с входом записи блока памяти, группа информационных входов которого подключена к группе выходов второго счетчика, счетный вход которого соединен с выходом первого блока сравнения, первый вход которого соединен с выходом первого регистра, второй выход дешифратора соединен со стробирующими входами блока умножителей, блока умножения и цифроаналогового преобразователя, информационный вход которого соединен с пер(Л вым выходом блока памяти, второй выход которого соединен с информационными входами блока умножителей, блока умножения, третий выход дешифратора подключен к стробирующему входу коммутатора, кодовый адресный вход которого соединен с выходом третьего счетчика и с первым входом ел второго блока сравнения, выход кото05 рого подключен к входам записи кода блока умножителей, блока-умножения, цифроаналогового преобразователя, блока кодоуправляемых peзиctopoв, к счетному входу четвертого счетчика, к второму установочному входу триггера и через элемент задержки к второму входу элемента ИЛИ, выход четвертого счетчика соединен с вторым входом первого блока сравнения, выход второго регистра подключен к второму входу второго блока сравнения, четвертый выход дешифратора соединен с управляющим входом аналогоцифрового преобразователя, выход ко

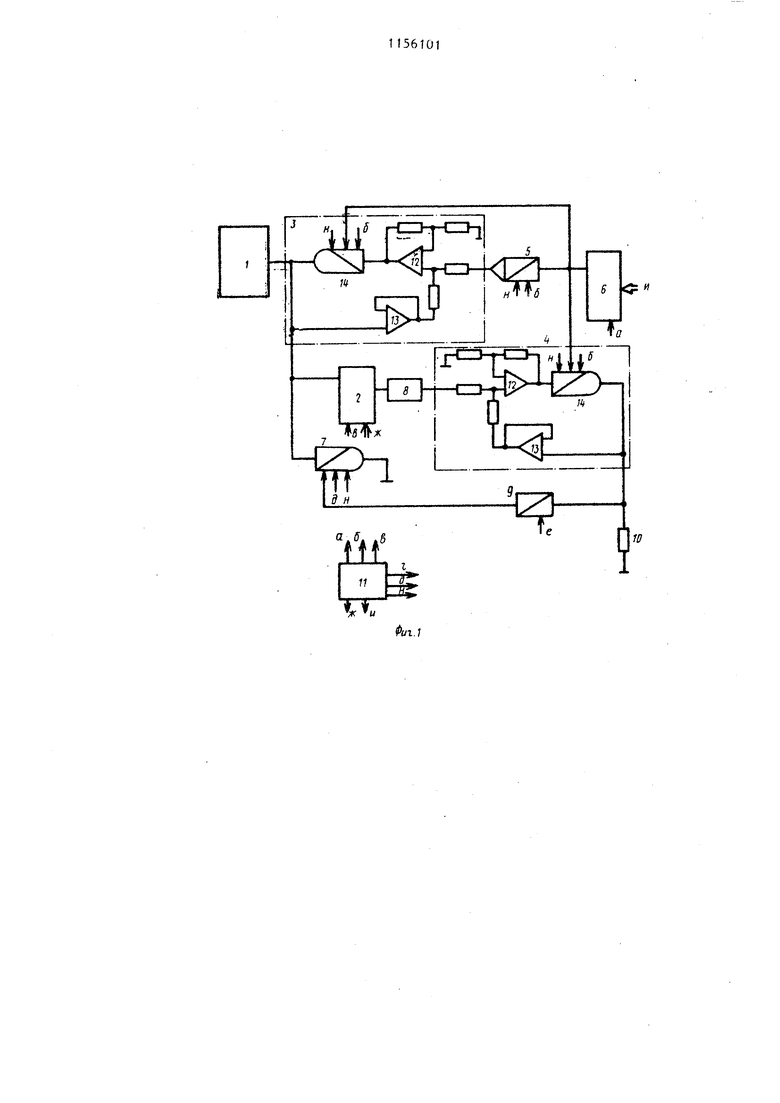

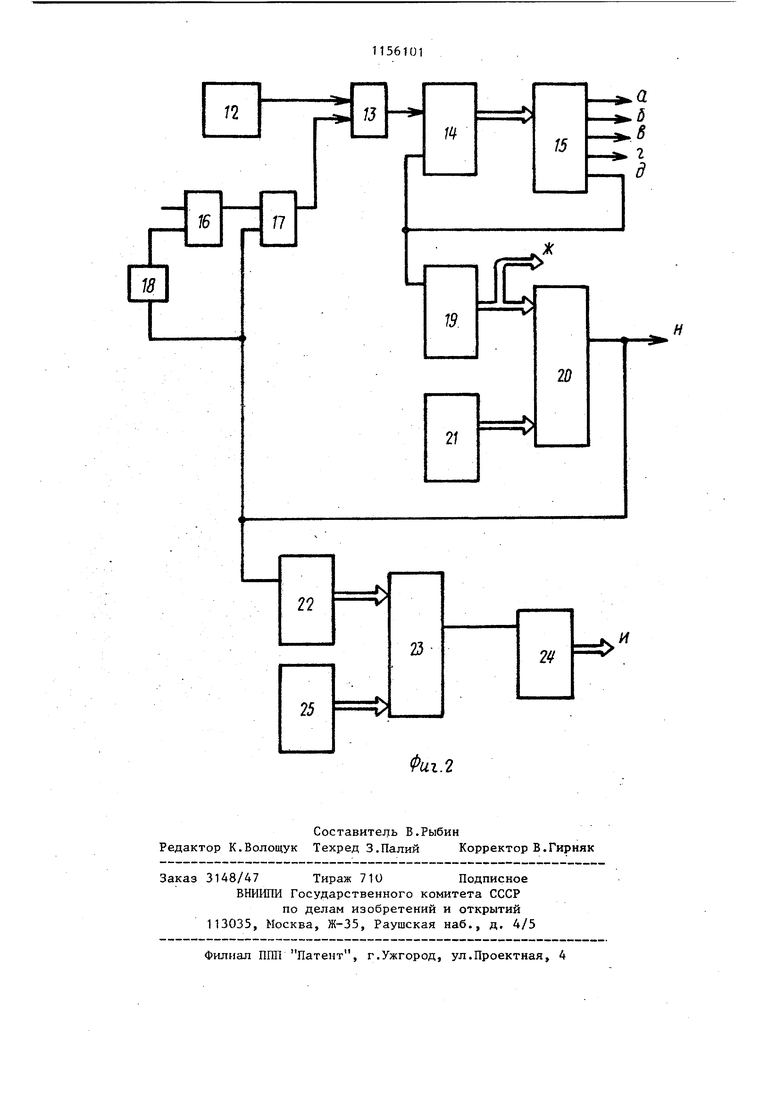

Изобретение относится к вычислительной технике -к предназначено для решения нелинейньк задач теории пол в частности, нелинейных задач тепло проводности. Моделирование нелинейных перемен ных: во времени граничных условий III р да й(()-Ит) может быть осуществлено путем итера тивного изменения параметров аналогового процессора, если в алгоритм работы устройства заложен метод Либ мана или его несколько измененный вариант. Граничные условия в виде (1) или в виде Г2) получающемся после применения подст новок, например, преобразования Кирхгофа е-5 Мт)сЛТ, могут быть реапизованы традиционным путями с помощью аналоговых устройств. Цель изобретения - повьшение быстродействия. На фиг. 1 представлена блок-схем устройства; на фиг. 2 - блок-схема блока управления. Устройство содержит R-сетку 1, коммутатор 2, блок 3 умножителей, блок 4 умножения, цифроаналоговый преобразователь 5, блок 6 памяти, блок 7 кодоуправляемых резисторов, блок 8 задания нелинейности типа экспоненты, аналого-цифровой преобразователь 9, токозадающий резистор 10, блок 11 управления. Блок 11 управления содержит генератор 12 тактовых импульсов, элемент И 13, счетчик 14, дешифратор 15, элемент ИЛИ 16, триггер 17, элемент задержки 18, счетчик 19, блок 20 сравнения, регистр 21, счетчик 22, блок 23 сравнения, счетчик 24, регистр 25. Устройство работает следующим образом. После ввода исходных данных в блок 6 памяти (эта информация заносится перед решением задачи из вычислительной системы, которая на чертеже не изображена), в который заносится значение функций ((t) и Тр (t) для каждого шага во времени, и набора функции в блок 8, по сигналам из блока 11 управления считывается значение oCCt) из блока 6 памяти и поступает на цифровые входы блоков 3 и 4, значения Т записываются в ЦАП 5. В результате на выходе блока 3 формируется ток, пропорциональный произведению , который поступает в граничный узел R-сетки 1. После задания токов во все граничные узлы R-сетки на ней формируется решение, которое соответствует первому приближению. 6 Для получения второго приближенного решения на данном временном 3 шаге из блока 11 упрапления поступают сигналы, которые включают коммутатор 2, подключающий граничный узел R-сетки к блоку 8, который в зависимости от величины потенциала, пропорционального В, формирует значение функции TtOVt. В результате на входе аналого-цифрового преобразователя 9 поступает потенциал, пропорциональный (6)/Q. После преобразования аналогового потенциа ла с(Т(©)/0 в цифровой код АЦП 9 дискретная информация о потенциале записывается в буферный регистр бло ка 7, где она запоминается. Коммутатор 2 продолжает обход всех граничных точек, для которых производится запись корректируемых параметров в соответствующие им кодоуправляемые проводимости блока 7. По окончании этого процесса из блока 11 управления поступает сигнал в блок 7, т.е. происходит запись информации из буферных регистров блока 7 в их вторые регистры. В результате в узлы R-сетки 1 подается ток, пропорциональный выражению (2) Таким образом, цифровой процессор не участвует в итерационном процессе, что существенно сокращает время рещения задачи. Блок 11 управления работает следующим образом. Перед началом решения задачи про исходит сброс информации в счетчиках 14, 19, 22 и 24, в триггере 17 и регистрах 21 и 25. Затем с помощью клавиишого регистра задаются количество узловых точек R-сетки в регистр 21 и количество итераций необходимых для получения решения на временном шаге в регистр 25. После этого дается команда Пуск, п которой на выходе схемы ИЛИ 16 формируется импульс, устанавливающий триггер 17 в единичное состояние, которое разрешает прохождение импульсов с генератора 12. На счетчике 14 устанавливается последовател ность кодов, которые подаются на дешифратор 15. На выходах дешифрат ра 15 формируется последовательнос микрокоманд, разрешающих считывани информации из блока 6 памяти, согласно адресу, сформированному на выходе счетчика 24. Следующая микр 14 команда разрешает запись в буферные регистры блока 7 блоков 3, 4 и в буферный регистр ЦДЛ 5, очередная микрокоманда производит пуск коммутатора 2, который подключает узловую точку к входу блока 8 по адресу, сформированному на выходе счетчика 19. После этого следующая микрокоманда с вьЕхода дешифратора 15 разрешает аналого-цифровому преобразователю 9 произвести преобразование аналоговой информации в дискретную, которая записывается в буферный регистр блока 7 по следующей микрокоманде с дешифратора 15, по которой также осуществляется сброс счетчика 14. Очередной импульс с генератора 1 начинает повторять обработку следующей узловой точки, адрес которой формируется на счетчике 19 по этому же сигналу. Этот процесс повторяется до тех пор, пока не будет записана вся информация во все буферные регистры блока 7, о чем свидетельствует импульс, появляющийся на выходе блока 20 сравнения, по которому происходит одновременная запись информации из буферных регистров блока 7 в их вторые регистры, в результате чего происходит преобразование цифровой информации в аналоговую и на R-сетке 1 формируется решение для данной итерации. Во время формирования решения импульсы с генератора 1 не поступают на вход счетчика 14, так как элемент И 13 запирается потенциалом с триггера 17, управление которым производится импульсом с выхода блока 20 сравнения, поступающего также на счетчик 22. Этот же импульс с помощью элемента 18 задержки разрешает прохождение очередной серии импульсов с генератора 1. С этого момента начинается очередная итерация. . Таким образом, итерационный процесс осуществляется до тех пор, пока на выходе блока 23 сравнения не сформируется импульс, свидетельствующий об окончании итерационного процесса на временном шаге. Этот импульс поступает на счетчик 24, на котором формируется код, являющийся адресом для блока 6 памяти.

«

w

И

23

2

| Устройство для моделирования теплопроводности | 1974 |

|

SU492890A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для моделирования теплопроводности | 1974 |

|

SU491963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-03-15—Подача