проводимостей и граничных узловых точек по координатам X, Y, аналоговые входы и выходы 25 второй группы для связи граничных узловых точек и граничных проводимостей по координате Z, информационные входы 26 и выходы 27 третьей, адресные входы 28 четвертой группы узлов вычисления истемы конечно-разностных уравнений, выходы 29 - 32 распределителя 12

импульсов. Достижение поставленной цели обеспечено благодаря введению в устройство блоков памяти коммутаторов памяти, контроллеров шин, дешифраторов адреса, распределителей импульсов, переключателей локальных общих шин и аналого-цифровых преобразователей, а также новым связям между составными блоками устройства. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения краевых задач теории поля | 1985 |

|

SU1265813A1 |

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1383391A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство для отслеживания контуров двумерных объектов | 1986 |

|

SU1314353A1 |

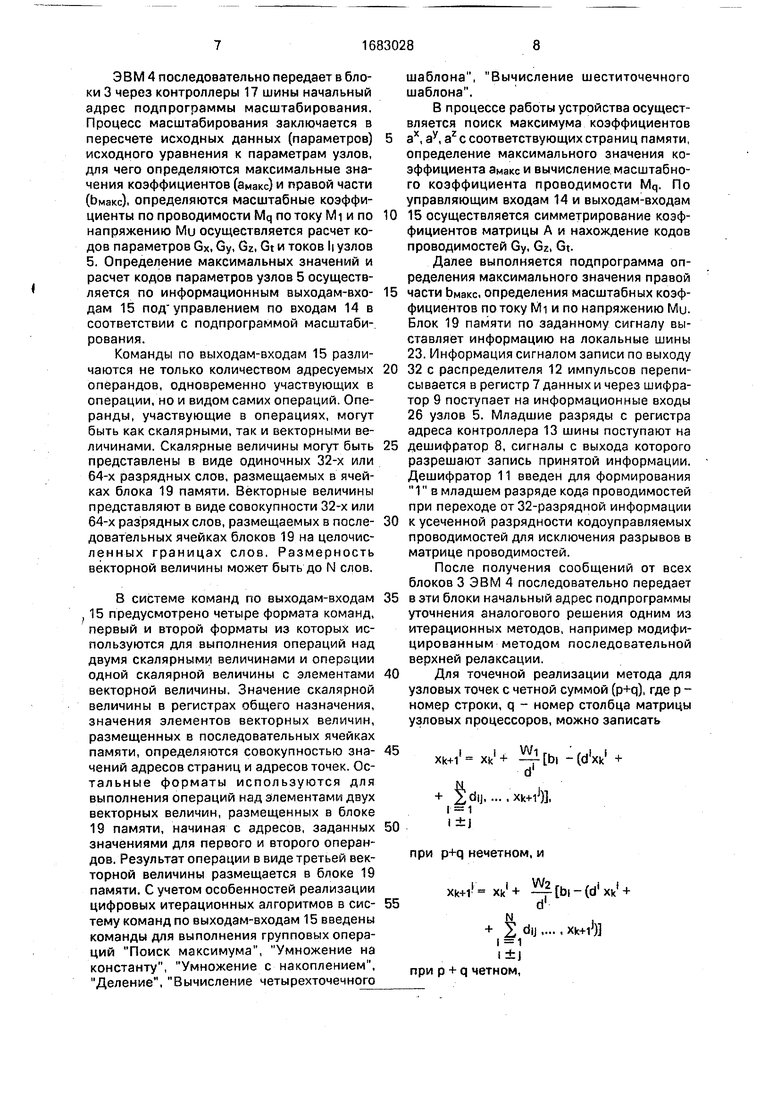

Изобретение относится к аналоговой вычислительной технике и может быть применено для решения краевых задач, описываемых дифференциальными уравнениями в частных производных с функциональными и нелинейными зависимостями коэффициентов, методами дискретного моделирования. Целью изобретения является повышение быстродействия устройства Устройство содержит регистр 1 конфигурации, коммутатор 2, матрицу блоков 3 решения уравнений системы, внешнюю электронно- вычислительную машину (ЭВМ) 4. Каждый блок 3 содержит узел 5 вычисления системы конечно-разностных уравнений, блок 6 коммутации, регистр 7 данных, дешифратор 8 адреса, шифратор 9, аналого-цифровой преобразователь 10, дешифратор 11 команд, шифратор команд, распределитель 12 импульсов, первый контроллер 13 шины, управляющие входы 14, информационные выходы-входы 15, третий контроллер 16 шины (с магистралью X, Y), второй контроллер .17 шины, коммутатор 18 памяти, блок 19 памяти, переключатель 20 локальных общих шин, первую общую шину 21, вторую общую шину 22, первую, вторую и третью локальные магистрали 231, 232 и 23з, входы-выходы 24 первой группы для связи граничных 2И 25 иигжм

Изобретение относится к аналоговой вычислительной технике и может быть применено для решения краевых задач, описываемых дифференциальными уравнениями в частных производных с функциональными и нелинейными зависимостями коэффициентов, методами дискретного моделирования.

Целью изобретения является повышение быстродействия устройства.

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1 конфигурации, коммутатор 2, матрицу блоков 3 решения уравнений системы, внешнюю электронно-вычислительную машину (ЭВМ) 4. Каждый блок 3 содержит узел 5 вычисления системы конечно-разностных уравнений, блок 6 коммутации, регистр 7 данных, дешифратор 8 адреса, шифратор 9, аналого- цифровой преобразователь 10, дешифратор команд 11, распределитель 12 импульсов, первый контроллер 13 шины, управляющие входы 14, информационные выходы-входы 15, третий контроллер 16 шины (с магистралью X, Y), второй контроллер 17 шины, коммутатор 18 памяти, блок 19 памяти, переключатель 20 локальных общих шин, первую общую шину 21, вторую общую шину 22, первую, вторую и третью локальные общие шины соответственно 231, 232 и 23з, входы- выходы первой группы 24 для связи граничных проводимостей и граничных узловых точек по координатам X, Y, аналоговые входы и выходы 25 второй группы для связи граничных узловых точек и граничных проводимостей по координате Z, информацион- ные входы 26 и выходы 27 третьей, адресные входы 28 четвертой группы узлов вычисления системы конечно-разностных уравнений, выходы 29 - 32 распределителя 12 импульсов, соединенные по приведенной схеме.

Сложная краевая задача, описываемая дифференциальным уравнением в частных производных второго порядка в одномерных, двумерных и трехмерных областях про- 5 извольный конфигурации вида:

10

20

25

5(Уч

8V

V EL /G -2JJ-N Q + Р +

Эх, Г эх,/ u + p +at

где (Г- искомая функция;

xi - координаты пространства; t- время;

G, Q, Р, Т- коэффициенты уравнений, -с с начальными условиями

a (xi, о) fi (xi),

с граничными условиями вида

317 |

где

(X,,t),

(x,,a,t), (xi,o:t).

сводится известными методами дискрет-, зации (например, методом сеток) и решению ряда систем конечно-разностных уравнений вида АХ В, при этом вместо

3Q функций непрерывного аргумента рассматриваются функции дискретного аргумента, граничные условия заменяются разностными производными. Функция временного аргумента разбивается на ряд дискретных

35 временных шагов, внутри каждого временного шага итерационными методами учитываю ся нелинейные зависимости коэффициентов исходного уравнения.

Для каждого узлового процессора ко4Q нечно-разностные уравнения имеют вид

Cf. Х- .. + сЈ: -X:... a.: -

зом.

-V2 «-WaM.iz «+1 И . J-1- }

мч-Г i,4-f QlW Лм,e;Устройство работает следующим обра- 45 „ Л . , - g. .

i,)it iii4

Сложная краевая задача, описываемая дифференциальным уравнением в частных производных второго порядка в одномерных, двумерных и трехмерных областях про- извольный конфигурации вида:

5(Уч

8V

V EL /G -2JJ-N Q + Р +

Эх, Г эх,/ u + p +at

где (Г- искомая функция;

xi - координаты пространства; t- время;

G, Q, Р, Т- коэффициенты уравнений, с начальными условиями

a (xi, о) fi (xi),

с граничными условиями вида

20

317 |

(X,,t),

где

(x,,a,t), (xi,o:t).

сводится известными методами дискрет-, зации (например, методом сеток) и решению ряда систем конечно-разностных уравнений вида АХ В, при этом вместо

функций непрерывного аргумента рассматриваются функции дискретного аргумента, граничные условия заменяются разностными производными. Функция временного аргумента разбивается на ряд дискретных

временных шагов, внутри каждого временного шага итерационными методами учитываю ся нелинейные зависимости коэффициентов исходного уравнения.

Для каждого узлового процессора конечно-разностные уравнения имеют вид

Cf. Х- .. + сЈ: -X:... a.: -

-V2 «-WaM.iz «+1 И . J-1- }

где ах, ау, аг - соответствующие коэффициенты саязи между узловыми точками по координатам X и Y, сеточного шаблона соответственно

b,,j I в случае граничных условий I сюда;

Јг в случае граничных условий И рода ;

п а, ;,Ј в случае граничных условий 111 рода;

Ь;,) 0. в случае моделирования временной производной по методу Либмана;

ch,j,w диагональный элемент, пред- став/К Ощий сумму коэффициентов ах, ау, az, т в счучае граничных условий III рода или временной производной и диагонального преобладания а1.

Блок-схема программы организации вычислительного процесса в устройстве содержит блоки занесения исходных данных в решающие блоки, установки конфигурации области, масштабирования, занесения информации в матрицу узловых процессоров, съема решения и демасштабирования, уточнения решения, учета нелинейности, пыдачи решения из решающих блоков в ЭВМ,

Из ЭВМ 4 через общие шины 21 и 22 и блоки связи с ЭВМ в блоки 19 памяти матрицы блоков 3 решения уравнений системы записывается программа работы устройства в исходные данные системы конечно-разностных уравнений АХ В. Для каждого коэффициента ах, ау, a7, b, d в блоке 19 памяти отведена определенная страница памяти, длина которой равна 4N байтов, где N - число узлов процессоров в матрице решающего блока 3. Процесс передачи данных и программ из ЭВМ 4 в блок 19 памяти осуществляется через контроллер 17 шины, представляющий собой скоростной канал связи, состоящий из двух однотипных интерфейсных узлов (не показаны). Последние имеют независимое управление со стороны входа 14 управления и ЭВМ 4 соответственно в процессе пословного или блочного обмена информацией между ними.

Процесс обмена информацией между ЭВМ 4 и входами 14 управления строится по принципу запрос-ответ, т.е. в любом обмене информацией существует процессор- инициатор обмена и процессор-абонент.

При передаче данных ЭВМ 4 производит загрузку адресуемых регистров контроллера 17 шины со стороны общей шины 21, причем в регистры начального и конечного адресов контроллера засылаются коды начального и конечного адресов Ак передаваемого блока данных. В регистр команд и состояния контроллера заносится код команды, разрешения прерывания и разряд пуска. Выборка регистров осуществляется кодом адреса на общей шине 21.

Программа работы устройства состоит из сменных подпрограмм, реализующих определенные блоки алгоритма работы устройства, загрузка которых в блоки 19 памяти блоков 3 производится аналогично. Организация взаимодействия между

ЭВМ 4 и блоками 3 осуществляется путем передачи адреса подпрограммы, вызываемой в блоках 3.

ЭВМ 4 последовательно передает в контроллер 17 шины начальный адрес подпрограммы и код команды записи одиночного слова. Аналогично ЭВМ 4 осуществляет запуск остальных блоков 3.

Длл установки конфигурации области осуществляется программная настройка

блоков 3 устройства для решения конкретной краевой задачи. Из ЭВМ 4 в регистр 1 конфигурации выдается код тороидальной базовой области. Из регистра 1 этот код выдается на коммутатор 2, который осуществляет коммутацию границ матрицы узлов 5 блоков 3 по координатам X, Y, образуя необходимую конфигурацию моделирую- шей базовой области в плоскости X, Y. По координате Z координатные проводимости

gz узлов 5 блоков 3 через входы-выходы 25 соединены последовательно в кольцо. Кроме того, осуществляется программная настройка контроллера 16 шины.

Контроллер 16 шины представляет собой программно настраиваемый блок, предназначенный для сопряжения данного блока 3 с общей шиной 22, которая содержит линию связи, объединяющую между собой блоки контроллера 16 шины всех блоков 3, и включает в себя набор линий управления. Контроллер 16 шины обеспечивает выдачу заявок на общую шину 22 для чтения информации из соседних блоков 3, прием и

передачу данных с общей шины 22 на шины данных локальных общих шин 23, чтение и выдачу данных из блока 19 памяти своего узла 5 на шины данных по заявкам блоков 3. Для обеспечения связи блока 3 с другими в

составе контроллера 16 шины имеется блок памяти реконфигурации, предназначенный для хранения значений номеров соседних блоков 3 в области моделирования краевой задачи, расположенных слева и справа по

координате X, а также снизу и сверху по координате Y соответственно. Кроме того, блок памяти реконфигурации обеспечивает хранение номеров соседних блоков 3 по отношению к резервируемому решающему блоку 3 по координате Z.

ЭВМ 4 последовательно передает в блоки 3 через контроллеры 17 шины начальный адрес подпрограммы масштабирования. Процесс масштабирования заключается в пересчете исходных данных (параметров) исходного уравнения к параметрам узлов, для чего определяются максимальные значения коэффициентов (амакс) и правой части (Ьмакс), определяются масштабные коэффициенты по проводимости Mq потоку MI и по напряжению Ми осуществляется расчет кодов параметров Gx, Gy, Gz, Gt и токов li узлов 5. Определение максимальных значений и расчет кодов параметров узлов 5 осуществляется по информационным выходам-входам 15 под управлением по входам 14 в соответствии с подпрограммой масштабирования.

Команды по выходам-входам 15 различаются не только количеством адресуемых операндов, одновременно участвующих в операции, но и видом самих операций. Операнды, участвующие в операциях, могут быть как скалярными, так и векторными величинами. Скалярные величины могут быть представлены в виде одиночных 32-х или 64-х разрядных слов, размещаемых в ячейках блока 19 памяти. Векторные величины представляют в виде совокупности 32-х или 64-х разрядных слов, размещаемых в последовательных ячейках блоков 19 на целочисленных границах слов, Размерность векторной величины может быть до N слов.

В системе команд по выходам-входам } 15 предусмотрено четыре формата команд, первый и второй форматы из которых используются для выполнения операций над двумя скалярными величинами и операции одной скалярной величины с элементами векторной величины. Значение скалярной величины в регистрах общего назначения, значения элементов векторных величин, размещенных в последовательных ячейках памяти, определяются совокупностью значений адресов страниц и адресов точек. Ос- тальные форматы используются для выполнения операций над элементами двух векторных величин, размещенных в блоке 19 памяти, начиная с адресов, заданных значениями для первого и второго операндов. Результат операции в виде третьей векторной величины размещается в блоке 19 памяти. С учетом особенностей реализации цифровых итерационных алгоритмов в систему команд по выходам-входам 15 введены команды для выполнения групповых операций Поиск максимума, Умножение на константу, Умножение с накоплением, Деление, Вычисление четырехточечного

шаблона, Вычисление шеститочечного шаблона.

В процессе работы устройства осуществляется поиск максимума коэффициентов

ах, ау, аг с соответствующих страниц памяти, определение максимального значения коэффициента амакс и вычисление масштабного коэффициента проводимости Mq. По управляющим входам 14 и выходам-входам

15 осуществляется симметрирование коэффициентов матрицы А и нахождение кодов проводимостей Gy, Gz, Gt.

Далее выполняется подпрограмма определения максимального значения правой

части Ьмакс, определения масштабных коэффициентов потоку Mi и по напряжению Ми. Блок 19 памяти по заданному сигналу выставляет информацию на локальные шины 23. Информация сигналом записи по выходу

32 с распределителя 12 импульсов переписывается в регистр 7 данных и через шифратор 9 поступает на информационные входы 26 узлов 5. Младшие разряды с регистра адреса контроллера 13 шины поступают на

дешифратор 8, сигналы с выхода которого разрешают запись принятой информации. Дешифратор 11 введен для формирования 1 в младшем разряде кода проводимостей при переходе от 32-разрядной информации

к усеченной разрядности кодоуправляемых проводимостей для исключения разрывов в матрице проводимостей.

После получения сообщений от всех блоков 3 ЭВМ 4 последовательно передает

в эти блоки начальный адрес подпрограммы уточнения аналогового решения одним из итерационных методов, например модифицированным методом последовательной верхней релаксации.

Для точечной реализации метода для узловых точек с четной суммой (p+q), где р - номер строки, q - номер столбца матрицы узловых процессоров, можно записать

Xk+1 xk + ( +

d

+ EdijxkW),

1 1

(±

при p+q нечетном, и

xkW хк + bi-(dV + d1

+ dijxk+ij)j

i 1

i±J

при p + q четном,

где xk+1 - новое приближение решения;

k - номер итерации;

Wi, Wa - итерационные параметры релаксации.

Формула изобретения

Устройство для решения нелинейных краевых задач, содержащее регистр конфигураций, коммутатор и группу узлов вычис- ления системы конечно-разностных уравнений, каждый из которых выполнен в виде дешифратора команд, блока коммутации, шифратора, регистра данных и матрицы блоков решения уравнений системы, первые информационные входы и выходы которых соединены с соответствующими выходами и информационными входами коммутатора, подключенного управляющим входом к выходу регистра конфигураций, вторые информационные входы и выходы блоков матрицы 1-го (1 2- п-1) узла вычисления системы конечно-разностных уравнений соединены соответственно с вторыми выходами и информационными входами соответствующих блоков матриц (1-1)-го и (i-H)-ro узлов вычисления системы конечно- разностных уравнений группы, третьи информационные входы блоков матрицы решения уравнений системы подключены в каждом узле вычисления системы конечно- разностных уравнений через шифратор к выходу регистра данных, а их выходы соединены с соответствующими информационными входами блока коммутации, отличающееся тем, что, с целью повышения быстродействия, в каждый узел вычисления системы конечно-разностных уравнений введены блок памяти, коммутатор памяти, первый, второй и третий контроллеры шины, дешифратор адреса, распределитель импульсов, переключатель локальных общих шин и аналого-цифровой преобразователь, причем в каждом i-ом узле вычисления системы конечно-разностных уравнений первые группы информационных входов- выходов и управляющие входы первого, второго и третьего контроллеров шины соединены через первую локальную общую шину, подключенную к управляющему входу узла и к информационным выходам-входам, с управляющим и информационными входами-выходами коммутатора памяти и переключателя общих шин i-ro узла, с вторыми группами информационных входов- выходов и управляющими входами первого

контроллера шины, переключателя локальных общих шин и коммутатора памяти (i+1)-ro узла вычисления системы конечно-разностных уравнений, третья группа

информационных выходов-входов переключателя локальных общих шин каждого нечетного и четного 1-го узлов вычисления системы конечно-разностных уравнений подключена к третьей группе информационных входов-вы ходов коммутаторами памяти соответственно (1-1)-го и (i+1)-ro узлов вычисления системы конечно-разностных уравнений, вторые группы информационных входов вторых контроллеров шины

узлов вычисления системы конечно-разностных уравнений соединены между собой и с соответствующей группой информационных входов регистра конфигураций и являются информационными входами устройства, вторые группы входов-выходов третьих контроллеров шины узлов вычисления системы конечно-разностных уравнений соединены между собой, третья группа информационных выходов-входов третьего контроллера шины в каждом узле вычисления системы конечно-разностных уравнений подключена кчетвертой группе информационных входов-выходов коммутатора памяти, подключенного пятой группой выходов и информационных входов соответственно к адресным входам и выходам блока памяти, выход аналого-цифрового преобразователя в каждом i-ом узле решения системы конечно-разностных

уравнений соединен с соответствующим информационным входом первого контроллера шины, первый, второй, третий и четвертый информационные выходы которого подключены к информационным входам соответственно регистра данных, дешифратора адреса, дешифратора команд и к входу синхронизации распределителя импульсов, установочный вход которого соединен с выходом дешифратора команд, а

первый, второй, третий и четвертый выходы подключены соответственно к управляющим входам матрицы блоков решения уравнений системы, к управляющему входу узла коммутации, к входу запуска аналого-цифрового преобразователя и к входу строба записи регистра данных, выход дешифратора адреса подключен к адресным входам матрицы блоков решения уравнений системы и блока коммутации.

| Авторское свидетельство СССР Ns 383069, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1987-03-30—Подача