1

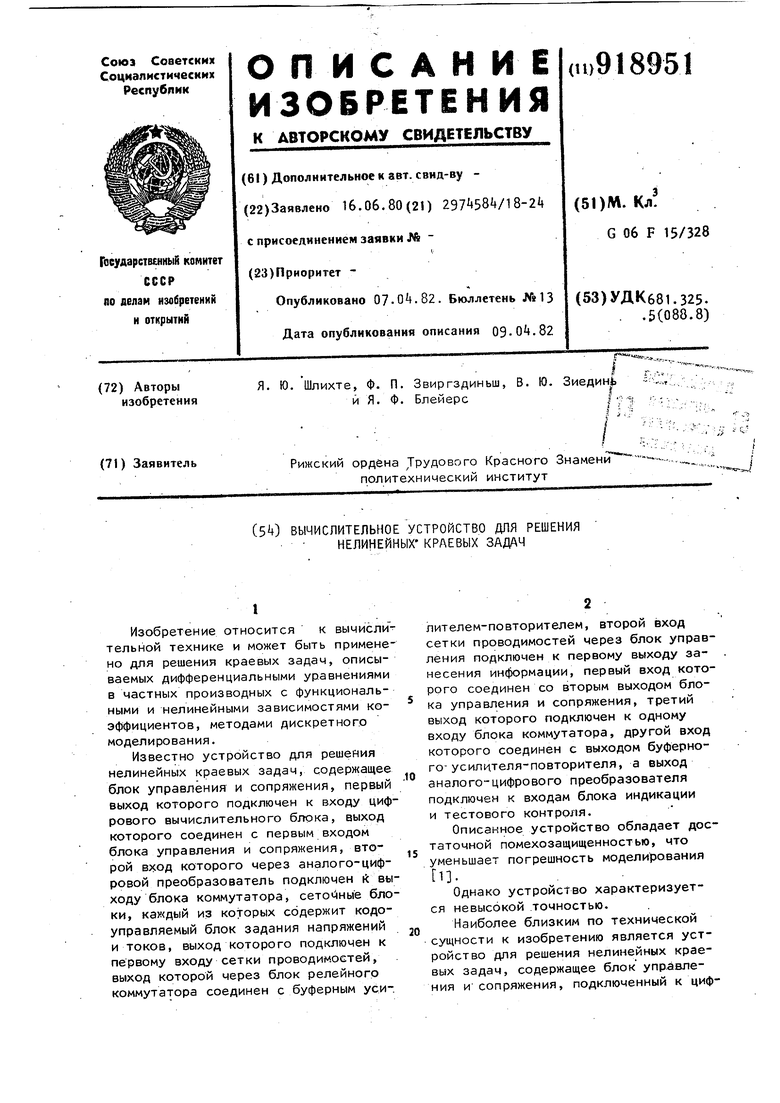

Изобретение относится к вычислительной технике и может быть применено для решения краевых задач, описываемых дифференциальными уравнениями в частных производных с функциональными и нелинейными зависимостями коэффициентов, методами дискретного моделирования.

Известно устройство для решения нелинейных краевых задач, содержащее блок управления и сопряжения, первый выход которого подключен к входу цифрового вычислительного блока, выход которого соединен с первым входом блока управления и сопряжения, второй вход которого через аналого-цифровой преобразователь подключен k выходу блока коммутатора, сетоС)ные блоки, каждый из которых содержит кодоуправляемый блок задания напряжений и токов, выход которого подключен к первому входу сетки проводимостей, выход которой через блок релейного коммутатора соединен с буферным уси-.

лителем-повторителем, второй вход сетки проводимостей через блок управления подключен к первому выходу занесения информации, первый вход которого соединен со вторым выходом блока управления и сопряжения, третий выход которого подключен к одному входу блока коммутатора, другой вход которого соединен с выходом буферного- усилителя-повторителя, а выход

.10 аналого-цифрового преобразователя подключен к входам блока индикации и тестового контроля.

Описанное устройство обладает достаточной помехозащищенностью, что

15 уменьшает погрешность моделирования

1.

Однако устройство характеризуется невысокой .точностью,

Наиболее близким по технической

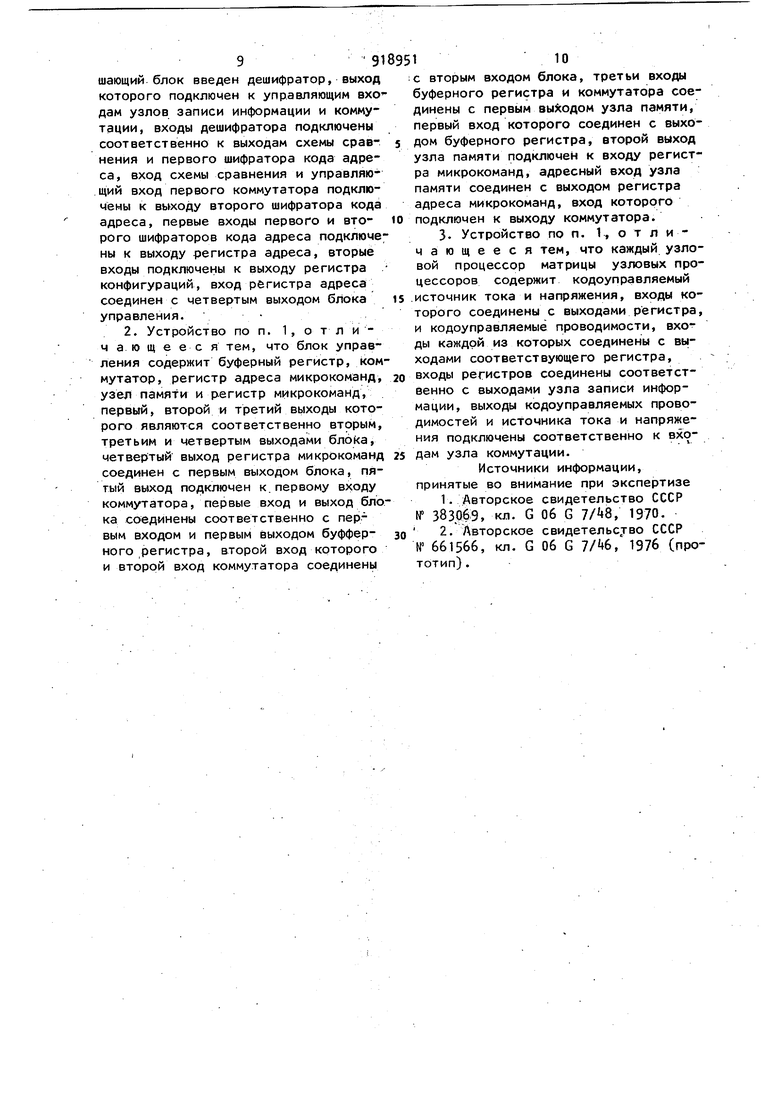

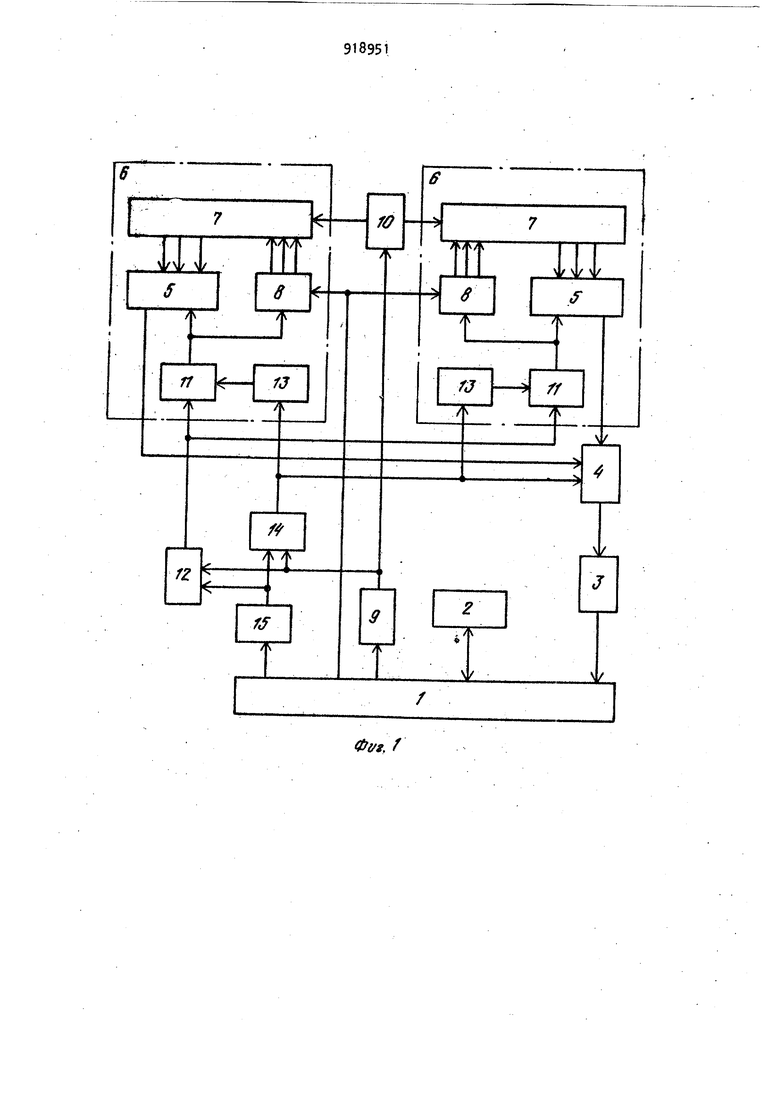

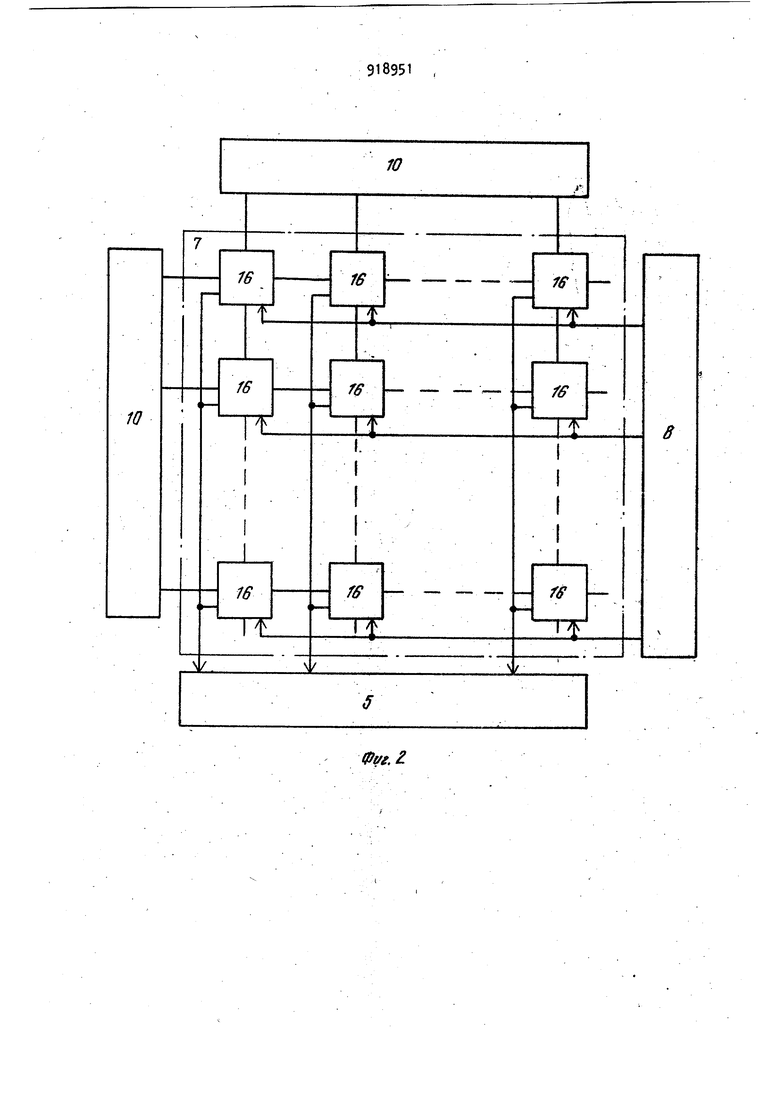

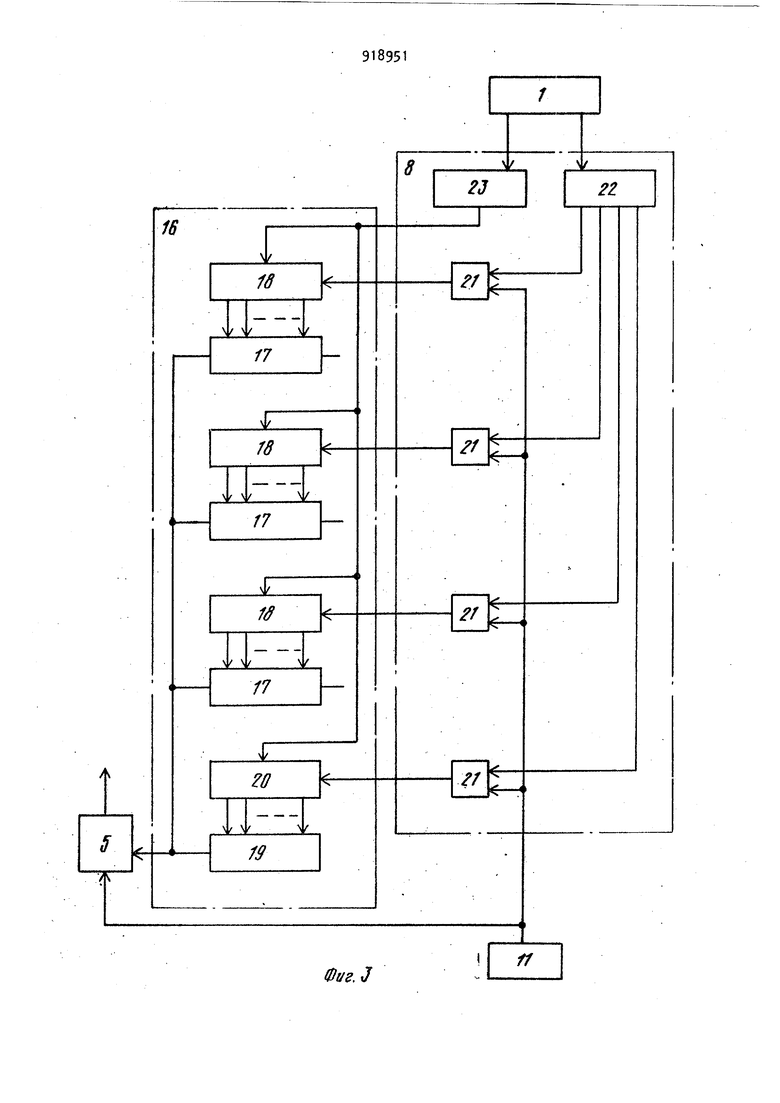

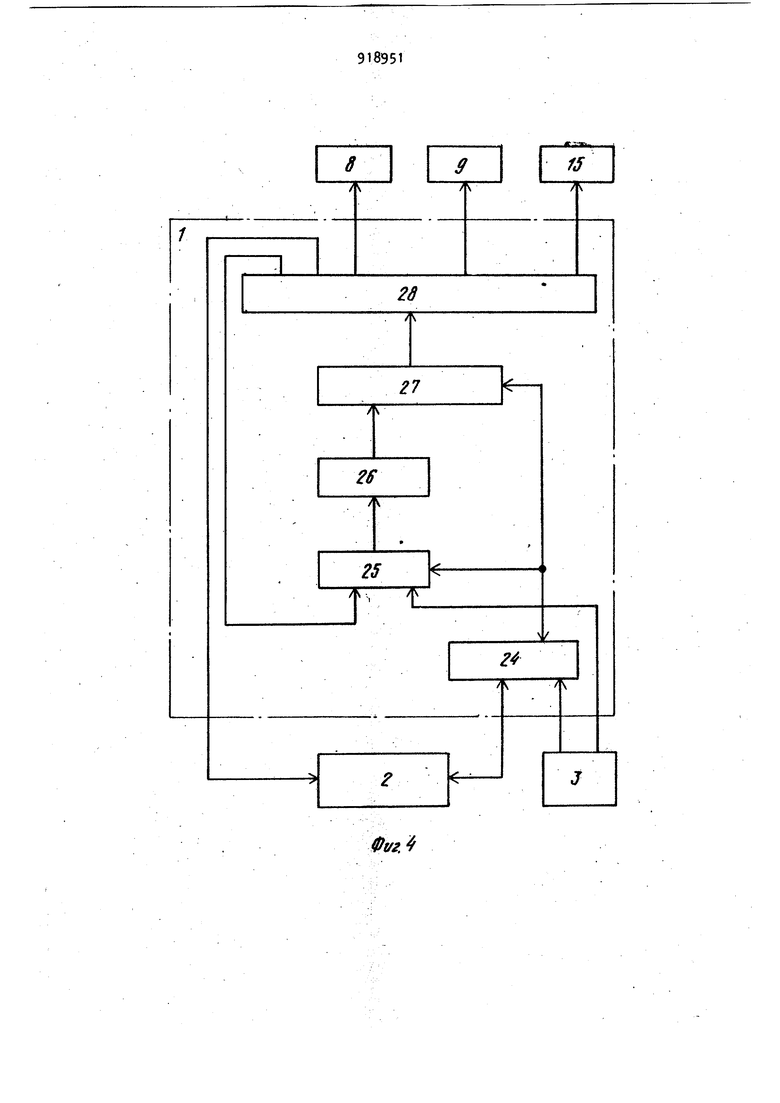

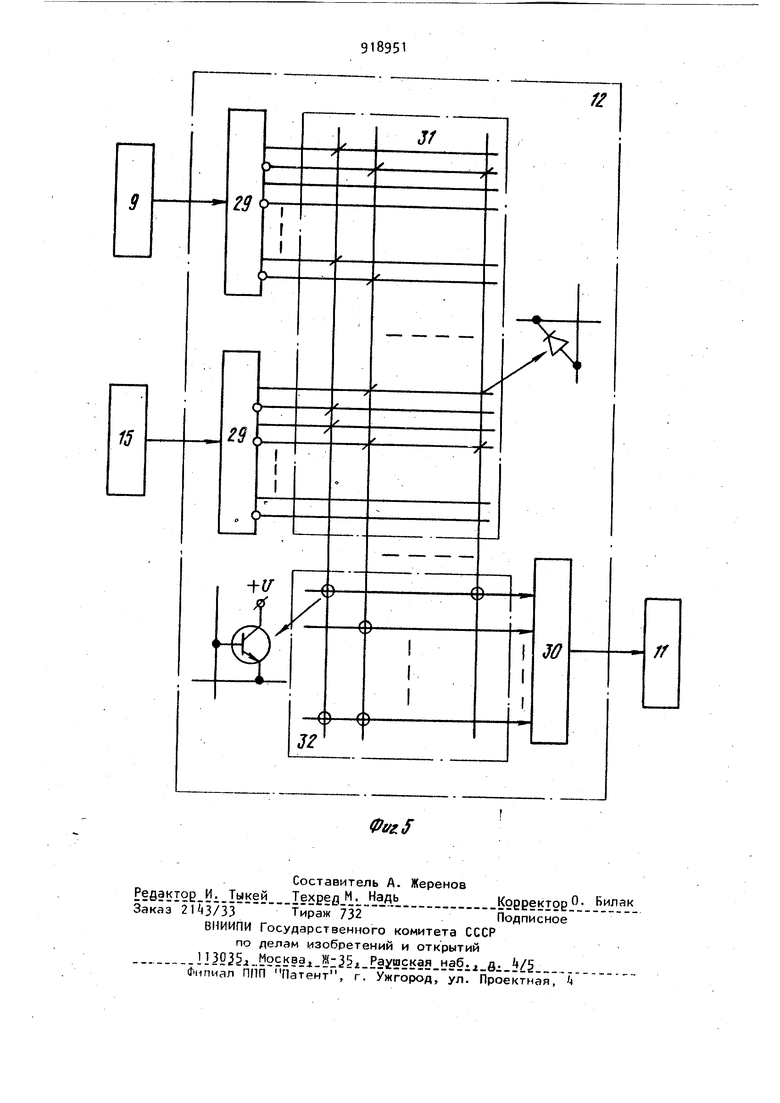

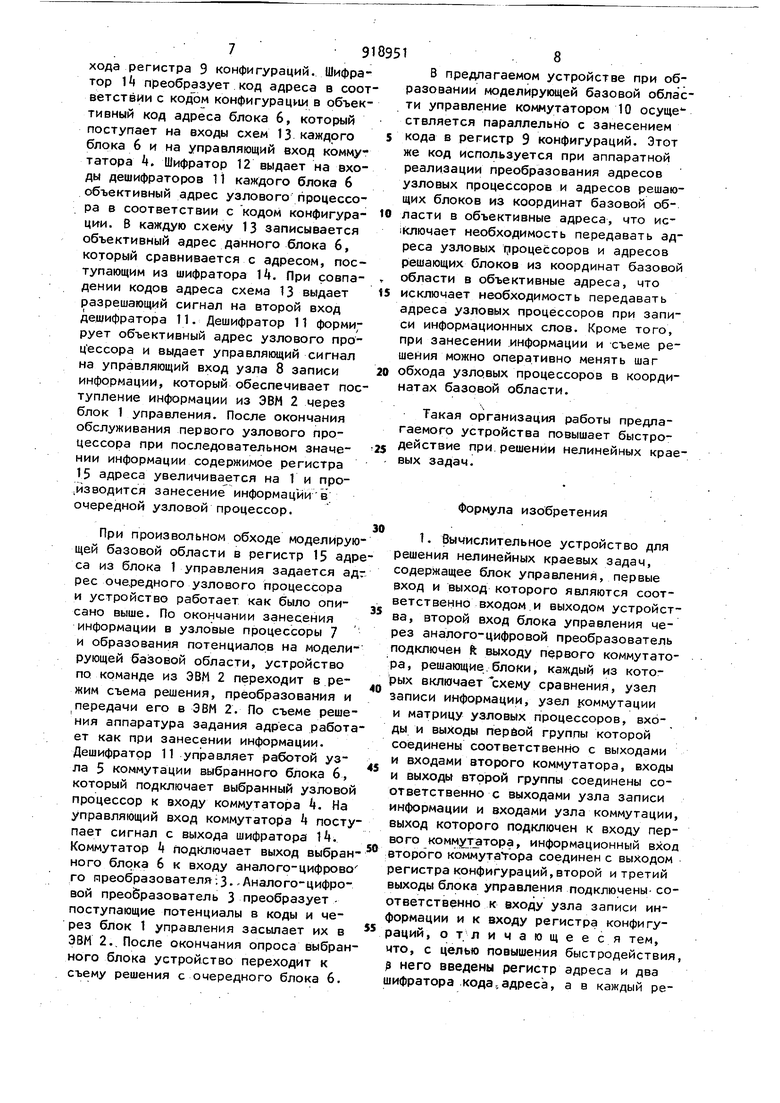

20 сущности к изобретению является устройство для решения нелинейных краевых задач, содержащее блок упр.авления и сопряжения, подключенный к циф3 9 ровому блоку и через аналого-цифровой преобразователь соединен с блоком коммутатора и сеточные блоки, каждый из которых содержит кодоуправ ляемый блок задания напряжений и токов, выход которого подключен к сетк проводимостей, связанной через блок релейного коммутатора с буферным уси лителем-повторителем, соединенным с блоком коммутатора, подключенным к блоку управления и сопряжения,, связанного с селекторами, блоком коммутации областей произвольной конфигурации и с блоком занесения информации, соединенным с кодоуправляемым блоком задания напряжений и токов, с первым селектором и через блок управления с сеткой проводимости, подключенной к блоку коммутации областей произвольной конструкции, селек- торы соединены между собой и подключены к блоку коммутации областей про извольной конструкции. В данном устройстве повышена точность решения управления за счет обеспечения возможности образования необходимой конфигурации решающей сетки 21.. Однако известное„устройство обладает низким быстродействием. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в устройство, содержащее блок управления, первые вход и выход кото рого являются соответственно входом и выходом устройства, второй вход блока управления через аналоготцифровой преобразователь подключен к выходу первого коммутатора, решающие блоки, каждый из которых включает схему сравнения, узел записи информа ции, узел коммутации и матрицу узловых процессоров, входы и выходы первой группы которой соединены соответст венно с выходами и входами второго коммутатора, входы и выходы второй группы соединены соответственно с выходами узла записи информации и входами узла коммутации, выход кото рого подключен к входу первого комму татора, информационный вход второго коммутатора соединен с выходом регистра конфигураций, второй и третий выходы блока управления подключены соответственно к входу узла записи информации и к входу регистра конфигураций, введены регистр адреса и два шифра 4 тора кода адреса, а в каждый решающий блок введен дешифратор, выход которого подключен к управляющим входам узлов записи информации и коммутации, входы дешифратора подключены соответственно к выходам схемы сравнения и первого шифратора кода адреса, вход схемы сравнения и управляющий вход первого коммутатора подключены к выходу второго шифратора кода адреса, первые входы первого и второго шифраторов кода адреса подключены к выходу регистра адреса, вторые входы подключены к выходу регистра конфигураций, вход регистра соединен с четвертым выходом блока управления. Кроме того, в устройстве блок управления со ержит буферный регистр, коммутатор, регистр адреса микрокоманд, узел памяти и регистр микрокоманд., первый, второй и третий выходы которого являются соответственно вторым, третьим и четвертым выходами блока, четвертый выход регистра микрокоманд соединен с первым выходом блока, пят.ый выход подключен к первому входу коммутатора, первые вход и выход блока соединены соответственно с первым входом и первым выходом буферного регистра, второй вход которого и второй вход коммутатора соединены с вторым входом блока, третьи входы буферного регистра и коммутатора соединены с первым выходом узла памяти, первый вход которого соединен с выходом буферного регистра, второй выход узла памяти подключен к входу регистра микрокоманд, адресный вход узла памяти соединен с выходом регистра адреса микрокоманд, вход которого подключен к выходу комjjiyTaTopa. Каждый узловой процессор матрицы узловых процессоров в устройстве содержит кодоуправляемый источник тока и напряжения, входы которого соединены с выходом регистра, и кодоуправл 1емые проводимости, входы каждой из KdTopbix соединены с выходами соответствующего реги стра, входы регистров соединены соответственно с выходами узла записи информации, выходы кодоуправляемых проводимостей и источника тока и напряжения подключены соответственно к входам узла коммутации. На фиг. 1 представлена структурная схема устройства; на фиг. 2 схема двумерной матрицы узловых про59цессоров; на фиг. 3 схема узлового процессора и узла записи информации; на фиг. схема блока управле ния; на фиг. 5 - схема шифратора кода адреса. Устройство содержит блок 1 управления, электронную машину (ЭВМ) 2, аналого-цифровой преобразователь 3 коммутатор it, узел 5 коммутации, ре:шающие блоки 6,матрицу 7 узловых процессоров,узел 8 записи информации,регистр 9 конфигураций,коммутатор 10, дешифратор 11,шифратор 12 кода адреса, схему 13 сравнения, шифратор 14 кода адреса, регистр 15 адреса, узловой процессор 16, кодоуправляемые проводимости 17, регистры 18, кодоуправляемый источник 19 тока и напряжения регистр 20, группы элементов И 21, регистр 22 признака параметра, ре- . гистр 23 данных, буферный регистр 2k коммутатор 25, регистр 26 адреса мик рокоманд, узел 27 памяти, регистр 28 микрокоманд, узлы 29 ввода, узел 30 вывода, матрицу 31 элементов И и мат рицу 32 элементов ИЛИ. Узловой процессор содержит крдоуправляемые проводимости 17 в направ лении осей Х,У. Из регистра 23 данных узла 8 код проводимостей или источника 19 тока и напряжения поступает на вход регис ра 18 источника 19- Запись в регистры осуществляетсяи по сигналам, которые поступают с выходов элементов И 21 узла 8, на один вход которых поступает разрешающий сигнал выбранного узлового процессора с выхода дешифра тора 11. На другие входы поступает сигнал признака параметра с выходов регистра 22 признака узла 8. Запись в соответствующий регистр 18, 20 про исходит при совпадении на входах эле ментов И 21 сигналов адресе, который поступает с выхода дешифратора 11 и признака параметра, например, X, который поступает с выхода регистра 22 признака параметра узла 8. Из ЭВМ 2 в узел 27 записывается . программа работы устройства. Начальная команда из ЭВМ 2 через буферный регистр 2k и коммутатор 25 поступает в регистр 26 адреса микрокоманд, который определяет первую микрокоманду в узле 27 памяти. Микрокоманда из узла 27 считывается в регистр 28 мик рокоманд. С выхода регистра 28 микро команд на вход коммутатора 25 поступает сигнал, служащий для передачи адреса следующей микрокоманды в регистр 28 микрокоманд. Со второго выхода регистра 28 микрокоманде регистр 9 конфигурации записывается код конфигурации модульной базовой области. Из узла 27 в регистр 28 микрокоманд поступает очередная микрокоманда и с выхода регистра 28 в регистр 15 адреса записывает код начального адреса 9 координатах установленной конфигурации моделирующей базовой области. Затем по команде, записанной в узле ., 27 с выхода регистра 28 в регистры 22 и 23 узла 8, записываются коды признака вводимого параметра и .кодо- вой эквивалент выбранного параметра соответственно; После обслуживания очередного узлового процессора в регистр 15 адреса из регистра 28 микрокоманд записывается код следующего узлового процессора и устройство работает как было описано выше. При съеме решения аппаратура задания адреса узлового процессора работает как при занесении информации, а решение задачи поступает через буферный регистр 2k в ЭВМ 2. Запускается .аналого-цифровой преобразователь . ;после преобразования АЦП 3 выдает сиг нал Конец преобразования, который поступает на вход коммутатора 25. Результат преобразования из аналогоцифрового преобразователя 3 записывается в буферный регистр 2k, а затем по сигналу, поступающего из per гистра 28 в ЭВМ, этот результат записывается в ЭВМ и запускается преобразователь 3 на следующее решение. Для образования конфигурации модулирующей базовой области в регистр 9 конфигураций из ЭВМ 2 через блок 1 . управления поступает код. Из регистра 9 конфигураций этот код поступает на коммутатор 10, который коммутирует границы матриц узловых процессоров 7 блоков 6, образуя необходимую конфигурацию модулирующей базовой области. Затем из ЭВМ 2 через блок 1 управления в регистр 15 адреса заносится начальный адрес узлового процессора в координатах установленной конфигурации моделирующей базовой области. С выхода регистра 15 адреса код поступает на входы шифраторов Щи 12, на других входах которых присутствует код конфигурации с выхода регистра 9 конфигураций. Шифратор 1Ц преобразует код адреса в соот ветствии с кодом конфигурации в объективный код адреса блока 6, который поступает на входы схем 13 каждого блока 6 и на управляющий вход коммутатора . Шифратор 12 выдает на входы дешифраторов 11 каждого блока 6 объективный адрес узлового процессора в соответствии с кодом конфигурации. В каждую схему 13 записывается объективный адрес данного блока 6, который сравнивается с адресом, поступающим из шифратора 1. При совпадении кодов адреса схема 13 выдает разрешающий сигнал на второй вход дешифратора 11. Дешифратор 11 формирует объективный адрес узлового процессора и выдает управляющий сигнал на управляющий вход узла 8 записи информации, который обеспечивает пос тупление информации из ЭВМ 2 через блок 1 управления. После окончания обслуживания первого узлового процессора при последовательном значении информации содержимое регистра 15 адреса увеличивается на 1 и про,изводится занесение информациив очередной узловой процессор. При произвольном обхода моделирую щей базовой области в регистр 15 адр са из блока 1 управления задается ад рее очередного узлового процессора и устройство работает как было описано выше. По окончании занесения информации в узловые процессоры 7 и образования потенциалов на моделирующей базовой области, устройство по команде из ЭВМ 2 переходит в режим съема решения, преобразования и передачи его в ЭВМ 2. По съеме решения аппаратура задания адреса работа ет как при занесении информации. Дешифратор 11 управляет работой узла 5 коммутации выбранного блока 6, который подключает выбранный узловой процессор к входу коммутатора k. На управляющий вход коммутатора k посту пает сигнал с выхода шифратора 1. Коммутатор k подключает выход выбран ного блока 6 к входу аналого-цифрово го преобразователя;3.,Аналого-цифровой преобразователь 3 преобразует поступающие потенциалы в коды и через блок 1 управления засылает их в ЭВМ 2.. После окончания опроса выбран ного блока устройство переходит к съему решения с очередного блока 6. 9 . 8 В предлагаемом устройстве при образовании моделирующей базовой области управление коммутатором 10 осуществляется параллельно с занесением кода в регистр 9 конфигураций. Этот же код используется при аппаратной реализации преобразования адресов узловых процессоров и адресов решающих блоков из координат базовой области в объективные адреса, что ис1|спючает необходимость передавать адреса узловых г роцессоров и адресов решающих блоков из координат базовой области в объективные адреса, что исключает необходимость передавать адреса узловых процессоров при записи информационных слов. Кроме того, при занесении .информации и съеме решения можно оперативно менять шаг обхода узловых процессоров в координатах базовой области. Такая организация работы предлагаемого устройства повышает быстродействие при решении нелинейных краевых задач. Формула изобретения 1. Вычислительное устройство для решения нелинейных краевых задач, содержащее блок управления, первые вход и выход которого являются соответственно входом и выходом устройства, второй вход блока управления через аналого-цифровой преобразователь подключен ft выходу первого коммутатора, решающие.блоки, каждый из которых включаетсхему сравнения, узел записи информации, узел коммутации и матрицу узловых процессоров, входы и выходы первой группы которой соединены соответственно с выходами и входами второго коммутатора, входы и выходы второй группы соединены соответственно с выходами узла записи информации и входами узла коммутации, выход которого подключен к входу первого коммут атора, информационный вход второго коммутатора соединен с выходом регистра конфигураций,второй и третий выходы блока управления подключены- соответственно к входу узла записи информации и к входу регистра конфигураций, отличающееся тем, что, с целью повышения быстродействия, Э него введены регистр адреса и два шифратора кода,адреса, а в каждый решающий блок введен дешифратор, выход которого подключен к управляющим входам узлов записи информации и коммутации, входы дешифратора подключены соответственно к выходам схемы сравнения и первого шифратора кода адреса, вход схемы сравнения и управляющий вход первого коммутатора подключены к выходу второго шифратора кода адреса, первые входы первого и эторого шифраторов кода адреса подключены к выходу регистра адреса, вторые входы подключены к выходу регистра конфигураций, вход регистра адреса соединен с четвертым выходом блока управления.

2. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит буферный регистр, коммутатор, регистр адреса микрокоманд, узел памяти и регистр микрокоманд, первый, второй и третий выходы которого являются соответственно вторым, третьим и четвертым выходами блока, четвертый выход регистра микрокоманд соединен с первым выходом блока, пятый выход подключен к.первому входу коммутатора, первые вход и выход блока соединены соответственно с первым входом и первым выходом буфферкого регистра, второй вход которого и второй вход коммутатора соединены

:с вторым входом блока, третьи входы буферного регистра и коммутатора соединены с первым выводом узла памяти, первый вход которого соединен с выходом буферного регистра, второй выход узла памяти подключен к входу регистра микрокоманд, адресный вход узла памяти соединен с выходом регистра адреса микрокоманд, вход которого подключен к выходу коммутатора.

3- Устройство по п. 1, о т л и чающееся тем, что каждый узловой процессор матрицы узловых процессоров содержит кодоуправляемый .источник тока и напряжения, входы которого соединены с выходами регистра, и кодоуправляемые проводимости, входы каждой из которых соединены с вцходами соответствующего регистра, входы регистров соединены соответственно с выходами узла записи информации, выходы кодоуправляемых проводимостей и источника тока и напряжения подключены соответственно к входам узла коммутации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 3830$9, кл. G Об G , 1970. 2. Авторское свидетельсхво СССР W 661566, кл. G 06 G , 1976 (прототип) .

Фуг, f

фуг. г

i

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1164747A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

r

27

r

Т

i i

-

4Фш. 4

г9.

15

LJх:

Авторы

Даты

1982-04-07—Публикация

1980-06-16—Подача