соединена с группой входов регистра микрокоманд, первый выход которого подключен к второму информационному входу коммутатора команд, управляющий вход которого соединен с выходом коммутатора условий перехода, управляющий вход которого подключен к второму выходу регистра микрокоманд, третий выход которого соединен с управляющим входом регистра команд, выход генератора тактовых импульсов подключен к стробирующим входам регистра команд, счетчика и регистра микрокоманд, четвертьй выход которого соединен с управляющим входом счетчика, выход которого соединен со стробирующим входом коммутатора команд, пятый выход регистра микрокоманд подключен к стробирующим входам первого и второго регистров кода адреса, первого и второго аналого-цифровых преобразователей и блоков элементов И обоих блоков формирования частного решения вход запуска устройства соединен с первым информационным входом коммутатора условий перехода, отличающееся тем, что, с целью повышения быстродействия, в него введены два блока памяти, триггер, мультиплексор блок регистрации, а в каждый блок формирования частного решения введен элемент ИЛИ, выход которого соединен с вторым входом дешифратора, пятый выход регистра микрокоманд подключен к первому входу блока арифметических вычислений, к стробирующим входам первого и второго блоков памяти и к установочному входу триггера,.выход которого соединен с первыми входами элементов ШШ и с первыми управляющими входами первого и второго блоков памяти, вторые управляющие входа которых подключены к выходам соответственно первого и второго шифраторов кода адреса, второй выход блока арифметических вычислений соединен с вторым информационным

входом коммутатора условий перехода ,и с входами разрешения съема информации аналого-цифровых преобразователей и блоков памяти, третий выход блока арифметических вычислений подключен к информационному входу блок регистрации., управляющий вход которого соединен с шестым выходом регистра микрокоманд, выходы первого и второго блоков памяти подключены соответственно к первому и второму информационным входам мультиплексора, выход которого соединен с вторым входом блока арифметических вычислений, третий вход которого подключен к информационному входу второго регистра кода адреса, выход второго шифратора кода адреса соединен с управляющим входом мультиплексора.

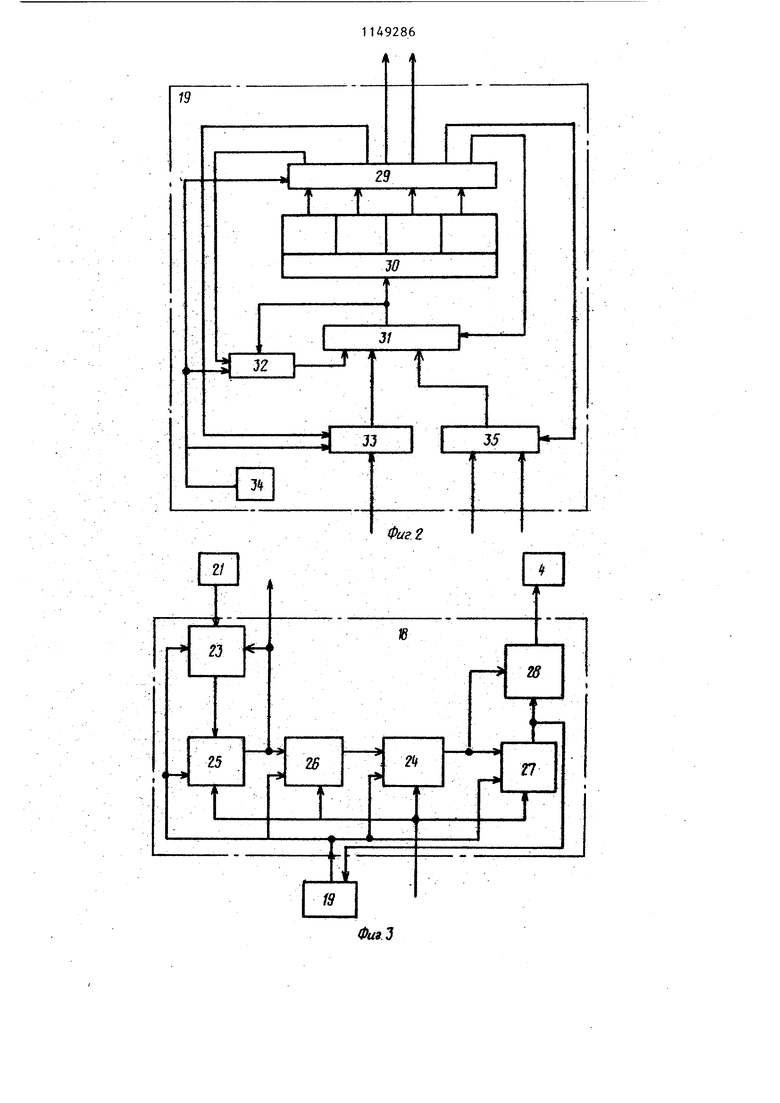

2. Устройство по П.1, о т л и ч а ю щ е е с .я тем, что блок арифметических вычислений содержит два сумматора, элемент памяти, узел умножения, схему сравнения и элемент И, выход которого является первым выходом блока, первый вход которого соединен со стробирующими входами сумматоров, элемента памяти, узла умножения и схемы сравнения, выход которой соединен с первьм входом элемента И и является вторым выходом блока, третий выход .которого подключен к первому входу первого сумматора, к выходу элемента памяти и к первому входу узла умножения, выход которого соединен с первым входом второго сумматора, выход которого подключен к второму входу элемента И и к первому входу схемы сравнения, второй вход блока соединен с вторым входом первого сумматора, третий вход блока подключен к вторым входам элемента памяти, уз.ла умножения, второго сумматора и схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1164747A1 |

| Устройство для съема информации с сеточной электромодели | 1980 |

|

SU962985A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

1. УСТРОЙСТВО ДЛЯ РЕШЕНИЯ КРАЕВЫХ ЗАДАЧ, содержащее два блока формирования частного решения, каждый из которых содержит кодоуправляемую R-сетку, коммутатор, блок элементов И, шифратор и дешифратор, выход.которого подключен к первым входам коммутатора и блока элементов И, выход которого соединен с разрядными входами кодоуправляемой R-сетки, группа центральных узлов которой подключена к второму входу коммутатора, блок управления,состоящий из генератора тактовых импульсов, коммутатора условий перехода, регистра команд, коммутатора команд, счетчика, блока памяти программы и регистра, микрокоманд, блок арифметических вычислений, первый выход которого подключен к вторым входам блоков элементов И обоих блоков формирования частного решения, пер1вый и второй аналого-цифровые преобразователи, информационные входы которых соединены с выходами коммутаторов соответственно первого и второго блоков формирования частного решения, перв)1й шифратор кода адреса, выход которого подключен к входам дешифраторов обоих блоков формирования частного решения, второй шифратор кода адреса, выход которого соеднен с входами шифраторов обоих блоков формирования частного решения, первый регистр кода адреса, выход которого подключен к первым входам первого и второго шифраторов кода адреса, второй регистр кода адреса, выход которого соеди t нен с вторыми входами шифраторов кода адреса и с управляющим входом коммутатора конфигураций, первая If) группа выходов которого подключена С к первой группе граничных узлов кодоуправляемой R-сетки первого блока формирования частного решения, вторая группа граничных узлов которой соединена с первой группой информационных входов коммутатора конфи 4 гураций, вторая группа выходов котоСО рого подключена к первой группе граЮ ничных узлов кодоуправляемой R-сеткй 00 второго блока формирования частного d5 решения, вторая группа граничных уз- : :г1ов которой соединена с второй группой информационных входов коммутатора конфигураций, вход ввода данных устройства подключен к информационным входам первого и второго регистров кода адреса и регистра команд, выход которого соединен с первым информа- ; ционным входом коммутатора команд, выход которого подключен к счетному входу счетчика и к входу блока памяти программы, группа выходов которого

1

Изобретение относится к аналогоцифровой вычислительной технике и может быть применено для решения краевых задач теории поля, опйсьшаемых дифференциальными уравнениями

в частных производных, методом дискретного моделирования.

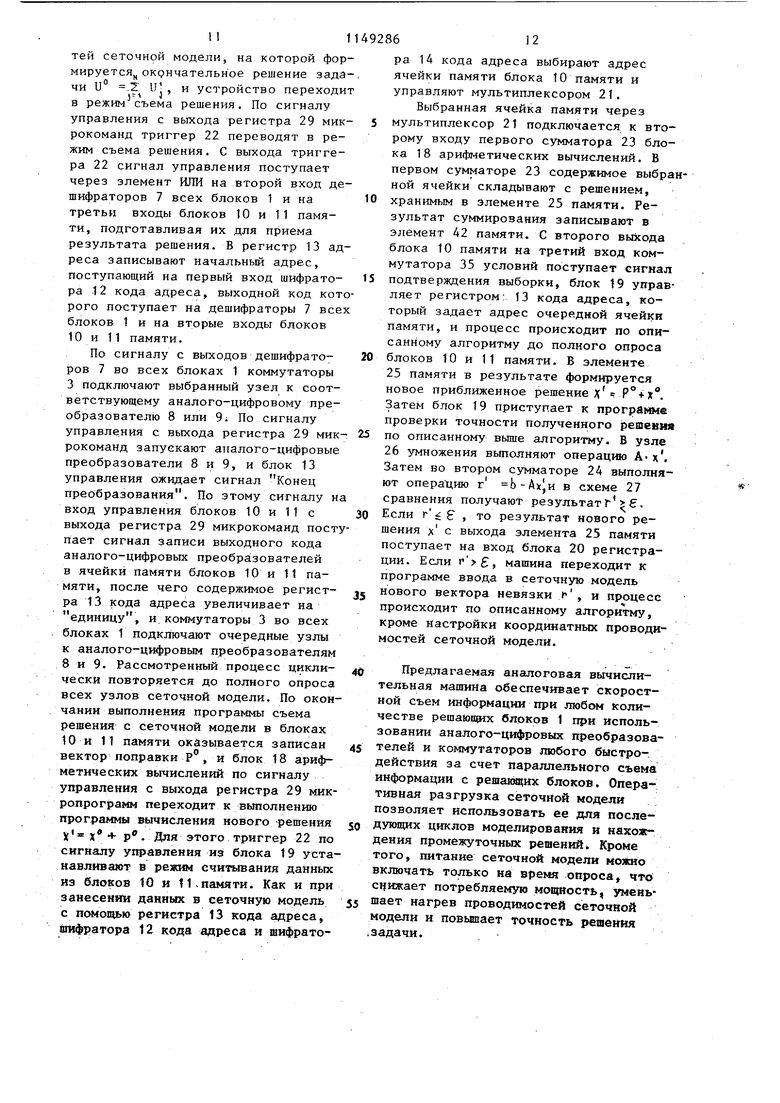

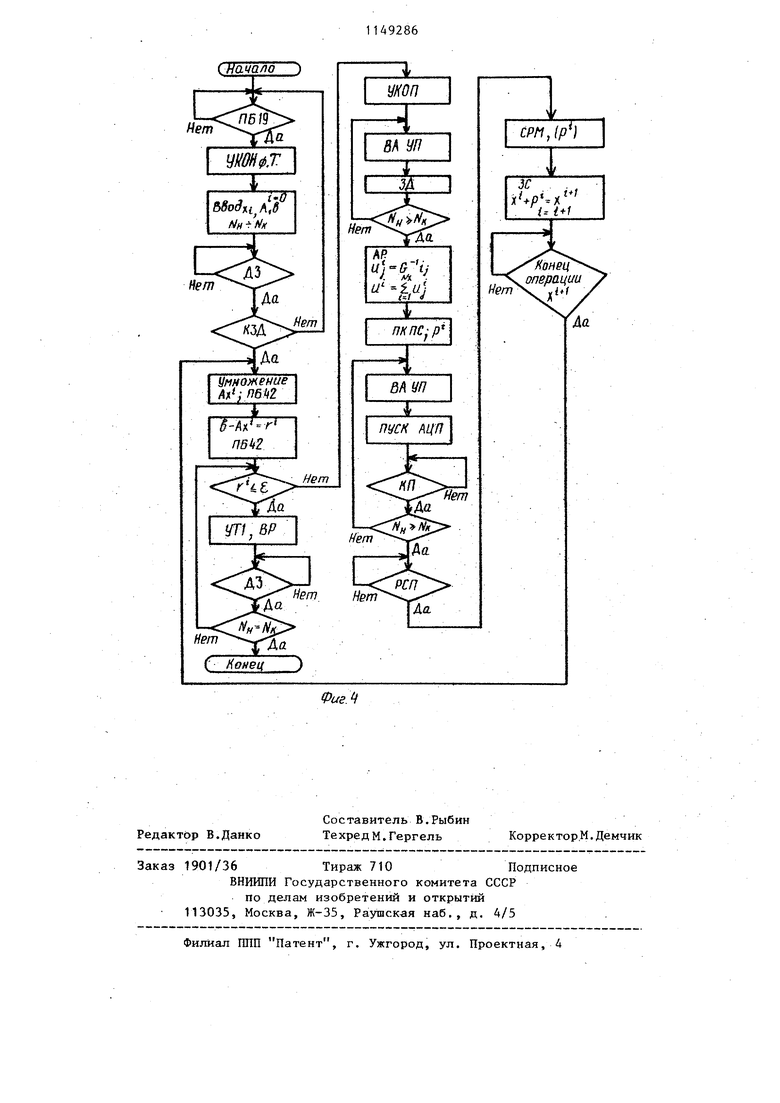

Известно устройство для решения нелинейных краевых задач, содержащее, блок управления и.сопряжения, подключенный к цифровому блоку и через аналого-цифровой преобразователь соединенный с блоком коммутатора, и сеточные блоки, каждый из которых содержит кодоуправляемый блок задания напряжений и токов, выход которого подк-гдачен к сетке про водимостей, связанной.через блок релейного коммутатора с буферным усили телем-повторителем, соединенным с блоком коммутатора, подключенного к блоку управления и сопряжения и связанного с селекторами, блоком коммутаций областей произвольной конфигурации и с блоком занесения информации, соединенным с кодоуправляемым блоком задания напряжений и токовое первым селектором и через блок управ ления с сеткой проводимости, подключенной к блоку коммутации областей произвольной конфигурации, селекторы соединены между собой и подключены к блоку коммутации областей произ водной конфигурации. В этом устройстве повьппена точность решения уравнений за счет возможности образования необходимой конфигурации решакяцей сетки lj . Однако, это устройство обладает низким быстродействием. Наиболее близким техническим реше нием к изобретению является вычислительное устройство для решения нелинейных краевых задач, содержащее два блока формирования частотного решения, включающие каждый кодоуправ ляемую R-сетку, коммутатор, блок элементов И, шифратор и дешифратор, выход которого подключен к первьм входам коммутатора и блока элементов И, выход которого соединен с разрядньми входами кодоуправляемой R-сетки группа центральных узлов которой под ключена к второму входу коммутатора подкгаоченного к аналого-цифровому преобразователю и к шифратору и соединенного с шифратором кода адреса, с регистром кода адреса и регистром конфигурации, связанным с ко1 1утатором конфигураций, соединенн с кодо управляемыми R-ce-тками, аналого-ш фровой преобразователь, цифровая вычислительная машина, регистр кода адреса и регистр кода конфигурации ;соединены с блоком управления. Известное устройство позволяет параллельно с эзиесением информации в регистр конфигурации управлять ком мутатором конфигураций и обеспечивает аппаратурную реализацию преобразования адресов, что повышает его быстродействие 2 . Однако известное устройство обладает низким быстродействием при съеме информации с кодоуправляе1 гх R-сеток, что вызывает расход энергии и нагрев аппаратуры устройства, вызывающий уход ее параметров в процессе съема решения. Это снижает точность решения задачи и требует дополнительных затрат машинного времени. Кроме того, в известном устт ройстве неравномерно загружена аппаратура устройства. Целью изобретения является повыш ние быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее два блока формирования частного решения , каждый из которых содержит кодоуправляемую R-сетку, коммутатор, блок элементов И, шифратор и дешифратор, выход которого подключен к первым входам коммутатора и блока элементов И, выход которого соединен с разрядными входами кодоуправляемой R-сетки, группа центральных узлов которой подключена к второму входу коммутатора, блок управления, состоящий из генератора тактовых импульсов, коммутатора условий перехода, регистра команд, коммутатора команд, счетчика.,блока памяти программы и регистра микрокоманд, блок арифметических вычислений, первый выход которого подключен к вторым входам блоков элементов И обоих блоков формирования частного решения, первый и второй аналогоцифровые преобразователи, информационные входы которых соединены с выходами коммутаторов соответственно первого и второго блоков формирования частного решения, первый шифратор кода адреса, выход которого подключен к входам дешифраторов обоих блоков формирования частного решения, второй шь ратор кода адреса, выосод которого соединен с входам ми шифраторов обоих блоков формирования частного решения, первый регистр кода адреса, выход которого подключен к первым входам первого и второго шифраторов кода адреса, : втарой регистр кода адреса, выход которого соединен с вторыми входами шифраторов кода адреса и с управляю-щим входом коммутатора конфигураций, первая группа выходов которого подключена к первой группе граничных узлов кодоуправляемой R-сетки первого блока формирования частного решения, вторая группа граничных узлов которой соединена с первой группой информационных входов коммутатора конфигураций, вторая группа выходов которого подключена к первой группе граничных узлов кодоуправляемой R-сетки второго блока формирования частного решения, вторая группа граничных узлов которой соединена с второй группой информационных входов коммутатора конфигураций, вход ввода данных устройства подключен к информационньм входам первого и второго регистров кода адреса и регистра команд, выход которого соединен с первым информационнь входом коммута тора команд, выход которого подключен к счетному входу счетчика и к входу блока памяти программы, группа выходов которого соединена с группой входов регистра микрокоманд, первый пыход которого подключен к второму информационному входу коммутатора команд, управляющий вход которого соединен с выходом коммутатора условий перехода, управляющий вход кото рого подключен к второму выходу регистра микрокоманд, третий выход ко торого соединен с управляющим входо регистра команд, выход генератора тактовых импульсов подключен к стро бирующим входам регистра команд, счетчика и регистра микрокоманд, че вертый выход которого соединен с управляющим входом счетчика, выход которого соединен со стробирующим входом коммутатора команд, пятый выход регистра микрокоманд подключён к стробирующим входам первого и второго регистров кода адреса, перв го и второго аналого-цифровых преоб разователей и блоков элементов И об их блоков формирования частного реш ния, вход запуска устройства соединен с первьм информационньм входом комм татора услорий перехода, введены два блока памяти, триггер, мультийлексор, блок регистрации, а в каждьй блок,формирования частного реше НИЛ введем элемент ИЛИ, выход которого соединен с вторым входом дешиф ратора, пятый выход регистра микрокоманд подключен к первому входу блока арифметических вычислений, к стробирующим входам первого и второго блоков памяти и к установочному входу триггера, выход которого соединен с первьми входами элементов ИЛИ и с первыми управляющими входами первого и второго блоков памяти, вторые управляющие входы которых подключены к выходам соответственно первого и второго шифраторов коДа адреса, второй выход блока арифметических вычислений соединен с вторым информационным входом коммутатора условий перехода и с входами разрешения съема информации аналого-цифровых преобразователей и блоков памяти, третий выход блока арифметических в вычислений подключен к информационному входу блока регистрации, управляющий вход которого соединен с шестым выходом регистра микрокоманд, выходы первого и второго блоков памяти подключены соответственно к первому и второму информационным входам мультиплексора, выход которого соединен с вторым входом блока арифметических вычислений, третий вход которого подключен к информационному входу второго регистра кода адреса, выход второго шифратора кода адреса соединен с управляющим входом мультиплексора. Кроме того, блок арифметических вычислений содержит два сумматора, элемент памяти, узел умножения, схему сравнения и элемент И, выход которого является первым выходом блока, первый вход которого соединен со стробирующими входами сумматоров, элемента памяти, узла умножения и схемы сравнения, выход которой соединен с первым входом элемента и и является вторым выходом блока, третий выход которого подключен к первому входу первого сумматора, к выходу элемента памяти и к первому входу узла умножения, выход которого соединен с первым входом второго сумматора, выход которого подключен к второму входу элемента И и к первому входу схемы сравнения, второй вход блока соединен с вторым входом первого сумматора, третий вход блока подключен к вторым входам элемента памяти, узла умножения, второго сумматора и схемы сравнения На фиг, 1 изображена блок-схема предлагаемого устройства, на фиг. 2 - блок-схема блока управления J на фиг. 3 - блок-схема блока ари4 4етических вычислений; на фиг. 4 - блок-схема алгоритма рабо ты устройства. Устройство содержит блоки 1 формирования частного решения, каждый из которых содержит кодоуправляемую R-сетку 2, коммутатор 3, блок элементов И 4, шифратор 5, элемент ИЛИ 6 и дешифратор 7. Кроме того, устройство содержит аналого-цифровые преобразователи 8 и 9, блоки 10 и 11 памяти , шифратор 12 кода адреса, регистр 13 кода адреса, шифратор 14 кода адреса, регистр 15 кода адреса, коммутатор 16 конфигураций, вход 17 ввода данных, блок 18 арифметических вычислений, блок 19 управления, блок 20 регистрации, мультиплексор 21, триггер 22. Кроме того, блок 18 арифметичес ких вычислений содержит сумматоры 23 и 24, элемент 25 памяти, узел 26 умножения, схему 27 сравнения, элемент И 28. Блок 19 управления со держит регистр 29 микрокоманд, блок 30 памяти программы, коммутатор 31 команд, счетчик 32, регистр 33 команд, генератор 34 тактовых импульсов и коммутатор 35 условий переход Устройство для решения краевых задач работает по блок-схеме алгори на, представленной на фиг. 4, где принятые следующие обозначения: 1ТБ19 - пуск блока 19 управления, УКОНФ.Т. - запись кода конфигурации в регистр 15 и уст новка триггера 22 в нуль, Н„ - N. запись адресов в регистр 13 кода адреса от начального до конеч ного адреса, подтверждение записи данных в блок 18 арифметических вычислений, конец записи данных в R-сетке 2, установка триггера 22 в единицу, - вьвдача результата реше НИН задачи из блока 18 арифметических вычисле ний, УКОП - установка кода операции в регистр 29 микрокоманд , ВА УП - выборка адреса, ЗД - запись кодовых эквивалентов , АР - аналоговое решение системы разностных уравнений , ПКПС - переход к программе съема результата решения Р , АЦП - аналого-цифровые преобразователи 8 и 9, КП - конец преобразования, РСП - разрешение считывания с блока 10 (11), СРМ - считывание результата моделирования с блока 10(11) памяти, ЗС - запуск первого сумматора 23, формирование нового решения. Блок 19 управления организует оту всех блоков аналоговой вычисельной машины по записанной в его яти программе. Данные и команды ашину поступают по входной шине данных последовательно байт за том, которые синхронизируются налом запуска, поступающим на д квитирования блока 13 управле. Для выполнения любой операции егистр 33 команд с входной шины данных записывают код команда. который используется блоком 19 управления в качестве адреса перехода к соответствукнцей микропрограмме, путем передачи его в блок 30 памяти программы. По этому адресу из блока 30 выбирают микрокоманду и засылают ее в регистр 29 микрокоманд. Из регистра 29 микрокоманд с первого выхода адрес перехода поступает на второй вход коммутатора 31 команд, с второго выхода адрес выбора источника следующего адреса микроманды на первый вход коммутатора 35 условий, с третьего выхода сигнал управления - на второй вход счетчика 32, с группы выходов сигналы управления по программе - на входы управления соответствующих блоков устройства. На пятом выходе регистра 29 микрокоманд вырабатывается сигнал квитирования записи информации, свидетельствующий о том, что команда или данные приняты в блоке 19 управления. Соответствующее кодирование блока 30 позволяет микропрограммно реализовать выполнение всех функций .машины путем последовательной проверки условий ветвления микропрограмм, поступающ1гх на вход коммутатора 35, и выборки поля управляющих сигналов в регистре 29 микрокоманд.

Первой выполняется команда установки конфигурации.решающего поля сеточной модели. По этой команде из регистра 29 микрок,оманд на вход управления регистра 15 кода конфигураций поступает сигнал разрешения записи, и с входной шины 17 данных код конфигурации записывают в регистр 15 кода конфигураций, с выхода которого код конфигурации поступает на вторые входы шифратора 12 кода адреса и шифратора 14 кода, а также на вход коммутатора 16 конфигураций. По этому коду коммутатор 16 конфигураций соединяет граничные вьпводы R-сеток 2 блоков 1. По этой же команде устанавливают триггер 22 в режим ввода данных в сеточную модель. Следующей по программе выполняют операцию ввода исходных данных для решения системы разностных уравнений . С входной шины 17 данных в элемент 25 памяти последовательно байт за байтом записывают вектор сеточной функции X в первом приближении. Вектор правых частей Ь записывают во второй сумматор 24, а квадратную матрицу А - в узел 26 умножения

Ввод исходных данных осуществляется квитированием сигналов Пуск и Готов к приему на втором входе и первом выходе блока 19, а занесение информации в элемент 25 памяти, в узел 26 умножения и но второй сумматор 24 происходит по сигналам управления с группы выходов блока 1 Ввод исходных данных решаемой задачи прекращается с появлением на втором входе коммутатора 35 условий сигнала Конец приема данных. По этому сигналу блок 19 переходит к выполнению операции умножения А х в узле 26 умножения, на первый вход которого поступает х а по второму входу записана квадратная матрица А Результат умножения поступает .на первый вход второго сую атора 24, где суммируется с вектором Ь. Ка выходе второго сумматора 24 формируется вектор невязки г b - Ах поступающий на первые входы схемы 27 сравнения и элементы И 28. По сигналу блока 19 на выходе схемы 27 сравнения формируется результат сравнения г Е(6 - постоянная, характеризующая желаемую точность решения), . поступающий на второй вход элемента 0 И 28 и на третий вход коммутатора 35 условий.

Если , то результат решения X с выхода устройства памяти выводится на блок 20 регистрации. Если , происходит переход к программе занесения г° и А в R-сеткй 2 ре- шающих блоков 1. С входной шины 17 данных по сигналу управления из регистра микрокоманд в регистр 13 кода

0 адреса записывают код адреса блока

1в R-сетки 2, к которой предполагается обращение последующими командами. Записанные коды с выхода регистра 13 кода адреса поступают на первые входы шифратора 14 кода адреса

и щифратора 12 кода адреса узлового процессора, где в соответствии с кодом конфигурации, действующим на вторых входах, их преобразуют из

0 представления в координатах базовых областей конфигурации в коды физического адреса блока 1. Код физического адреса блока 1 поступает с выхода шифратора 14 кода адреса на входы шифратора 5, а код адреса R-сетки

2с выхода шифратора 12 кода адреса узлового процессора - на первые входи дешифраторов 7. С выхода щифратора

5 выбранного блока 1 разрешакнций

0 сигнал через элемент ИЛИ 6 поступает на второй вход дешифратора 7.

Дешифрованный адрес с выхода дешифратора 7 поступает на первые входы коммутатора 3 и блок элементов И 4. ;

5 На второй вход блока элементов И 4 с первого выхода блока арифметических вычислений последовательно поступают коды данных и с выхода блока элементов И 4 по сигналу управления записываются в R-сетку 2, где формируется частное решение. Затем содержимое регистра 13 увеличивают на единицу, и указанный процесс циклически повторяют, В узлах -сет5 ,ки 2 блоков 1 формируется решение UJ как результат умножения вводимого токд 1 на значения, обратные величинам установленньш проводимос11 1

тей сеточной модели, на которой формируется окрнчательное решение задачи и° .Z и , и устройство переходит в режим съема решения. По сигналу управления с выхода регистра 29 микрокоманд триггер 22 переводят в режим съема решения. С выхода триггера 22 сигнал управления поступает через элемент ИЛИ на второй вход дешифраторов 7 всех блоков 1 и на третьи входы блоков 10 и 11 памяти, подготавливая их для приема результата решения. В регистр 13 адреса записывают начальный адрес, поступающий на первый вход шифратора 12 кода адреса, выходной код которого поступает на дешифраторы 7 всех блоков 1 и на вторые входы блоков 10 и 11 памяти.

По сигналу с выходов дешифраторов 7 во всех блоках 1 коммутаторы 3 подключают выбранный узел к соответствующему аналого-цифровому преобразователю 8 или 9; По сигналу управления с выхода регистра 29 микрокоманд запускают аналого-цифровые преобразователи 8 и 9, и блок 13 управления ожидает сигнал Конец преобразования. По этому сигналу на вход управления блоков 10 и 11 с выхода регистра 29 микрокоманд поступает сигнал записи выходного кода аналого-цифровых преобразователей в ячейки памяти блоков 10 и 11 памяти, после чего содержимое регистра 13 кода адреса увеличивает на единицу, и. коммутаторы 3 во всех блоках 1 подключают очередные узлы к аналого-цифровым преобразователям 8 и 9. Рассмотренный процесс циклически повторяется до полного опроса всех узлов сеточной модели. По окончании выполнения программы съема решения с сеточной модели в блоках 10 и 11 памяти оказывается записан вектор поправки р, и блок 18 арифметических вычислений по сигналу управления с выхода регистра 29 микропрограмм переходит к выполнению программы вычисления нового решения X X Р. Для этого триггер 22 по сигналу управления из блока 19 устанавливают в режим ечичъгеания данных из блоков 10 и 11,памяти Как и при занесеням данных в сеточную модель с поно1кью регистра 13 кода адреса, шифратора 12 кода адреса и шифрато928612

ра 14 кода адреса выбирают адрес ячейки памяти блока 10 памяти и управляют мультиплексором 21.

Выбранная ячейка памяти через 5 мультиплексор 21 подключается к второму входу первого сумматора 23 блока 18 арифметических вычислений. В первом сумматоре 23 содержимое выбранной ячейки складывают с решением,

10 хранимым в элементе 25 памяти. Результат суммирования записывают в элемент 42 памяти. С второго выхода блока 10 памяти на третий вход коммутатора 35 условий поступает сигнал

15 подтверждения выборки, блок 19 управляет регистром: 13 кода адреса, который задает адрес очередной ячейки памяти, и процесс происходит по описанному алгоритму до полного опроса

0 блоков 10 и 11 памяти. В элементе

25памяти в результате формируется новое приближенное решение х- . Затем блок 19 приступает к программе проверки точности полученного решения

5 по описанному вьше алгоритму, В узле

26умножения вьтолняют операцию А- х . Затем во втором сумматоре 24 выполняют операцию г в схеме 27 сравнения получают результат Г J5.

0 Если г р , то результат нового решения с выхода элемента 25 памяти поступает на вход блока 20 регистрации. Если , машина переходит к программе ввода в сеточную модель

J нового вектора невязки , и процесс происходит по описанному алгоритму, кроме настройки координатных проводимостей сеточной модели.

0 Предлагаемая аналоговая вычислительная машина обеспечивает скоростной съем информации при любом количестве решающих блоков 1 при использовании аналого-цифровых преобразователей и коммутаторов любого быстродействия за счет параллельного съема информации с решакУщих блоков. Оперативная разгрузка сеточНой модели позволяет использовать ее для после0 ДУощих циклов моделирования и нахождения промежуточных решений Кроме того, питание сеточной модели можно включать только на время опроса, чтб снижает потребляемую мощность, уменьшает нагрев проводимостей сеточной модели и повьтает точность решения .задачи.

Т гл

I

П

3 32

a 33 I I 35

i I i I

a ь

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для решения нелинейных краевых задач | 1977 |

|

SU661566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство для решения нелинейных краевых задач | 1980 |

|

SU918951A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-10-05—Подача