а

4;:

00 00

«vj

1

Изобретение относится к автоматике и вычислительной технике, а именно к цифровой обработке сигналов, и может быть использовано для построения кодеров и декодеров в каналах связи с использованием дельта-модуляции. .

По основному авт. св. № 594583 известен дельта-декодер с экспандированием, содержащий формирователь цифрового сигнала, первый и второй входы которого соединены с входами устройства, а выходы подключены к первым входам соответствующих элементов И и к соответствующим входам анализатора цифрового сигнала, первый и второй выходы которого соединены соответственно со счетным и управляющим входами двоичного реверсивного счетчика, выходы разрядов которого подключены к управляющим входам соответствукщих ключей, входы которых соединены с соответствующими выходами Генератора импульсных последовательностей, объединенные выходы ключей соединены с вторыми входами элементов И, выходы которых подключены к соответствующим входам генератора тока, выход которого соединен с входом интегратора, подключенного своим выходом к выходу устройства LI J.

Недостатком этого дельта-декодера является повышенный уровень шу.ма в режиме молчания из-за неидеальности устройств преобразования исходного сигнала в .цифровую последовательность.

Ц-елЬ изобретения - уменьшение шумов квантования в режиме молчания.

Поставленная цель достигается тем, что в дельта-декодер с экспандйрованием введены .резистор, повторитель напряжения, дополнительный, ключ, вьщелитель постоянной составляющей, источник опорного напряжения и компаратор, выход интегратора через соединенные последовательно резистор и повторитель напряже.ВИЯ подключен к выходу устройства, а объединенные выходы ключей соединены с входом выделителя постоянной составляющей, выход которого подклю чен к первому входу компаратора, второй вход которого соединен с источником опорного напряжения, а выход - с управляющим Входом дополнительного ключа, вход и выход которо го подключены соответственно к нуле48872

вой шине и входу повторителя напряжения.

J

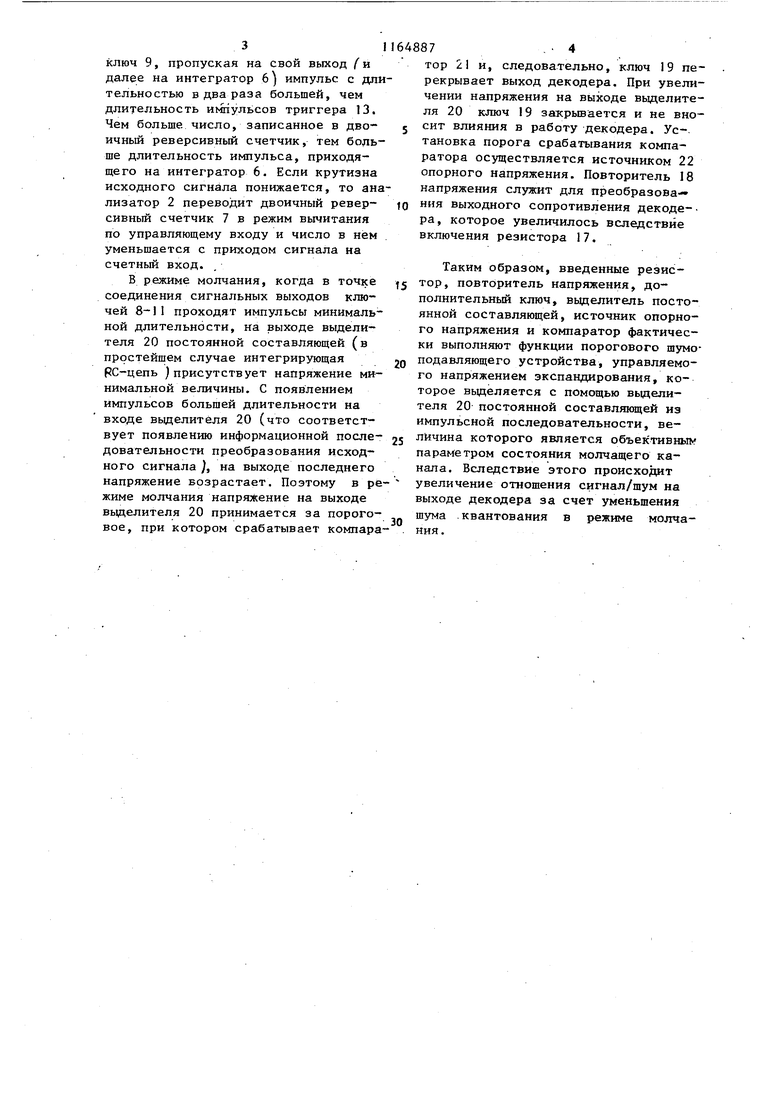

На чертеже показана блок-схема предлагаемого устройства. 5 Устройство содержит формирователь 1 цифрового сигнала, выходы которого подключены к входам анализатора 2 цифрового сигнала и к первым входам соответствующих элементов 3

0 -и 4 И, выходь которых через генератор 5 тока.подключены-к входу интегратора 6. Выходы анализатора 2 цифрового сигнала подключены также к счетному и управляющему входам

5 двоичного реверсивного счетчика 7, .выходы разрядов которого подключены к управляющим входам соответствующих ключей 8-11, сигнальные входы которых соединены с соответствующими входами генератора 12 импульсных последовательностей, а выходы ключей 8-11 подключены ко вторым входам элементов 3 и 4 И, при этом двоичный реверсивный счетчик 7 состоит из цепочки триггеров 13-16.

Последовательно соединенные резистор 17 и повторитель 18 напряжения включены на выходе интегратора 6, между входом повторителя 18 и нулевой шиной включен дополнительный ключ 19. С выходами ключей 8-11 соединен вход выделителя 20 постоянной составляющей, а выход его соединен с первым входом компаратора 21, ко второму входу которого подключен источник 22 опорного напряжения, а выход койпаратора 21 соединен с управляющим входом дополнительного ключа 19. Устройство работает следующим образ м. ,.

Анализато.р 2 анализирует двоичный сигнал на выходе формирователя 1. Если число подряд следующих единиц или нулей не превышает четыре, то в двоичном реверсивном счетчике 7 взведен только триггер 13. Выходной сигнал триггера 13 отпирает ключ 8 и на интегратор 6 через генератор 5 тока и соответствующий элемент 3 или 4 И каждый интервал дискретизации проходят импульсы из последовательности, имеющей минимальную длительность. Если число подряд следующих единиц или нулей превьщ1ает четыре, то анализатор 2 выдает импульсный сигнал, при котором триггер 13 приходит в исходное состояние, а триггер 14 взводится. В результате ключ 8 запирается, а отпирается

31

ключ 9, пропуская на свой выход (к далее на интегратор б) импульс с длительностью в два раза большей, чем длительность икшульсов триггера 13. Чем больше число, записанное в двоичный реверсивный счетчик, тем больше длительность импульса, приходящего на интегратор 6. Если крутизна исходного сигнала понижается, то анализатор 2 переводит двоичный реверсивный счетчик 7 в режим вычитания по управляющему входу и число в нем . уменьшается с приходом сигнала на счетный вход.

В режиме молчания, когда в точке соединения сигнальных выходов ключей 8-11 проходят импульсы минимальной длительности, на выходе выделителя 20 постоянной составляющей (в простейшем случае интегрирующая рС-цепь ) присутствует напряжение минимальной величины. С появлением Импульсов большей длительности на входе выделителя 20 (что соответствует появлению информационной последовательности преобразования исходного сигнала ), на выходе последнего напряжение возрастает. Поэтому в режиме молчания напряжение на выходе вьвделителя 20 принимается за пороговое, при котором срабатывает компара4887, 4

тор 21 и, следовательно, ключ 19 перекрывает выход декодера. При увеличении напряжения на выходе вьщелителя 20 ключ I9 закрьшается и не вносит влияния в работу декодера. Установка порога срабатывания компаратора осуществляется источником 22 опорного напряжения. Повторитель 18 напряжения служит для преобразовало выходного сопротивления декоде-. ра, которое увеличилось вследствие включения резистора 17.

Таким образом, введенные резистор, повторитель напряжения, дополнительный ключ, выделитель постоянной составляющей, источник опорного напряжения и компаратор фактически выполняют функции порогового шумоQ подавляющего устройства, управляемого напряжением экспандирования, которое выделяется с помощью выделителя 20 постоянной составляющей из импульсной последовательности, величина которого является объективные параметром состояния молчащего канала. Вследствие этого происходит увеличение отношения сигнал/шум на выходе декодера за счет уменьшения шума .квантования в режиме молчаНИН.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-декодер с экспандированием | 1976 |

|

SU594583A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Адаптивный дельта-модулятор | 1989 |

|

SU1644367A1 |

| АДАПТИВНЫЙ ДЕЛЬТА КОДЕК | 2013 |

|

RU2530294C1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1431074A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ РАСХОДА ЭЛЕКТРОЭНЕРГИИ С ПРЕОБРАЗОВАТЕЛЕМ СИГМА-ДЕЛЬТА С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ (ВАРИАНТЫ) | 1994 |

|

RU2117303C1 |

| Дельта-декодер | 1987 |

|

SU1444954A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

ДЕЛЬТА-ДЕКОДЕР С ЭКСПАНДИРОВАНИЕМ по авт. св. № 594583, отличающийся тем, что, с целью уменьшения шумов квантования в режиме молчания, 1з него введены резистор, повторитель напряжения, дополнительный ключ, выделитель постоянной составляющей, источник опорного напряжения и компаратор, выход интегратора через соедияенные последовательно резистор и повторитель напряжения подключен к выходу устройства, а объединенные выходы ключей соединены с входом выделителя постоянной составляющей, выход которого подключен к первому входу компаратора, второй вход которого соединен с источником опорного напряжения, а выход - с управляющим входом дополнительного ключа, вход и выход которого подключены соответственно к нулевой шине и входу повто(Л рителя напряжения.

| I | |||

| Дельта-декодер с экспандированием | 1976 |

|

SU594583A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-04—Подача