Изобретение относится к технике телефонной связи и может быть применено в качестве устройства преобразования речевых сигналов из аналоговой в цифровую форму в цифровых телефонных аппаратах.

В настоящее время в различных областях жизни и деятельности различных структур и ведомств все более широкое распространение находят цифровые сети телефонной связи, образованные с использованием высокоскоростных и низкоскоростных цифровых каналов.

Однако используемые в упомянутых сетях телефонной связи оконечные устройства ведения связи, в том числе телефонные аппараты, не обеспечивают выполнения возросших требований по качеству передачи речевого сигнала, особенно при работе по низко- и среднескоростным цифровым каналам связи.

Целью изобретения является повышение качества передачи речевого сигнала по цифровым каналам связи с малой скоростью передачи при одновременном упрощении схемы устройства.

Поставленная цель достигается тем, что адаптивный дельта-кодек состоит из кодера, содержащего дискретизатор аналогового сигнала, компаратор, инвертор, JK триггер, схему адаптации передачи, включающую в себя делитель напряжения, операционный усилитель передачи, первый, второй и третий резисторы, конденсатор, а также содержащего генератор тактовых импульсов (ГТИ); декодера, содержащего усилитель, аналоговый ключ, фильтр нижних частот, схему адаптации приема, включающую в себя делитель напряжения, операционный усилитель приема, первый, второй и третий резисторы, конденсатор, источника и приемника аналогового сигнала, цифрового канала связи, при этом выход дискретизатора аналогового сигнала кодера соединен с первым входом компаратора, выход которого через инвертор подключен к первому (К) входу и непосредственно ко второму (J) входу JK триггера, выход которого соединен со входом цифрового канала связи и с первым входом операционного усилителя передачи схемы адаптации передачи, ко второму входу которого подключено питающее напряжение с делителя напряжения, выход которого соединен с первым выводом первого резистора, второй вывод которого соединен с первыми выводами второго и третьего резисторов и конденсатора, второй вывод которого соединен со вторым выводом второго резистора и с корпусом источника питания, второй вывод третьего резистора соединен со вторым входом компаратора, выход генератора тактовых импульсов, используемых в качестве стробирующих импульсов, соединен с установочным входом JK триггера и с управляющим входом дискретизатора аналогового сигнала, к питающему входу которого подключен корпус источника питания, а информационный вход дискретизатора аналогового сигнала соединен с выходом источника аналогового сигнала, выход цифрового канала связи соединен со входом усилителя декодера, выход которого соединен с управляющим входом аналогового ключа и с первым входом операционного усилителя приема схемы адаптации приема, ко второму входу которого подключено питающее напряжение с делителя напряжения, выход операционного усилителя приема соединен с первым выводом первого резистора, второй вывод которого соединен с первыми выводами второго и третьего резисторов и конденсатора, второй вывод которого соединен со вторым выводом второго резистора и с корпусом источника питания, второй вывод третьего резистора соединен со входом аналогового ключа, выход которого соединен со входом фильтра нижних частот, выход которого соединен с приемником аналогового сигнала, при этом информационный вход дискретизатора аналогового сигнала кодера является входом адаптивного дельта-кодека, выходом которого является выход JK триггера кодера, соединенный со входом цифрового канала связи, канальным входом дельта-кодека является вход усилителя декодера, соединенный с выходом цифрового канала связи, выход фильтра нижних частот декодера является информационным выходом аналогового сигнала адаптивного дельта-кодека, который соединен со входом приемника аналогового сигнала.

Сопоставимый анализ с известными решениями по построению устройств для преобразования аналогового сигнала в цифровую форму для обеспечения работы по цифровым каналам связи показывает, что заявляемый адаптивный дельта-кодек отличается по принципам адаптации и схемой устройства для их реализации. При этом следует отметить, что на момент подачи заявки на изобретение совокупность признаков, подобных предлагаемому адаптивному дельта-кодеку, не была выявлена.

Таким образом, заявляемый адаптивный дельта-кодек соответствует критерию изобретения «новизна».

Сравнение заявляемого решения с другими техническими решениями по реализации предлагаемого устройства показывает, что выполнение элементов адаптивного дельта-кодека осуществляется достаточно просто и при этом не потребуется дополнительного технического творчества. Это позволяет сделать вывод о соответствии предлагаемого адаптивного дельта-кодека критерию «существенные отличия».

Заявляемое решение явным образом не следует из уровня техники и имеет изобретательский уровень.

Изготовлен макет предлагаемого адаптивного дельта-кодека с использованием существующих элементов отечественного производства, проведены его испытания, которые подтвердили возможность его промышленной реализации.

Предлагаемый адаптивный дельта-кодек может найти применение в телефонных аппаратах, предназначенных для работы по цифровым среднескоростным каналам связи и абонентским линиям цифровых телефонных станций.

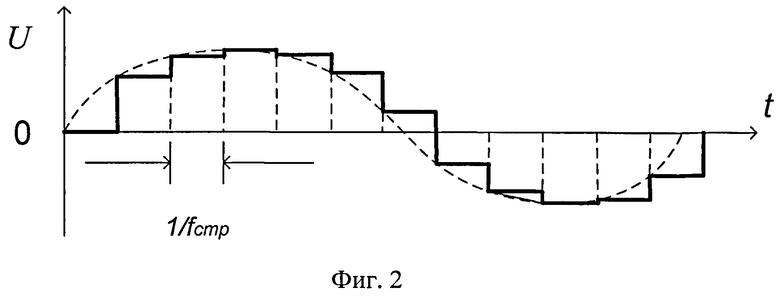

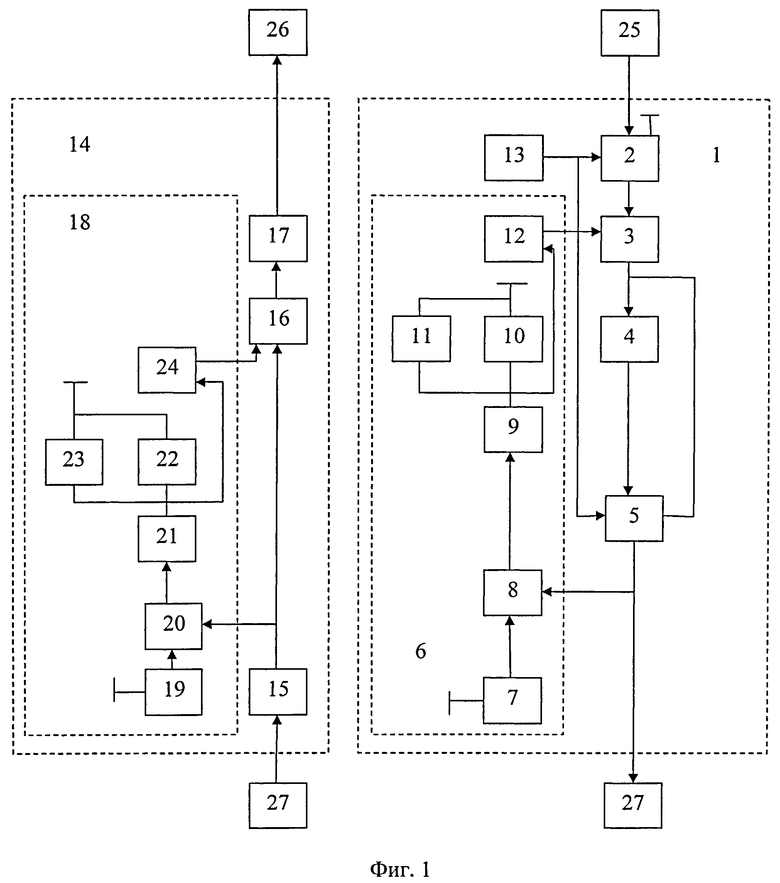

На фиг.1 приведена структурная электрическая схема адаптивного дельта-кодека, а на фиг.2 показаны эпюры напряжений на выходе дискретизатора аналогового сигнала.

Адаптивный дельта-кодек состоит (см. фиг.1) из кодера 1, содержащего дискретизатор 2 аналогового (речевого) сигнала, компаратор 3, инвертор 4, JK триггер 5, схему 6 адаптации передачи, включающую в себя делитель 7 напряжения, операционный усилитель 8 передачи, первый 9, второй 10 и третий 11 резисторы, конденсатор 12, а также содержащего генератор 13 тактовых импульсов (ГТИ); декодера 14, содержащего усилитель 15, аналоговый ключ 16, фильтр 17 нижних частот и схему 18 адаптации приема, включающую в себя делитель 19 напряжения, операционный усилитель 20 приема, первый 21, второй 22 и третий 24 резисторы, конденсатор 23, источника 25 и приемника 26 аналогового сигнала, цифрового канала 27 связи. При этом информационный вход дискретизатора 2 аналогового (речевого) сигнала кодера 1, к которому подключен выход источника 25 аналогового сигнала, является входом адаптивного дельта-кодека, управляющим входом которого является управляющий вход дискретизатора 2, соединенный с выходом генератора 13 тактовых импульсов, выходом адаптивного дельта-кодека является выход JK триггера 5 кодера 1, который соединен со входом цифрового канала 27 связи, канальным входом декодера 14 является вход усилителя 15, соединенный с выходом цифрового канала 27 связи, выход фильтра 17 нижних частот декодера 14 является информационным выходом аналогового сигнала адаптивного дельта-кодека, который соединен со входом приемника 26 аналогового сигнала.

На фиг.2 показаны эпюры напряжений, где по горизонтальной оси отложено время t, а по вертикальной оси указан уровень напряжения U. Здесь же на горизонтальной оси показана ширина ступеньки адаптации дельта-кодека, равная ta=1/fстр, где fстр - это частота следования стробирующего импульса, поступающего с выхода генератора 13 тактовых импульсов. Для среднескоростных цифровых каналов связи частота следования тактовых импульсов выбирается равной 16 кГц.

Выход дискретизатора 2 аналогового сигнала (см. фиг.1) кодера 1 соединен с первым входом компаратора 3, выход которого через инвертор 4 подключен к первому (К) входу и непосредственно ко второму (J) входу JK триггера 5, выход которого соединен со входом цифрового канала 27 связи и с первым входом операционного усилителя 8 передачи схемы адаптации 6 передачи, ко второму входу которого подключено питающее напряжение с делителя 7 напряжения, выход которого соединен с первым выводом первого резистора 9, второй вывод которого соединен с первыми выводами второго 10 и третьего 12 резисторов и конденсатора 11, второй вывод которого соединен со вторым выводом второго резистора 10 и с корпусом источника питания, второй вывод третьего резистора 12 соединен со вторым входом компаратора 3.

Выход генератора 13 тактовых импульсов, используемых в качестве стробирующих импульсов, соединен с установочным входом JK триггера 5 и с управляющим входом дискретизатора 2 аналогового сигнала, к питающему входу которого подключен корпус источника питания, а информационный вход дискретизатора 2 аналогового сигнала соединен с выходом источника 25 аналогового сигнала.

Выход цифрового канала 27 связи соединен со входом усилителя 15 декодера 14, выход которого соединен с управляющим входом аналогового ключа 16 и с первым входом операционного усилителя 20 приема схемы адаптации 18 приема, ко второму входу которого подключено питающее напряжение с делителя 19 напряжения, выход операционного усилителя 20 приема соединен с первым выводом первого резистора 21, второй вывод которого соединен с первыми выводами второго 22 и третьего резисторов 24 и конденсатора 23, второй вывод которого соединен со вторым выводом второго резистора 22 и с корпусом источника питания, второй вывод третьего резистора 24 соединен со входом аналогового ключа 16, выход которого соединен со входом фильтра 17 нижних частот, выход которого соединен с приемником 26 аналогового сигнала.

Дискретизатор 2 кодера 1 предназначен для превращения (преобразования) аналогового сигнала в ступенчатую функцию с одинаковой шириной ступенек и различной амплитудой, зависящей от скорости изменения речевого сигнала между стробирующими импульсами. Он позволяет снизить требования к компаратору по верхней рабочей частоте для обеспечения работы по низко- и среднескоростным цифровым каналам связи.

Компаратор 3 представляет собой схему сравнения и предназначен для формирования сигнала на своем выходе в зависимости от уровня напряжения сигналов, поступающих на его первый и второй входы.

В качестве компаратора 3 может быть использована интегральная микросхема серии К554 типа К554СА2 [1, с.463].

Триггер типа JK (JK триггер) 5 совместно с инвертором 4 служит для формирования дискретной последовательности в соответствии с тактовой частотой стробирующих импульсов, поступающих с выхода генератора 13 тактовых импульсов.

В качестве JK триггера 5 может быть использован триггер серии К561 типа К561 ТВ1 [1, с.319].

Схема адаптации 6 передачи в составе делителя напряжения 7, операционного усилителя 8 передачи, первого 9, второго 10 и третьего 12 резисторов и конденсатора 12 предназначена для формирования информационного сигнала из выходной последовательности импульсов, образованной JK триггером 5 и поступающей на вход цифрового канала 27 связи, и слежения за уровнем входного сигнала, поступающего на первый вход компаратора 3, с целью нивелирования изменяющейся амплитуды речевого сигнала. Соединенные параллельно второй резистор 10 и конденсатор 11 выполняют роль интегратора (RC цепочка).

Делитель 7 напряжения выполнен в виде двух последовательно соединенных резисторов, напряжение питания снимается со средней точки (точки соединения резисторов между собой).

Операционные усилители передачи 8 и приема 20 выполняют одинаковые функции и имеют одинаковую структуру. В качестве операционных усилителей могут быть использованы микросхемы серии К553 типа К553 УД2 [1, с.461].

Усилитель 15 декодера 14 предназначен для усиления и формирования (нормирования) амплитуды дискретного сигнала, поступающего с выхода цифрового канала 27 связи.

Аналоговый ключ 16 обеспечивает восстановление амплитуды поступающих импульсов дискретной последовательности.

Фильтр 17 нижних частот предназначен для исключения высокочастотных составляющих из принятой из цифрового канала 27 связи последовательности дискретных импульсов, модулированных по амплитуде.

Схема 18 адаптации приема декодера 14 в составе делителя 19 напряжения, операционного усилителя 20 приема, первого 21, второго 22 и третьего 24 резисторов и конденсатора 23 предназначена для восстановления сигнала адаптации из дискретной последовательности, поступающей из цифрового канала 27 связи через усилитель 15 путем извлечения сигнала адаптации из принятой двоичной последовательности, а также для управления величиной ступеньки дискретизации при восстановлении на приеме. Соединенные параллельно второй резистор 22 и конденсатор 23 выполняют роль интегратора (RC цепочка).

Принцип работы схемы адаптации заключается в закладке сигнала адаптации в последовательность передаваемых импульсов дискретного сигнала. При этом при отсутствии речевого сигнала на входе кодера в цифровой канал (или линию) связи поступает чистый меандр, который на приемной стороне на выходе декодера генерирует нулевую линию (отсутствие сигнала), а при появлении на входе кодера речевого сигнала на выходе кодера на слоговом интервале появляются дискретные последовательности импульсов (единиц или нулей), которые определяют величину сформированного порога дискретизации по амплитуде.

Напряжение адаптации, усредненное по времени интегратором (цепочкой RC), следит за средней величиной поступающего на первый вход компаратора ступенчатого сигнала. Если на первом входе компаратора напряжение сигнала превышает напряжение адаптации, поступающее с выхода схемы адаптации (с третьего резистора) на второй вход компаратора, то на его выходе появляется единица, если напряжение на первом входе компаратора меньше, то на его выходе появляется ноль.

Если мгновенное значение речевого сигнала делает резкий выброс, то на выходе компаратора следуют единицы и напряжение адаптации начинает возрастать, пытаясь следить за входным сигналом. Когда мгновенное значение речевого сигнала начинает спадать, напряжение на первом входе компаратора становится меньше напряжения адаптации и на его выходе появляются нули.

При медленном возрастании мгновенного значения речевого сигнала в выходной последовательности двоичного сигнала преобладают единицы, при медленном убывании мгновенного значения речевого сигнала в выходной последовательности двоичного сигнала преобладают нули.

В связи с тем, что адаптация в кодере и декодере управляется одной и той же дискретной последовательностью, сформированной на выходе JK триггера, то в декодере восстанавливается тот же сигнал, который поступал на вход компаратора. При поступлении на вход кодера участка речевого сигнала с большой амплитудой, например свистящий звук, сигнал адаптации увеличивает ступеньку дискретизации в кодере и, соответственно, увеличивает амплитуду импульсов в декодере.

В предлагаемом адаптивном дельта-кодеке, если рассматривать по аналоговому сигналу, имитируется процесс загиба частотной характеристики в сторону высоких частот и восстановление ее на приеме.

Использование предлагаемого принципа адаптации в дельта-кодеке способствует повышению точности передачи речевого сигнала за счет уменьшения шумов дискретизации для высокочастотных составляющих и не требует выделения специального канала связи для передачи сигнала частотной корректировки.

Усиленный и откорректированный по спектру сигнал с микрофона от источника 25 аналогового сигнала поступает на вход дискретизатора 2, который фиксирует мгновенное значение речевого сигнала в момент прихода тактового импульса. Это значение сигнала поступает на первый вход компаратора 3, который сравнивает его с напряжением на конденсаторе 11, поступающим с его первого вывода через третий резистор 12 на второй вход компаратора 3.

Если напряжение сигнала, поступившего на первый вход компаратора 3, больше напряжения на втором входе, то на выходе компаратора 3 появляется высокий потенциал, который фиксируется тактовым импульсом в виде единицы в JK триггере 5. Если напряжение на первом входе компаратора 3 ниже напряжения на его втором входе, то в триггере 5 фиксируется ноль.

Последовательность единиц и нулей с выхода триггера 5 формирует на конденсаторе 11 опорное напряжение. Скорость накопления заряда на емкости конденсатора 11 и скорость ее разряда устанавливаются выбором постоянной времени цепочки RC (второй резистор 10 и конденсатор 11). При исчезновении сигнала на входе дискретизатора 2 аналогового сигнала напряжение на конденсаторе 11 должно стремиться к нулю, поскольку конденсатор будет интенсивно разряжаться отрицательным потенциалом с выхода операционного усилителя 8. Подходя к этому вопросу с несколько другой стороны, следует отметить, что постоянная времени цепочки RC определяет сквозную частотную характеристику кодека. Именно по этому показателю выбирается постоянная времени цепочки RC (второго резистора 10 и конденсатора 11).

Рассмотрим принцип работы декодера (см. фиг.1).

Двоичный сигнал поступает с выхода цифрового канала 27 связи через усилитель 15 на вход операционного усилителя 20 приема. Из двоичной последовательности с помощью операционного усилителя 20 и цепочки RC (второй резистор 22 и конденсатор 23) выделяется напряжение адаптации. Это напряжение определяет величину двоичных импульсов на выходе схемы адаптации 18, следующих с тактовой частотой.

На тех участках двоичной последовательности, где в исходном речевом сигнале быстро нарастало мгновенное значение напряжения, амплитуда импульсов двоичной последовательности на выходе аналогового ключа 16 будет иметь большую амплитуду, что обеспечит быстрое возрастание мгновенного напряжения на выходе фильтра 17 нижних частот.

Техническая эффективность от предлагаемого адаптивного дельта-кодека заключается в повышении качества телефонной связи при работе по низкоскоростным цифровым каналам связи, достигаемого за счет улучшения качества кодирования речевого сигнала на низких скоростях в абонентской линии, к которой подключен телефонный аппарат со встроенным адаптивным дельта-кодеком, уменьшения перегрузки дельта-кодера по крутизне нарастания речевого сигнала, исключения или уменьшения шумов в паузах речи на выходе декодера при отсутствии речевого сигнала на входе кодера путем введения слоговой адаптации величины ступеньки дискретизации аналогового сигнала, автоматической закладки параметров адаптации в последовательность передаваемых импульсов дискретного сигнала и извлечения этой информации в декодере для восстановления исходного сигнала.

Достоинством предлагаемого изобретения является также и то, что заложенный в нем принцип адаптации способствует повышению точности передачи речевого сигнала за счет уменьшения шумов дискретизации для высокочастотных составляющих и не требуется выделение отдельного (специального) канала связи только для передачи сигнала частотной корректировки.

Применение для реализации предлагаемого адаптивного дельта-кодека стандартных однотипных элементов способствовало также упрощению схемы устройства и повышению надежности ее работы, снижению массогабаритных характеристик, что дало возможность встраивать дельта-кодек в схему телефонного аппарата без увеличения его массогабаритных характеристик.

Изготовлен макет предлагаемого дельта-кодека и проведены его испытания. Результаты испытаний подтвердили его работоспособность и возможность промышленного применения.

Источник информации

1. Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др.: Под ред. Б.В. Тарабрина. - М.: Радио и связь, 1984, с.319, 461, 463.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1989 |

|

SU1688412A1 |

| Кодек адаптивного дельта-модулятора | 1986 |

|

SU1378063A1 |

| УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА В ЦИФРОВУЮ ФОРМУ, УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ МНОЖЕСТВА ДВОИЧНО-КОДИРОВАННЫХ ЧИСЛОВЫХ ОТСЧЕТОВ СИГНАЛА В АНАЛОГОВЫЙ СИГНАЛ | 1994 |

|

RU2159505C2 |

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

| Адаптивный дельта-кодер для каналов тональной частоты цифровых систем связи | 1982 |

|

SU1091338A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО РАДИОСВЯЗИ И МНОГОРЕЖИМНЫЙ СОТОВЫЙ РАДИОТЕЛЕФОН | 1993 |

|

RU2128886C1 |

| ЦИФРОВАЯ СИСТЕМА СВЯЗИ | 2011 |

|

RU2454793C1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

Изобретение относится к устройству преобразования речевых сигналов из аналоговой в цифровую форму в цифровых телефонных аппаратах. Технический результат заключается в повышении качества передачи речевого сигнала по цифровым каналам связи с малой скоростью передачи при одновременном упрощении схемы устройства. Адаптивный дельта-кодек включает источник и приемник аналогового сигнала, цифрового канала связи, кодер, содержащий дискретизатор аналогового сигнала, компаратор, инвертор, JK триггер, схему адаптации передачи, включающую в себя делитель напряжения, операционный усилитель передачи, первый, второй и третий резисторы, конденсатор, а также содержащий генератор тактовых импульсов (ГТИ), а также декодер, содержащий усилитель, аналоговый ключ, фильтр нижних частот, схему адаптации приема, включающую в себя делитель напряжения, операционный усилитель приема, первый, второй и третий резисторы, конденсатор. 2 ил.

Адаптивный дельта-кодек, состоящий из кодера, содержащего дискретизатор аналогового сигнала, компаратор, инвертор, JK триггер, схему адаптации передачи, включающую в себя делитель напряжения, операционный усилитель передачи, первый, второй и третий резисторы, конденсатор, а также содержащего генератор тактовых импульсов (ГТИ); декодера, содержащего усилитель, аналоговый ключ, фильтр нижних частот, схему адаптации приема, включающую в себя делитель напряжения, операционный усилитель приема, первый, второй и третий резисторы, конденсатор, источника и приемника аналогового сигнала, цифрового канала связи, при этом выход дискретизатора аналогового сигнала кодера соединен с первым входом компаратора, выход которого через инвертор подключен к первому (К) входу и непосредственно ко второму (J) входу JK триггера, выход которого соединен со входом цифрового канала связи и с первым входом операционного усилителя передачи схемы адаптации передачи, ко второму входу которого подключено питающее напряжение с делителя напряжения, выход которого соединен с первым выводом первого резистора, второй вывод которого соединен с первыми выводами второго и третьего резисторов и конденсатора, второй вывод которого соединен со вторым выводом второго резистора и с корпусом источника питания, второй вывод третьего резистора соединен со вторым входом компаратора, выход генератора тактовых импульсов, используемых в качестве стробирующих импульсов, соединен с установочным входом JK триггера и с управляющим входом дискретизатора аналогового сигнала, к питающему входу которого подключен корпус источника питания, а информационный вход дискретизатора аналогового сигнала соединен с выходом источника аналогового сигнала, выход цифрового канала связи соединен со входом усилителя декодера, выход которого соединен с управляющим входом аналогового ключа и с первым входом операционного усилителя приема схемы адаптации приема, ко второму входу которого подключено питающее напряжение с делителя напряжения, выход операционного усилителя приема соединен с первым выводом первого резистора, второй вывод которого соединен с первыми выводами второго и третьего резисторов и конденсатора, второй вывод которого соединен со вторым выводом второго резистора и с корпусом источника питания, второй вывод третьего резистора соединен со входом аналогового ключа, выход которого соединен со входом фильтра нижних частот, выход которого соединен с приемником аналогового сигнала, при этом информационный вход дискретизатора аналогового сигнала кодера является входом адаптивного дельта-кодека, выходом которого является выход JK триггера кодера, соединенный со входом цифрового канала связи, канальным входом дельта-кодека является вход усилителя декодера, соединенный с выходом цифрового канала связи, выход фильтра нижних частот декодера является информационным выходом аналогового сигнала адаптивного дельта-кодека, который соединен со входом приемника аналогового сигнала.

| US 6204793 B1, 20.03.2001 | |||

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| RU 2053566 C1, 27.01.1996 | |||

Авторы

Даты

2014-10-10—Публикация

2013-03-19—Подача