ЬГ5

}б

(Л

4i 4 4Sb СО СП 4

I

Изобретение относится к вычислиельной технике и технике связи и моет быть использовано в системах пеедачи информации, например, в элек- ронных и квазиэлектронных АТС.

Цель изобретения - повьшение .точости декодирования.

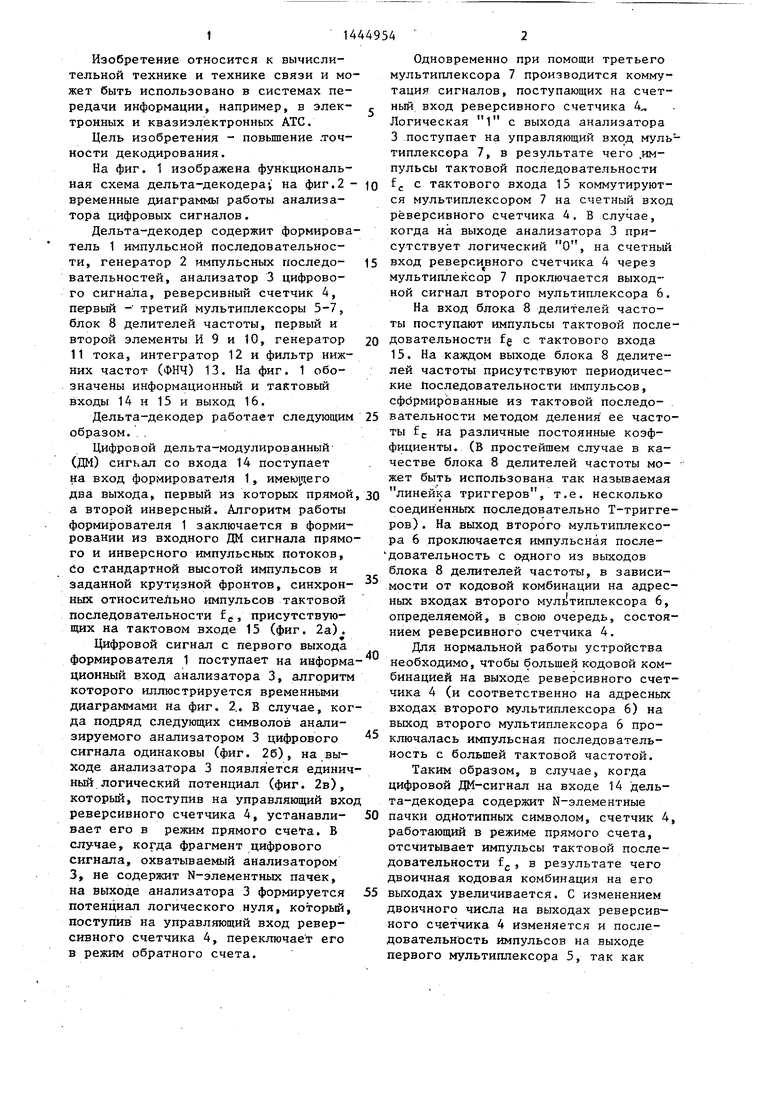

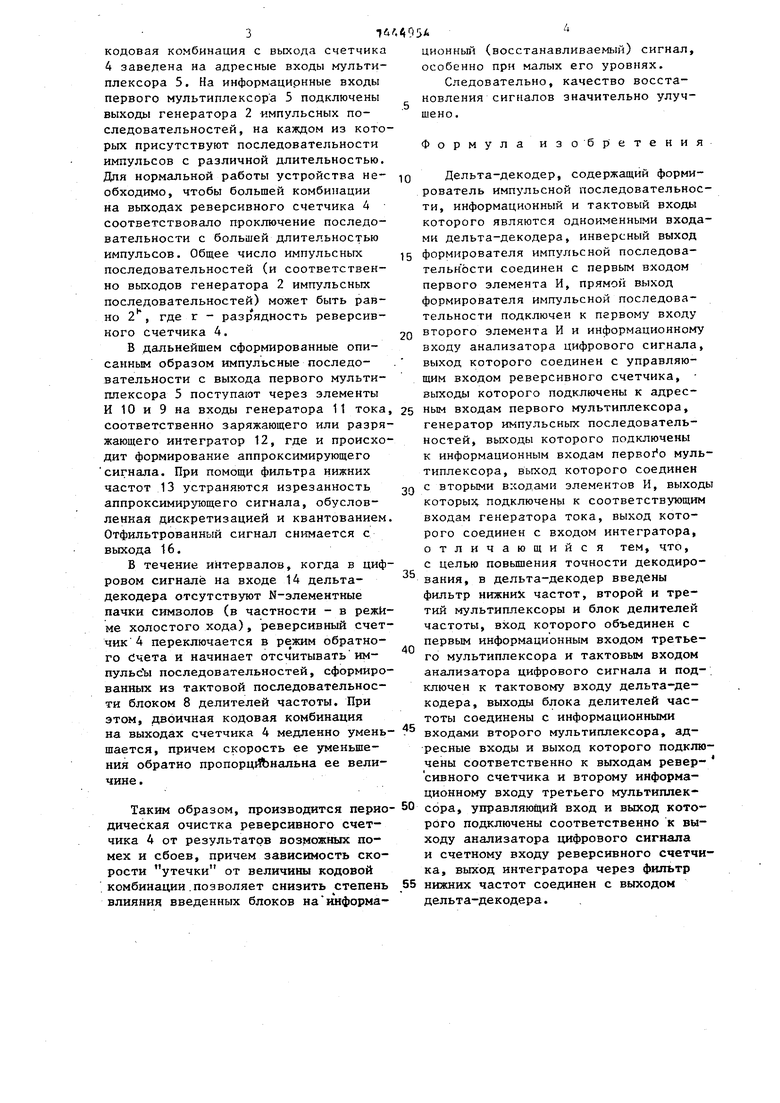

На фиг, 1 изображена функциональная схема дельта-декодера; на фиг.2 - ю ременные диаграммы работы анализаора цифровых сигналов.

Дельта-декодер содержит формирователь 1 импульсной последовательности, генератор 2 импульсных последо- 15 вательностей, анализатор 3 цифрового сигнала, реверсивный счетчик 4, первый - третий мультиплексоры 5-7, блок 8 делителей частоты, первый и второй элементы И 9 и 10, генератор 20 11 тока, интегратор 12 и фильтр нижних частот (ФНЧ) 13. На фиг. 1 обо- значены информационный и тактовый входы 14 и 15 и выход 16.

Дельта-декодер работает следующим 25 образом. . .

Цифровой дельта-модулированный- (дм) сигнал со входа 14 поступает на вход формирователя 1, име101,чего два выхода, первый из которых прямой, ЗО а второй инверсный. Алгоритм работы формирователя 1 заключается в формировании из входного ДМ сигнала прямого и инверсного импульсных потоков, Со стандартной высотой импульсов и заданной крутизной фронтов, синхронных относительно импульсов тактовой последовательности f , присутствующих на тактовом входе 15 (фиг. 2а).

Цифровой сигнал с первого выхода формирователя 1 поступает на информационный вход анализатора 3, алгоритм которого иллюстрируется временными диаграммами на фиг. 2., В случае, когда подряд следующих символов анализируемого анализатором 3 цифрового сигнала одинаковы (фиг. 26), на выходе анализатора 3 появляется единичный логический потенциал (фиг. 2в), который, поступив на управляющий вход реверсивного счетчика 4, устанавли- 50 вает его в режим прямого счета. В случае, когда фрагмент цифрового сигнала, охватываемый анализатором 3, не содержит N-элементных пачек, на выходе анализатора 3 формируется 55 потенциал логического нуля, который, постуйив на управляющий вход реверсивного счетчика 4, переключает его в режим обратного счета.

Одновременно при помощи третьего мультиплексора 7 производится коммутация сигналов, поступающих на счетный вход реверсивного счетчика 4 Логическая 1 с выхода анализатора 3 поступает на управляющий вход мультиплексора 7, в результате чего .импульсы тактовой последовательности fj. с тактового входа 15 коммутируются мультиплексором 7 на счетный вход реверсивного счетчика 4. В случае, когда на выходе анализатора 3 присутствует логический О, на счетный вход реверсивного счетчика 4 через мультиплексор 7 проключается выходной сигнал второго мультиплексора 6.

На вход блока 8 делителей частоты поступают импульсы тактовой последовательности fg с тактового входа 15. На каждом выходе блока 8 делителей частоты присутствуют периодические Последовательности импульсов, сформированные из тактовой последовательности методом деления ее частоты ЕС на различные постоянные коэффициенты. (В простейшем случае в качестве блока 8 делителей частоты может быть использована так называемая линейка триггеров, т.е. несколько соединенных последовательно Т-тригге ров). На выход второго мультиплексора 6 проключается импульсная после- довательность с одного из выходов блока 8 делителей частоты, в зависимости от кодовой комбинации на адресных входах второго мул11типлексора 6, определяемой, в свою очередь, состоянием реверсивного счетчика 4.

Для нормальной работы устройства необходимо, чтобы большей кодовой комбинацией на выходе реверсивного счетчика 4 (и соответственно на адресных входах второго мультиплексора 6) на выход второго мультиплексора 6 про- ключалась импульсная последовательность с большей тактовой частотой.

Таким образом, в случае, когда цифровой да-сигнал на входе 14 дельта-декодера содержит N-элементные пачки однотипных символом, счетчик 4 работающий в режиме прямого счета, отсчитывает импульсы тактовой последовательности f, в результате чего двоичная кодовая комбинация на его выходах увеличивается. С изменением двоичного числа на выходах реверсивного счетчика 4 изменяется и последовательность импульсов на выходе первого мультиплексора 5, так как

кодовая комбинация с вькода счетчика 4 заведена на адресные входы мультиплексора 5. На информацирнные входы первого мультиплексора 5 подключены выходы генератора 2 импульсных последовательностей, на каждом из которых присутствуют последовательности импульсов с различной длительностью. Дпя нормальной работы устройства необходимо, чтобы большей комбинации на выходах реверсивного счетчика 4 соответствовало проключение последовательности с большей длительностью импульсов. Общее число импульсных последовательностей (и соответственно выходов генератора 2 импульсных последовательностей) может быть равно 2 , где г - разрядность реверсивного счетчика 4.

В дальнейшем сформированные описанным образом импульсные последовательности с выхода первого мультиплексора 5 поступают через элементы И 10 и 9 на входы генератора 11 тока соответственно заряжающего или разряжающего интегратор 12, где и происходит формирование аппроксимирующего сигнала. При помощи фильтра нижних частот 13 устраняются изрезанность аппроксимирующего сигнала, обусловленная дискретизацией и квантованием Отфильтрованный сигнал снимается с выхода 16.

В течение интервалов, когда в цифровом сигнале на входе 14 дельта- декодера отсутствуют N-элементные пачки символов (в частности - в режиме холостого хода), реверсивный счетчик 4 переключается в режим обратного Счета и начинает отсчитывать им- пульс Ь последовательностей, сформированных из тактовой последовательности блоком 8 делителей частоты. При этом, двоичная кодовая комбинация на выходах счетчика 4 медленно уменьшается, причем скорость ее уменьшения обратно пропорциональна ее величине .

0

0

ционньп (восстанавливаемый) сигнал, особенно при малых его уровнях.

Следовательно, качество восстановления сигналов значительно улучшено.

Формула изобретения

Дельта-декодер, содержащий формирователь импульсной последовательности, информационный и тактовый входы которого являются одноименными входами дельта-декодера, инверсный выход 5 формирователя импульсной последова- тельн ости соединен с первым входом первого элемента И, прямой выход формирователя импульсной последовательности подключен к первому входу второго элемента И и информационному входу анализатора цифрового сигнала, выход которого соединен с управляющим входом реверсивного счетчика, выходы которого подключены к адресным входам первого мультиплексора, генератор импульсных последовательностей, выходы которого подключены к информационным входам первог о мультиплексора, вьжод которого соединен с вторыми входами элементов И, выходы которые подключены к соответствующим входам генератора тока, выход которого соединен с входом интегратора, отличающийс я тем, что, с целью повьш1ения точности декодирования, в дельта-декодер введены фильтр нижних частот, второй и третий мультиплексоры и блок делителей частоты, вход которого объединен с первым информационным входом третьего мультиплексора и тактовым входом анализатора цифрового сигнала и подключен к тактовому входу дельта-декодера, выходы блока делителей частоты соединены с информационными входами второго мультиплексора адресные входы и выход которого подключены соответственно к выходам ревер- сивного счетчика и второму информа5

0

5

0

5

ционному входу третьего мультиплек- Таким образом, производится перио- 50 сора, управляющий вход и выход котодическая очистка реверсивного счетчика 4 от результатов возможных помех и сбоев, причем зависимость скорости утечки от величины кодовой комбинации.позволяет снизить степень влияния введенных блоков на информа55

рого подключены соответственно к выходу анализатора цифрового сигнала и счетному входу реверсивного счетчика, выход интегратора через фильтр нижних частот соединен с выходом дельта-декодера.

y(t)

8

У%)

пд

(.2

| Патент США № 3500441, | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Дельта-декодер с экспандированием | 1976 |

|

SU594583A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-22—Подача