два группы в каждом канале соединен с соответствующим вхоэлемента И своего

дам третьего капала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многорежимное устройство приоритета | 1990 |

|

SU1805469A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1596338A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство переменного приоритета | 1988 |

|

SU1571584A1 |

| Устройство для сопряжения к абонентов с М вычислительными машинами | 1987 |

|

SU1411758A1 |

| Многоканальное устройство для обслуживания групповых запросов | 1981 |

|

SU1005054A1 |

| Устройство управления прерываниями | 1982 |

|

SU1242948A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Многоканальное устройство для приоритетного подключения источников информации к мультишинной магистрали | 1989 |

|

SU1647564A1 |

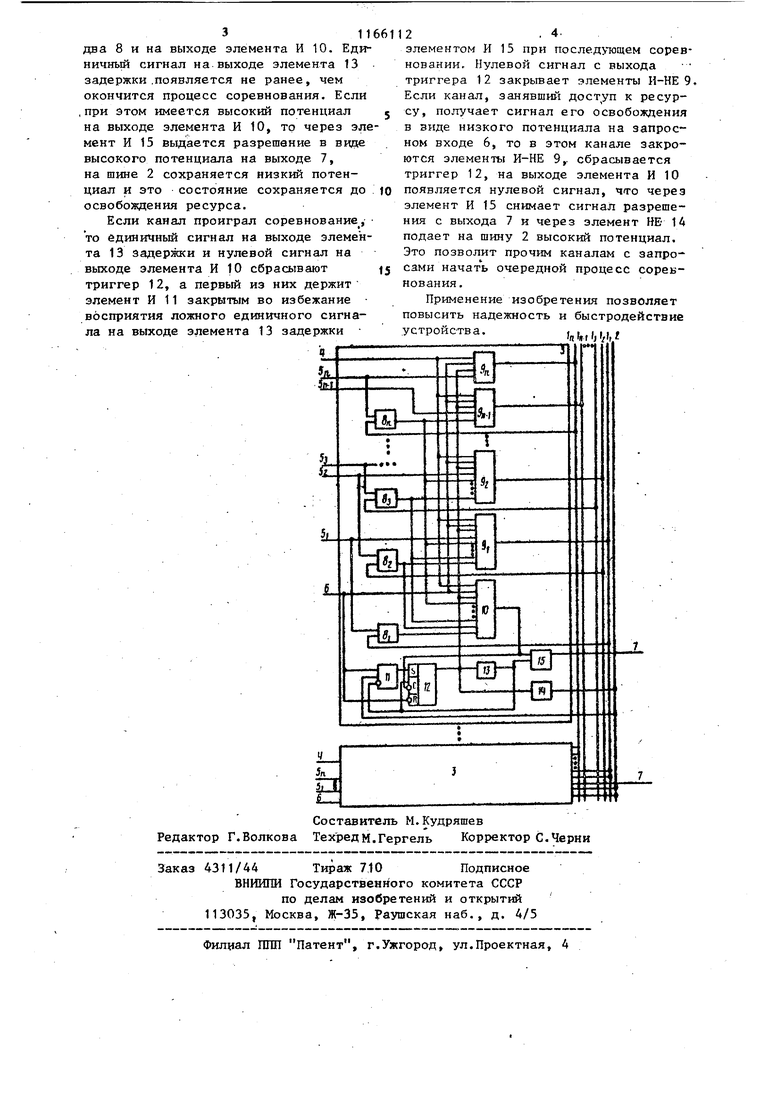

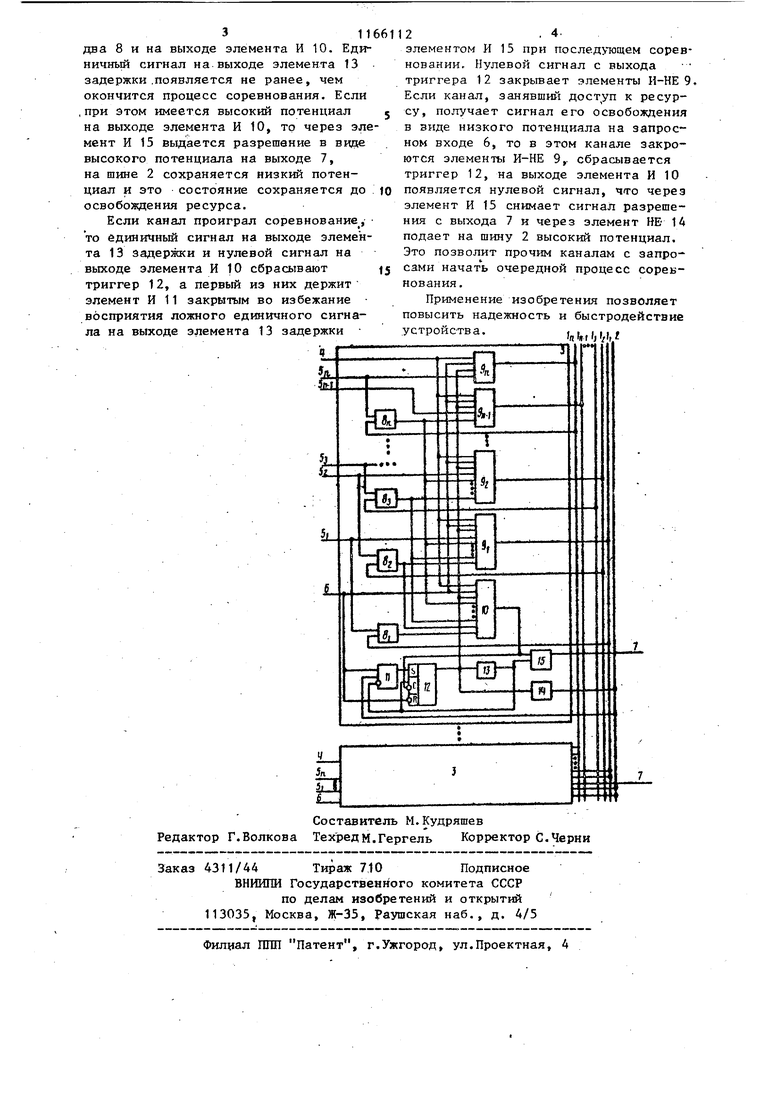

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА, содержащее в каждом канале три элемента И, триггер, элемент задержки, элемент НЕ, причем каждый /-Й запросный вход устройства (t 1, ...,п , где h - число запросов) соединен с первым входом первого . . элемента Иi-го канала, второй вход первого элемента И каждого канала соединен с выходом элемента задержки своего канала, единичный выход триггера канала соединен с входом элемента НЕ своего канала, выходы элемен- . тов НЕ каналов соединены с выходом запрета устройства, выход второго элемента И каждого канала является соответствующим сигнальным выходом устройства, выход первого элемента И соединен с единичным входом триггера своего канала, отличающеес я тем, что, с целью поввшения надежности за счет исключения возможности появления ложных сигналов на выходе устройства и повышения его быстродействия, оно содержит в каждом канале группу элементов ИНЕ, группу элементов сложения по модулю, два, причем в каждом канале стробирующий вход устройства соедиг / % нен с первыми входами всех элементов И-НЕ группы и с первым входом третьего элемента И, каждый i -и вход 4-й группы кодовых входов устройства соединен с вторым входом i -го элемента И-НЕ группы i -го канала и с первым входом 1-го элемента ело жения по модулю два группы i -го канала, выходы 1-х элементов И-НЕ группы каналов объединены по схеме ИЛИНЕ, соединены с i -м информационным выходом устройства и с вторым входом J -го элемента сложения по модулю два, каждый 1-й запросный вход устройства соединен с третьими входами элементов И-НЕ группы i -го канала, с вторым входом третьего элемента И (Л и с асинхронным нулевым входом триг- гера 1 -го канала, выход каждо.го i -го элемента сложения по модулю два (i n, ..., 2) соединен с соответствующим входом (i-l)-ro и следующих элементов И-НЕ группы и с соответствующим входом третьего элемента И а своего канала, выход третьего элемена та И соединен с первым входом второго элемента И своего канала, с синхронизируемым нулевым входом триггера своего канала, выход запрета устройства соединен с третьим входом первого элемента И каждого канала, единичный выход триггера канала соединен с входом элемента задержки, с соответствующим входом третьего элемента И, с соответствующими входами элементов И-НЕ группы своего канала, выход элемента задержки соединен с синхронизирующим входом триггера своего канала, и с вторым входом второго элемента И своего канала, выход первого элемента сложения по модулю

Изобретение относится к вычислительной технике и предназначено как для взаимного исключения доступа нескольких процессоров к общему ресурсу, так и для выбора одного из запросов прерывания процессора, выра батьшаемых переферийными устройствами. Целью изобретения является повышение надежности устройства за счет исключения возможности появления ложных сигналов на выходе устройства и повышение его быстродействия. Приоритетный код канала - двоичны нормальный код, причем приоритет возрастает с увеличением неотрицательного целого представляемого кодо числа. Задержка, выполняемая элементом задержки, должна быть не менее суммы максимальных времен задержки распространения в элементе НЕ, по ш не захвата, в триггере, в элементе НЕ, по кодовым входам, в элементе сложения по модулю два и в первом элементе И. На чертеже показана структурная схема предлагаемого устройства. Устройство содержит информационные выходы 1 устройства, выход 2 запрета устройства, каналы 3, а в ка дом канале - стробирующий вход ,4, кодовые входа 5 устройства, запросный вход 6 устройства, сигнальный выход 7 устройства, элементы 8 сложения по модулю два, элементы ИНЕ 9, элемент И 10, элемент И 11, триггер 12, элемент 13 задержки, элемент НЕ 14, элемент И 15. Процес ,соры или периферийные устройства мо гут быть соединены с каналами посред ством запросного входа, сигнального выхода, во втором случае процессор, (или процессоры) подключаются к выхо дам 1 для получения кода периферийно го устройства и к шине 2 (через элемент задержки) для получения sanpdca прерывания. Приоритетный код в каждом канале может быть постоянным или переменным, но в любой момент времени коды любых двух каналов не должны совпадать. Стробирующий вход 4 может быть использован для маскирования каналов. Устройство работает следующим образом. В исходном состоянии на всех выходах 1 и шине 2 - высокий потенциал, триггеры 12 всех каналов 3 сброшены, на входах 6 и выходах 7 высокий потенциал. Это состояние сохраняется до появления запроса, т.е. высокого потенциала на стробирующем 4 и запросном входе 6 хоть в одном канале. I При появлении в канале запроса открывается элемент И 11 и снимается запрет на переход триггера 12 в единичное состояние. В каждом канале, получившем запрос при высоком потенциале на шине 2, единичный сигнал с выхода элемента И 11 устанавливает триггер 12 в единичное состояние, а единичный сигнал с выхода этого триггера открывает элементы И-НЕ 9 для участия в соревновании через элемент НЕ 14 устанавливает низкий потенциал на шине 2, что препятствует прочим каналам пр.инять участие в соревновании. Соревнованием является переходный процесс, в ходе которого каждый канал подает на выход 1 инверсный сигнал со входа 5, если инверсное содержимое выходов 1 равно значениям кодовых разрядов. Если при-этом хоть один канал подает на выход 1 низкий потенциал, то он и устанавливается на выходе 1, иначе на этом выходе будет высокий потенциал. При этом каналы, имеющие на входе 5 низкий потенциал, проигрывают соревнование, если выход 1 содержит низкий потенциал. Канал, выигравший соревнование, имеет высокий потенциал на выходах всех своих элементов сложения по модулю

| Многоканальное устройство для подклю-чЕНия иСТОчНиКОВ иНфОРМАции K ОбщЕйМАгиСТРАли | 1979 |

|

SU807298A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство приоритета | 1978 |

|

SU798839A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| ; | |||

Авторы

Даты

1985-07-07—Публикация

1983-07-14—Подача