f

Изобретение относится к вычислительной технике и может быть применено, в частности, в многопрограммных, многопроцессорных системах

Цель изобретения - упрощение устройства.

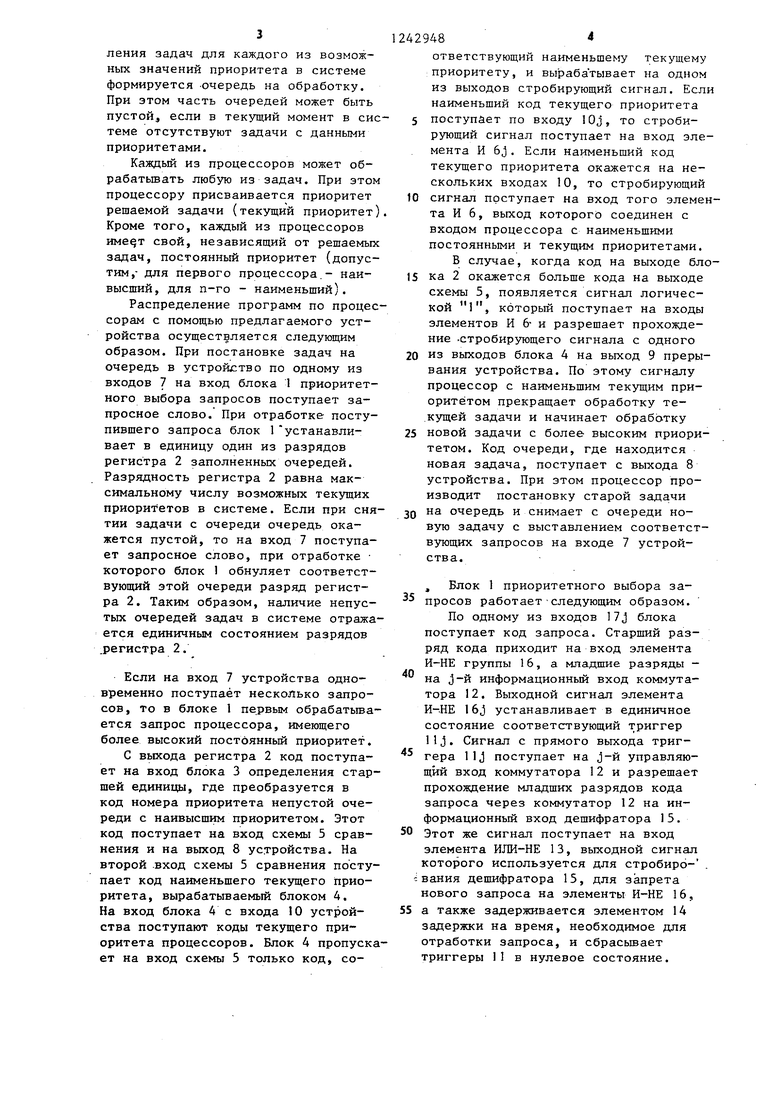

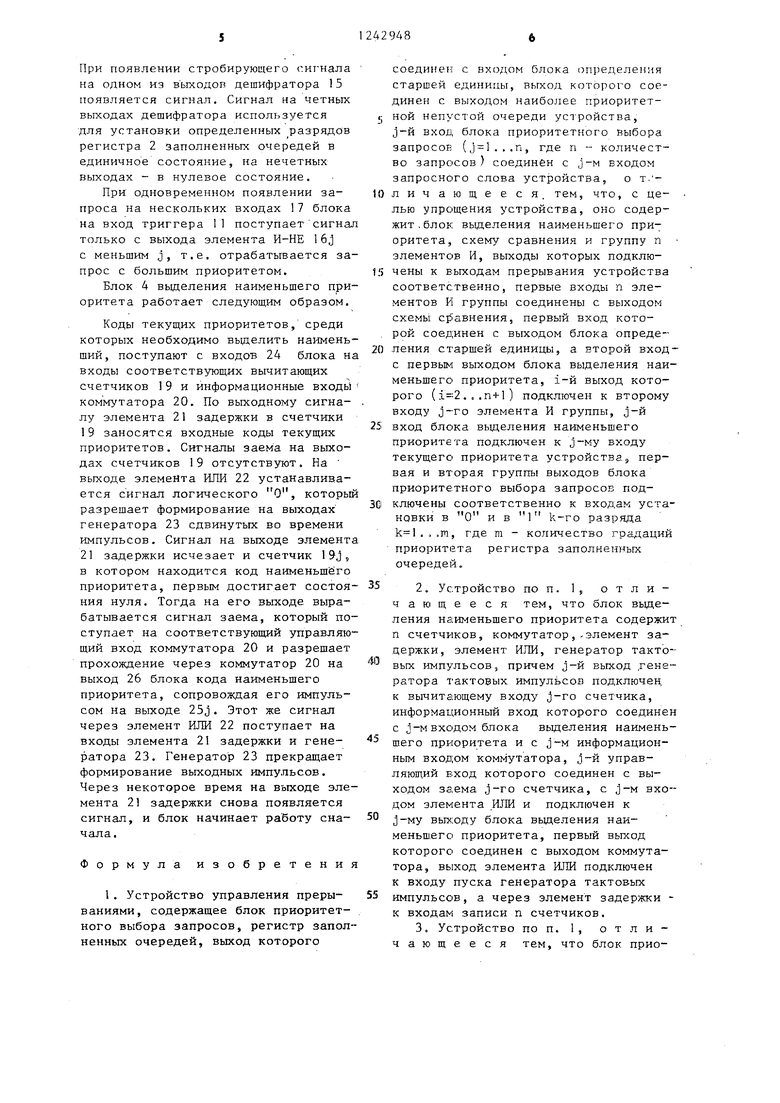

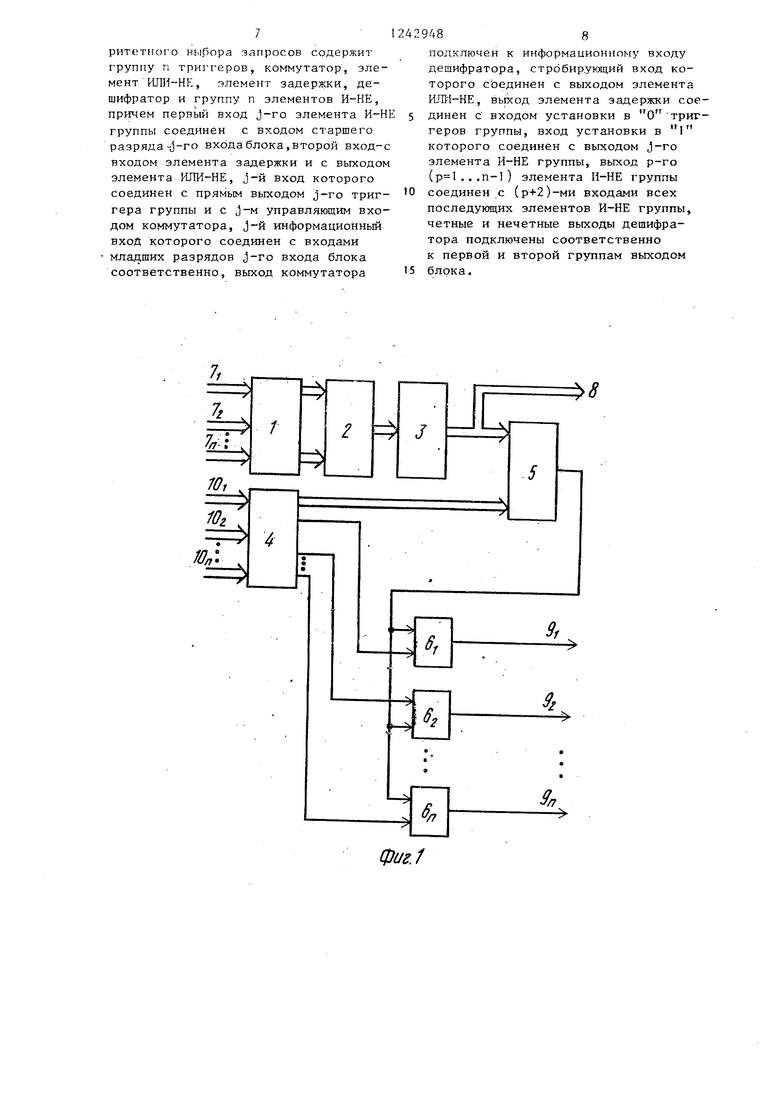

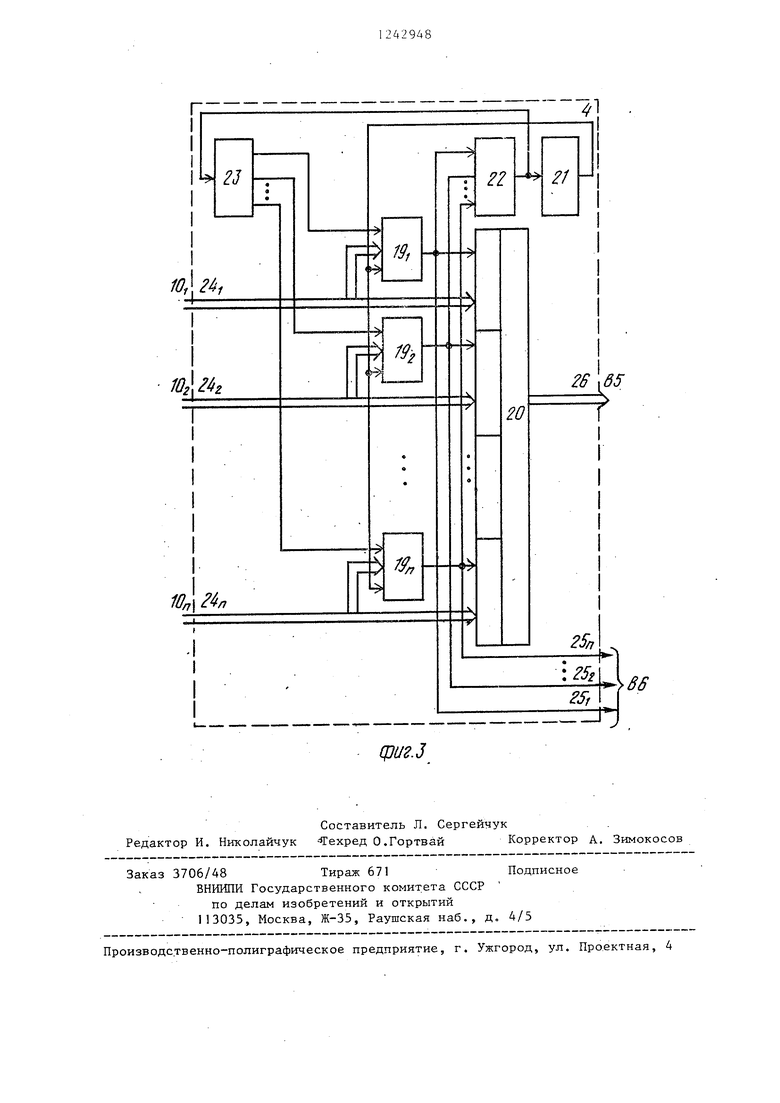

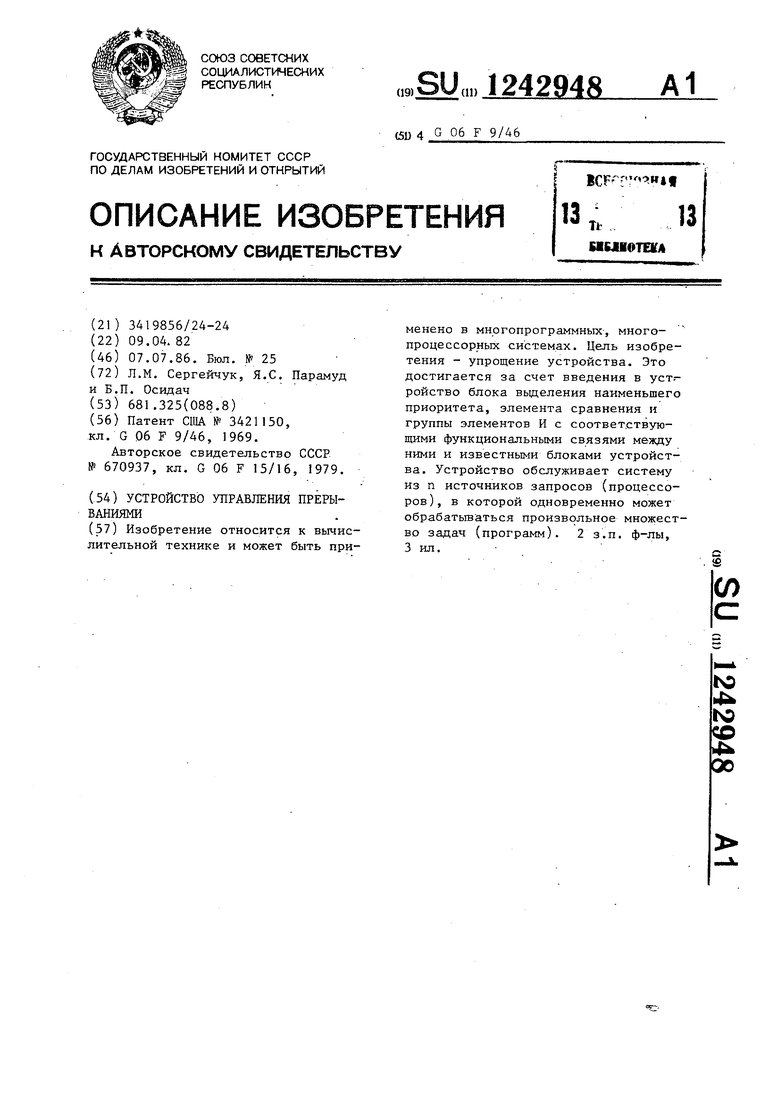

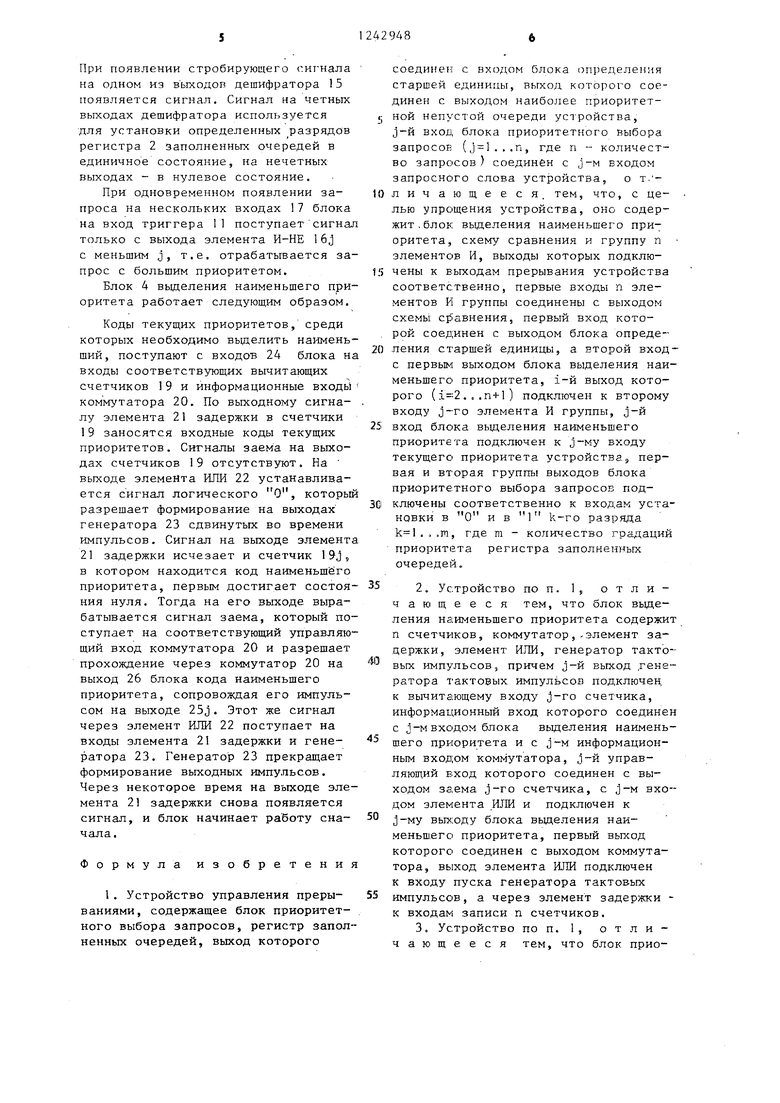

На фиг. 1 показана схема устройства управления прерываниями; на фиг. 2 - схема блока вьщеления наименьшего приоритета; на фиг. 3 - схема блока приоритетного выбора запросов.

Устройство управления прерываниями содержит (фиг. 1) блок 1 приоритетного выбора запросов, регистр 2 заполненных очередей, блок 3 опре-т деления старшей единицы, блок 4 выделения наименьшего приоритета, схему 5 сравнения и группу 6 элементов И. Входы блока 1 соединены с входами 7 запросного слова устройства. Первая группа вьгходов блок

Iподключена к входам установки в о, а вторая группа выходов - к входам установки в 1 соответствующих разрядов регистра 2 заполненных очередей. Устройство имеет такж выход 8. Выход регистра 2 соединен

с входом блока 3 определения старше единицы, выход которого подключен к выходу наиб.олее приоритетной непустой очереди устройства и к первому входу схемы 5 сравнения. Второй вхо схемы 5 сравнения соединен с первым выходом блока 4 выделения наименьшего приоритета, а выход подключен к первым входам элементов И группы 6. Вторые входы.элементов И группы 6 соединены с соответствующими выходами блока 4, а выходы подключены к соответствуюш,им выходам 9 устройства. Входы блока 4 соединены с соответствующими входами 10 тек ущего приоритета устройства.

Блок 1 приоритетного выбора запросов (фиг. 2) содержит группу

IIиз п триггеров, где п количество запросов, коммутатор

12, элемент И-НЕ 13, элемент 14 задержки, дешифратор 15 и группу 16 элементов И-НЕ. Первые входы элементов И-НЕ группы 6 соединены с входом старшего разряда соответствующих входов 17 блока, вторые вход с входом элемента 14 задержки, выходом элемента ИЛИ-НЕ 13 и стробиру щим входом дешифратора 15, входы элемента ИЛИ-НЕ 13 подключены к пря

2А2д482

мьпм выходам соответствующих триг - геров 1 1 и к соответствующр м управляющим входам коммутатора 12, информационные входы которого соединены с

5 входами младших разрядов соответствующих входов 17 блока. Выход элемента 14 задержки подключен к входам установки в О триггеров И. Вход установки в 1 триггера llj,

0 где j- l , 2,..., п, соединен с выходом элемента И-НЕ 16j и с (+2)-ми входами остальных (n-j) элементов И-НЕ группы 16. Выход коммутатора i 2 подключен к информационному вхоiS ду дешифратора 15. Четные и нечетные выходы дешифратора 15 подключены соответственно к первой и второй группгш выходов .18 блока.

Блок 4 выделения наименьшего при20. оритета (фиг. З) содержит п счетчиков 19, коммутатор 20, элемент 21 задержки, элемент ИЛИ 22, генератор 23 тактовых импульсов. Вьмитающий вход счетчика 1 9j

25 (j-l, 2, ..., n) соединен с i-м выходом генератора 23 тактовых- импульсов , а информационный вход соединен с входом 24j блока и с j-м информационным входом коммутатора

30 20. Выход заема счетч 1ка 19J подключен к j-му управляющему входу коммутатора 20, к J-му входу элемента ИПИ 22 и к выходу 25j блока. Выход элемента ИЛИ 22 соединен с входом

25 пуска генератора 23 и с входом элемента. 21 задержки, выход которого подключен к входам записи счетчиков 19. В.ЫХОД коммутатора 20 соединен с выходом 26 блока 4 выделения наиг

40 меньшего приоритета.

Устройство работает следующим образом.

Устройство обслуживает систему из п источников запросов (процессоров), в которой одновременно может обрабатываться произвольное множество задач (программ). С течением времени количество задач в системе изменяется: при необходимости извне

- через каждый процессор в -систему может поступать новая задача (множество увеличивается), после решения

задача выбывает из системы множест)v . Каждой вновь посту5- пившей в систему задаче присваивается определенный приоритет (возможно присвоение одинакового приоритета нескольким задачам). По мере поступления задач для каждого из возможных значений приоритета в системе формируется -очередь на обработку. При этом часть очередей может быть пустой, если в текущий момент в системе отсутствуют задачи с данными приоритетами.

Каждый из процессоров может об- рабатьшать любзто из задач. При этом процессору присваивается приоритет решаемой задачи (текущий приоритет) Кроме того, каждый из процессоров име§т свой, независящий от решаемых задач, постоянный приоритет (допустим,- для первого процессора.- наивысший, для п-го - наименьший).

Распределение программ по процессорам с помощью предлагаемого устройства осуществляется следующим образом. При постановке задач на очередь в устройство по одному из входов 7 на вход блока 1 приоритетного выбора запросов поступает запросное слово. При отработке поступившего запроса блок 1 устанавливает в единицу один из разрядов регистра 2 заполненных очередей. Разрядность регистра 2 равна максимальному числу возможных текущих приоритетов в системе. Если при снятии задачи с очереди очередь окажется пустой, то на вход 7 поступает запросное слово, при отработке которого блок 1 обнуляет соответствующий этой очереди разряд регистра 2. Таким образом, наличие непустых очередей задач в системе отражается единичным состоянием разрядов .регистра 2.

Если на вход 7 устройства одновременно поступает несколько запросов, то в блоке 1 первым обрабатьгоа- ется запрос процессора, имеющего более высокий постоянный приоритет.

С выхода регистра 2 код поступает на вход блока 3 определения старшей единицы, где преобразуется в код номера приоритета непустой очереди с наивысшим приоритетом. Этот код поступает на вход схемы 5 сравнения и на выход 8 устройства. На второй вход схемы 5 сравнения поступает код наименьшего текущего приоритета, вырабатьгеаемый блоком 4. На вход блока 4 с входа 10 устройства поступают коды текущего приоритета процессоров. Блок 4 пропускает на вход схемы 5 только код, со242948

ответствующий наименьшему текущему приоритету, и вы раба тывает на одном из выходов стробирующий сигнал. Если наименьший код текущего приоритета

5 поступает по входу lOj, то стробирующий сигнал поступает на вход элемента И 6j. Если наименьший код текущего приоритета окажется на нескольких входах 10, то стробирующий

10 сигнал поступает на вход того элемента И 6, выход которого соединен с входом процессора с наименьшими постоянными и текущим приоритетами. В случае, когда код на выходе бло)5 ка 2 окажется больше кода на выходе схемы 5, появляется сигнал логической 1, который поступает на входы элементов И 6- и разрешает прохождение -стробирующего сигнала с одного

20 из выходов блока 4 на выход 9 прерывания устройства. По этому сигналу процессор с наименьшим текущим приоритетом прекращает обработку текущей задачи и начинает обработку

25 новой задачи с более высоким приоритетом. Код очереди, где находится новая задача, поступает с выхода 8 устройства. При этом процессор производит постановку старой задачи

30 очередь и снимает с очереди новую задачу с выставлением соответствующих запросов на входе 7 устройства.

, Блок 1 приоритетного выбора за просов работает-следующим образом.

По одному из входов 17J блока поступает код запроса. Старший разряд кода приходит на вход элемента И-НЕ группы 16, а младшие разряды - на j-й информационный вход коммутатора 12. Выходной сигнал элемента И-.НЕ 16j устанавливает в единичное состояние соответствующий триггер 11j. Сигнал с прямого выхода триг гера llj поступает на j-й управляющий вход коммутатора 12 и разрешает прохождение младших разрядов кода запроса через коммутатор 12 на информационный вход дешифратора 15.

50 Этот же сигнал поступает на вход элемента ИЛИ-НЕ 13, выходной сигнал которого используется для стробиро- . свания дешифратора 15, для запрета нового запроса на элементы И-НЕ 16,

55 а также задерживается элементом 14 задержки на время, необходимое для отработки запроса, и сбрасьтает триггеры II в нулевое состояние.

40

При появлении стробирующего сит-нала на одном из в ыходов дешифратора 15 появляется сигнал. Сигнал на Четных выходах дешифратора используется для установки определенных разрядов регистра 2 заполненных очередей в единичное состояние, на нечетных выходах - в нулевое состояние.

При одновременном появлении за- проса на нескольких входах 17 блока на вход триггера 11 поступает сигнал только с выхода элемента И-НЕ 16j с меньшим J, т.е. отрабатывается запрос с большим приоритетом.

Блок 4 выделения наименьшего приоритета работает следующим образом.

Коды текущих приоритетов, среди которых необходимо выделить наименьший, поступают с входов 24 блока на входы соответствующих вычитающих счетчиков 9 и информационные входь коммутатора 20. По выходному сигналу элемента 21 задержки в счетчики 19 заносятся входные коды текущих приоритетов. Сигналы заема на выходах счетчиков 19 отсутствуют. На выходе элемента ИЛИ 22 устанавливается сигнал логического О , который разрешает формирование на выходах генератора 23 сдвинутых во времени импульсов. Сигнал на выходе элемента 21 задержки исчезает и счетчик 19j, в котором находится код наименьшего приоритета, первым достигает состоя- ния нуля. Тогда на его выходе вырабатывается сигнал заема, который поступает на соотв.етствующий управляющий вход коммутатора 20 и разрешает прохождение через коммутатор 20 на выход 26 блока кода наименьшего приоритета, сопровождая его импульсом на выходе 25j. Этот же сигнал через элемент ИЛИ 22 поступает на входы элемента 21 задержки и гене- ратора 23. Генерато1р 23 прекращает формирование выходных импульсов. Через некоторое время на выходе элемента 21 задержки снова появляется сигнал, и блок начинает работу сна- чала.

Формула изобретения

I. Устройство управления преры- ваниями, содержащее блок приоритетного выбора запросов, регистр запол- ненньпс очередей, выход которого

0

5

,|

(о ;

5

Ci

соединен с входом блока определения старшей единицы, выход которого соединен с выходом наиболее приоритетной непустой очереди устройства, j-й вход блока приоритетного выбора запросов (.,.n, где п - количество запросов) соединен с j-м входом запросного слова уст зойства, о т- - лич ающе е ся. тем, что, с целью упрощения устройства, оно содержит, блок выделения наименьшего приоритета, схему сравнения и группу п элементов И, выходы которых подключены к выходам прерывания устройства соответственно, первые входы п элементов И группы соединены с выходом схемы сравнения, первый вход которой соединен с выходом блока определения старшей единицы, а второй вход- с первым выходом блока выделения наименьшего приоритета, i-й выход которого (...n+l) подключен к второму входу j-TO элемента И группы, j-й вход блока выделения наименьшего приоритета подключен к j-му входу текущего приоритета устройстваj первая и вторая группы выходов блока приоритетного выбора запросов подключены соответственно к входам установки в О и в 1 k-ro разр5эда .,.rn, где m - количество градаций приоритета регистра заполненных очередей.

2.Устройство по п. Ij отличающееся тем, что блок выделения наименьшего приоритета содержит п счетчиков, коммутатор,-элемент задержки, элемент ИЛИ, генератор тактовых импульсов, причем j-й выход .генератора тактовых импульсов подключен,

к вычитающему входу j-ro счетчика, информационный вход которого соединен с 1-м входом блока вьщеления наименьшего приоритета и с j-м информационным входом коммутатора, j-й управляющий вход которого соединен с выходом заема j-ro счетчика, с j-м входом элемента ИЛИ и подключен к j-му вьшоду блока вьщеления наи- меньш:его приоритета, первый выход которого соединен с выходом коммутатора, выход элемента ИЛИ подключен к входу пуска генератора тактовых импульсов, а через элемент задержки - к входам записи п счетчиков.

3.Устройство по п. 1, отличающееся тем, что блок прио7

ритетного выбора запросов содержит группу п триггеров, коммутатор, элемент ИЛИ-НР, элемент задержки, дешифратор и группу п элементов И-НЕ, причем первый вход J-ro элемента И-НЕ группы соединен с входом старшего разряда-j-ro входа блока, второй вход-с входом элемента задержки и с выходом элемента ИЛИ-НЕ, j-й вход которого соединен с прямым выходом j-ro триггера группы и с J-M управляющим входом коммутатора, j-й информационный вход которого соединен с входами младших разрядов j-ro входа блока соответственно, выход коммутатора

429488

подключен к информационному входу дешифратора, стробирующий вход которого соединен с выходом элемента ИЛИ-НЕ, вьрсод элемента задержки сое- 5 динен с входом установки в О триггеров группы, вход установки в 1 которого соединен с выходом J-ro элемента И-НЕ группы, выход р-го (...n-l) элемента И-НЕ группы

0 соединен с (р+2)-ми входами всех последукщих элементов И-НЕ группы, четные и нечетные выходы дешифратора подключены соответственно к первой и второй группам выходом

5 блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1780087A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для обработки прерываний | 1986 |

|

SU1606975A1 |

| Устройство для сопряжения процессоров в вычислительной системе | 1985 |

|

SU1332327A1 |

| Устройство для управления обращением в оперативную память | 1976 |

|

SU641454A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

Изобретение относится к вычислительной технике и может быть применено в многопрограммных, многопроцессорных системах. Цель изобретения - упрощение устройства. Это достигается за счет введения в устройство блока выделения наименьшего приоритета, элемента сравнения и группы элементов И с соответствующими функциональными связями между ними и известными блоками устройства. Устройство обслуживает систему из п источников запросов (процессоров), в которой одновременно может обрабатываться произвольное множество задач (программ). 2 з.п. ф-лы, 3 ил. 1C 4ib 1C СО 4а 00

фиг.1

.L.- -

фиг. I

-I

Составитель Л. Сергейчук Редактор И. Николайчук Сехред О.Гортвай Корректор А, Зимокосов

Заказ 3706/48Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

.3

| Патент США № 3421150, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многопроцессорная вычислительная система | 1977 |

|

SU670937A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1982-04-09—Подача