( УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ОДНОКРАТНЫХ СИГНАЛОВ

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для исследования однократных сигналов.

Известно устройство для регистрации однократных сигналов, содержащее усилитель, аналого-цифровой преобразователь (АЦП), коммутатор, блок памяти, индикатор и блок управления С 1 3«

Недостатком этого устройства является большая емкость памяти, необходимая для регистрации сигнала с высокой точностью.

Наиболее близким к изобретению по технической сущности является устройство для регистрации однократных си|- налов, содержащее усилитель АЦП, две схемм сравнения, индикатор, генератор импульсов, два блока памяти, пять счетчиков, элемент ИЛИ, блок выделения границ сообщения, формирователь кода, коммутатор и блок управления 2.

Недостатком известного устройства является низкая точность регистрации, вызванная увеличением интервала дискретизации.

Цель изобретения - повышение точности регистрации однократных си|- налов.

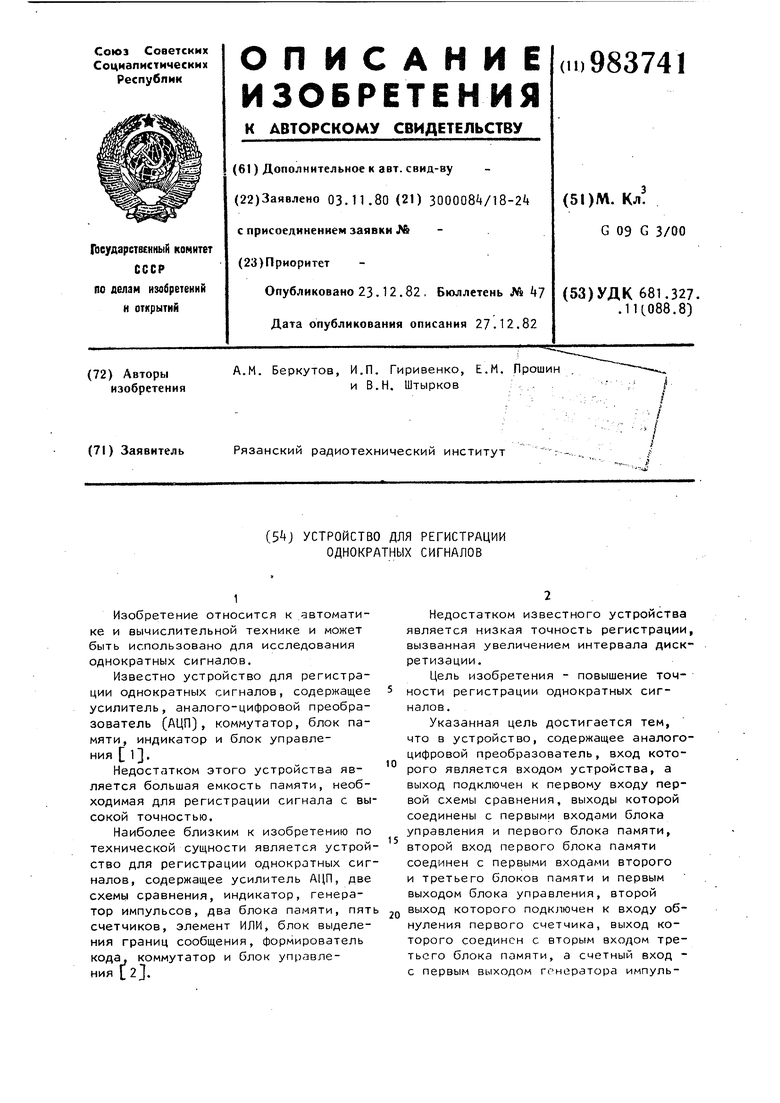

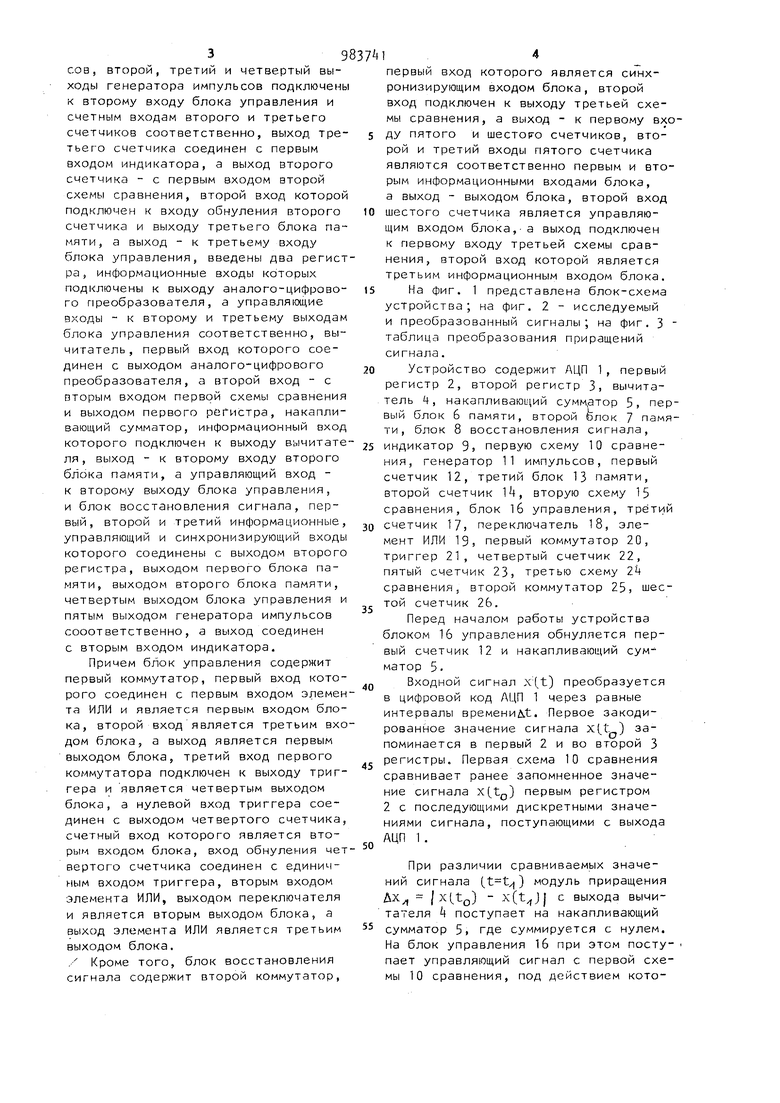

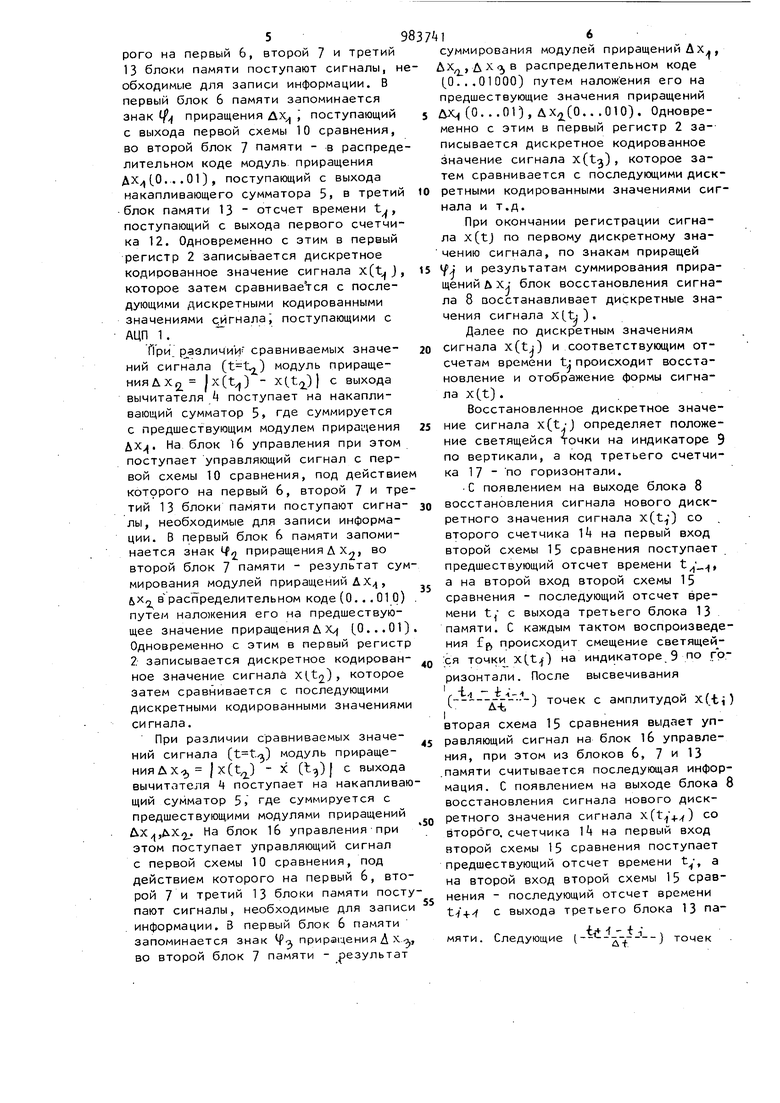

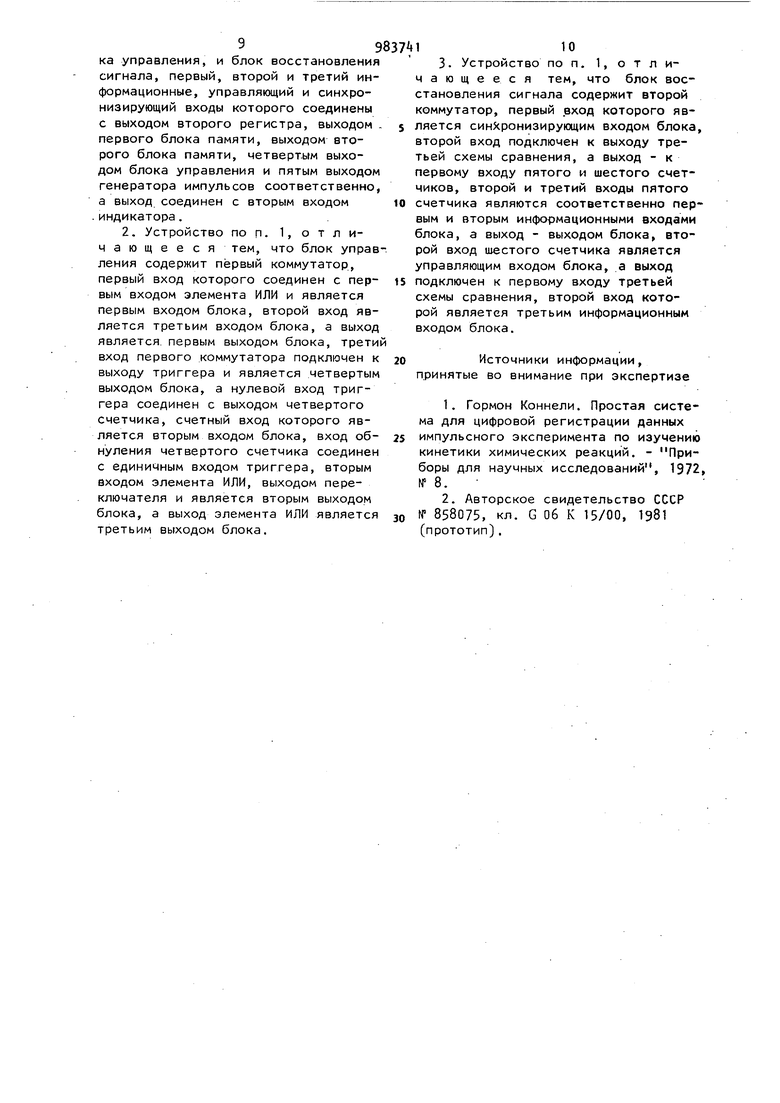

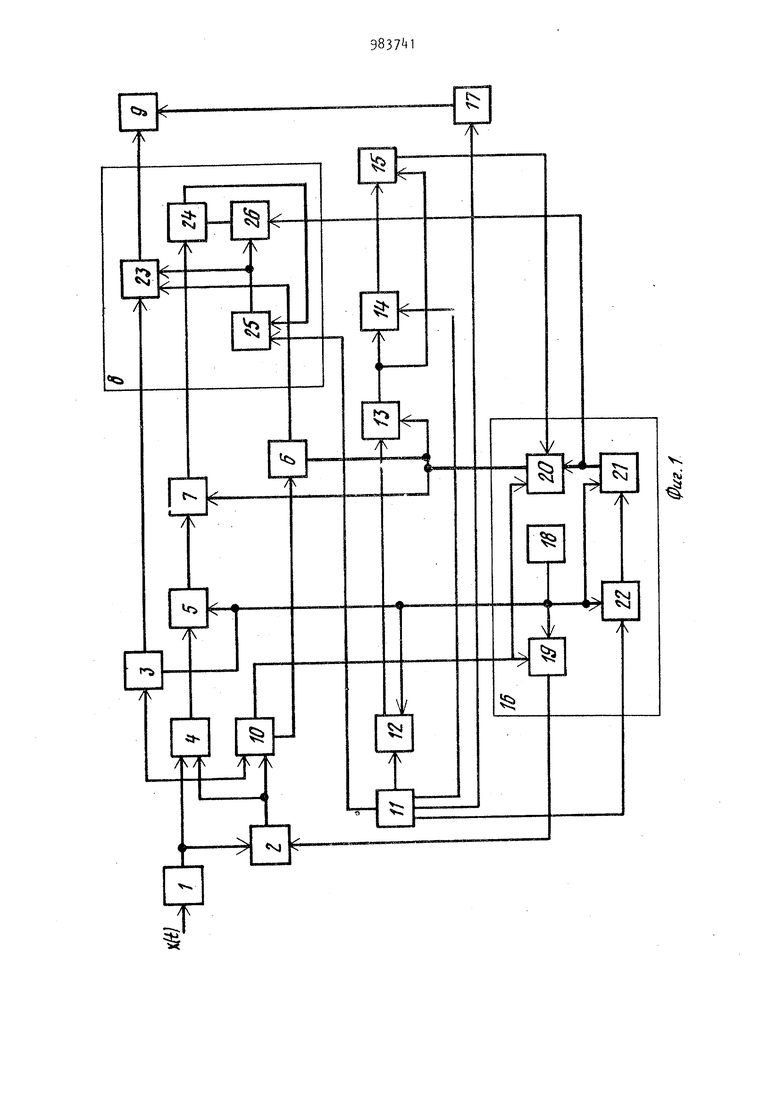

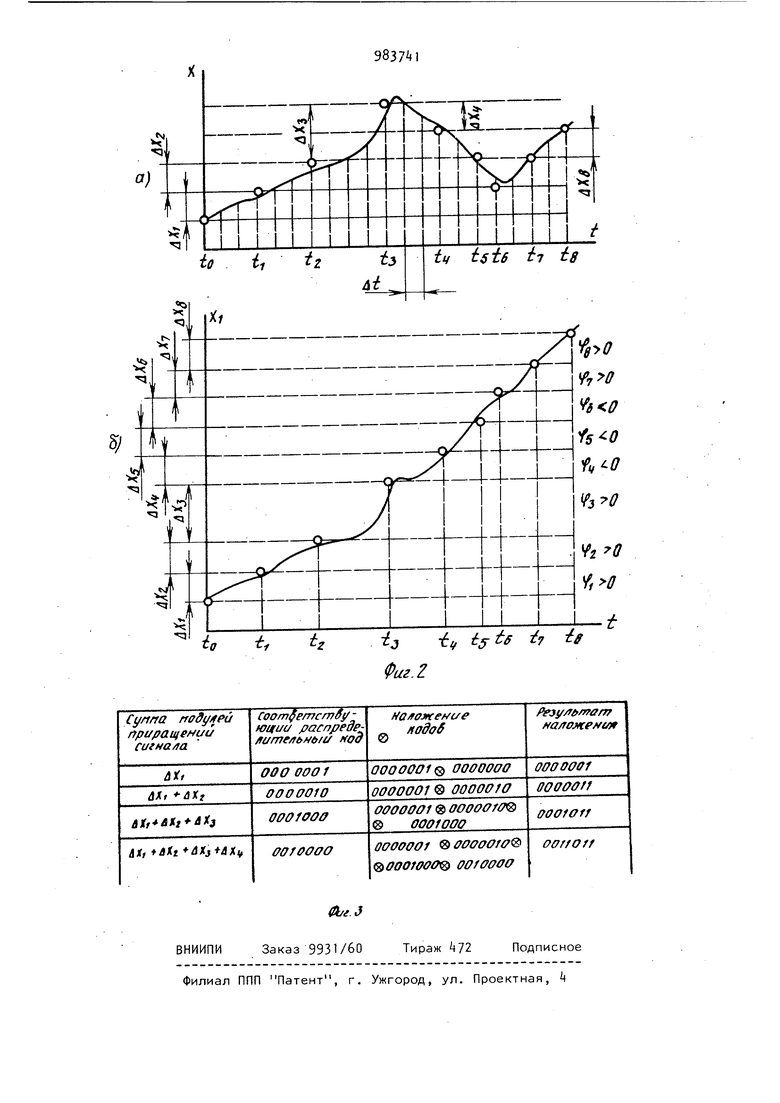

Указанная цель достигается тем, что в устройство, содержащее аналогоцифровой преобразователь, вход которого является входом устройства, а выход подключен к первому входу первой схемы сравнения, выходы которой соединены с первыми входами блока управления и первого блока памяти, второй вход первого блока памяти соединен с первыми входами второго и третьего блоков памяти и первым выходом блока управления, второй выход которого подключен к входу обнуления первого счетчика, выход которого соединен с вторым входом третьего блока памяти, а счетный вход с первым выходом генератора импуль3сов, второй, третий и четвертый выходы генератора импульсов подключен к второму входу блока управления и счетным входам второго и третьего счетчиков соответственно, выход тре тьего счетчика соединен с первым входом индикатора, а выход второго счетчика - с первым входом второй схемы сравнения, второй вход которо подключен к входу обнуления второго счетчика и выходу третьего блока па мяти, а выход - к третьему входу блока управления, введены два регис ра, информационные входы которых подключены к выходу аналого-цифрово го преобразователя, а управляющие входы к второму и третьему выходам блока управления соответственно, вычитатель, первый вход которого соединен с выходом аналого-цифрового преобразователя, а второй вход - с вторым входом первой схемы сравнения и выходом первого регистра, накапливающий сумматор, информационный вход которого подключен к выходу вычитате ля, выход - к второму входу второго блока памяти, а управляющий вход к второму выходу блока управления, и блок восстановления сигнала, первый, второй и третий информационные управляющий и синхронизирующий входы которого соединены с выходом второго регистра, выходом первого блока памяти, выходом второго блока памяти, четвертым выходом блока управления и пятым выходом генератора импульсов сооответственно, а выход соединен с вторым входом индикатора. Причем блок управления содержит первый коммутатор, первый вход которого соединен с первым входом элемен та ИЛИ и является первым входом блока, второй вход является третьим вхо дом блока, а выход является первым выходом блока, третий вход первого коммутатора подключен к выходу три1- гера и является четвертым выходом блока, а нулевой вход триггера соединен с выходом четвертого счетчика счетный вход которого является вторым входом блока, вход обнуления чет вертого счетчика соединен с единичным входом триггера, вторым входом элемента ИЛИ, выходом переключателя и является вторым выходом блока, а выход элемента ИЛИ является третьим выходом блока. / Кроме того, блок восстановления сигнала содержит второй коммутатор. 1.4 первый вход которого является синхронизирующим входом блока, второй вход подключен к выходу третьей схемы сравнения, а выход - к первому входу пятого и шестор-о счетчиков, второй и третий входы пятого счетчика являются соответственно первым и вторым информационными входами блока, а выход - выходом блока, второй вход шестого счетчика является управляющим входом блока,-а выход подключен к первому входу третьей схемы сравнения, второй вход которой является третьим информационным входом блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - исследуемый и преобразованный сигналы; на фиг. 3 таблица преобразования приращений сигнала. Устройство содержит АЦП 1, первый регистр 2, второй регистр 3, вычитатель л, накапливаюи(ий сумматор 5, первый блок 6 памяти, второй блок 7 памяти, блок 8 восстановления сигнала, индикатор 9) первую схему 10 сравнения, генератор 11 импульсов, первый счетчик 12, третий блок 13 памяти, второй счетчик 1i, вторую схему 15 сравнения, блок 1б управления, третий счетчик 17, переключатель 18, элемент ИЛИ 19, первый коммутатор 20, триггер 21, четвертый счетчик 22, пятый счетчик 23, третью схему 24 сравнения, второй коммутатор 25, шестой счетчик 26. Перед началом работы устройства блоком 16 управления обнуляется первый счетчик 12 и накапливающий сумматор 5. Входной сигнал ) преобразуется в цифровой код АЦП 1 через равные интервалы вpeмeнид.t. Первое закодированное значение сигнала ) запоминается в первый 2 и во второй 3 регистры. Первая схема 10 сравнения сравнивает ранее запомненное значение сигнала ,) первым регистром 2с последующими дискретными значениями сигнала, поступающими с выхода АЦП 1 . При различии сравниваемых значений сигнала () модуль приращения Дх |x(to) - x( с выхода вычитателя k поступает на накапливающий сумматор 5 где суммируется с нулем. На блок управления 16 при этом поступает управляющий сигнал с первой схемы 10 сравнения, под действием кото5рого на первый 6, второй 7 и третий 13 блоки памяти поступают сигналы, н обходимые для записи информации. В первый блок 6 памяти запоминается знак tf приращения дх j поступающий с выхода первой схемы 10 сравнения, во второй блок 7 памяти - в распреде лительном коде модуль приращения Дх(0...01), поступающий с выхода накапливающего сумматора 5, в третий блок памяти 13 отсчет времени t,, поступающий с выхода первого счетчика 12. Одновременно с этим в первый регистр 2 записывается дискретное кодированное значение сигнала x(, которое затем сравнивается с последующими дискретными кодированными значениями сигналаi поступающими с АЦП 1 . При различии- сравниваемых значений сигнала () модуль приращения Л Х2 Ix(t) - x(t)| с выхода вычитателя 4 поступает на накапливающий сумматор 5 где суммируется с предшествующим модулем приращения дх. На блок 1б управления при этом поступает управляющий сигнал с первой схемы 10 сравнения, под действие котррого на первый 6, второй 7 и тре тий 13 блоки памяти поступают сигналы, необходимые для записи информации. В первый блок 6 памяти запоминается знак приращенияД во второй блок 7 памяти - результат сум мирования модулей приращений Дх , ЬХ враспределитель ном коде (0.. . 01 0) путем наложения его на предшествующее значение приращения Д x/j 0...01) Одновременно с этим в первый регистр 2 записывается дискретное кодированное значение сигнала x(,t2), которое затем сравнивается с последующими дискретными кодированными значениями сигнала. При различии сравниваемых значений сигнала (t) модуль приращенияДх |x(t) - X (t) I с выхода вычитателя 4 поступает на накапливаю щий сумматор 5 где суммируется с предшествующими модулями приращений Дх,Х. На блок 16 управления при этом поступает управляющий сигнал с первой схемы 10 сравнения, под действием которого на первый 6, второй 7 и третий 13 блоки памяти посту пают сигналы, необходимые для записи информации. В первый блок 6 памяти запоминается знак Ч-а прирагдения Д х, во второй блок 7 памяти - результат 16 суммирования модулей приращений Дх., Лх, распределительном коде (0.., 01000) путем наложения его на предшествующие значения приращений ЛХ (0. . .01) , дх/(0.. .010). Одновременно с этим в первый регистр 2 записывается дискретное кодированное значение сигнала x(t2), которое затем сравнивается с последующими дискретными кодированными значениями сигнала и т.д. При окончании регистрации сигнала x(tj по первому дискретному значению сигнала, по знакам приращей fj и результатам суммирования приращенийUх; блок восстановления сигнала 8 восстанавливает дискретные значения сигнала x(tj). Далее по дискретным значениям сигнала x(ti) и соответствующим отсчетам времени t:происходит восстановление и отображение формы сигнала x(t) . Восстановленное дискретное значение сигнала x(t-J определяет положение светящейся точки на индикаторе 9 по вертикали, а код третьего счетчика 1 7 - по горизонтали. С появлением на выходе блока 8 восстановления сигнала нового дискретного Значения сигнала x() со второго счетчика Tt на первый вход второй схемы 15 сравнения поступает предшествующий отсчет времени , а на второй вход второй схемы 15 сравнения - последующий отсчет времени с выхода третьего блока 13 памяти. С каждым тактом воспроизведения f р, происходит смещение светящей:ся точки x(t) на индикаторе 9 по грризонтали. После высвечивания ( .. точек с амплитудой x(ti ) вторая схема 15 сравнения выдает управляющий сигнал на блок 1б управле р 3 блоков 6, 7 и 13 памяти считывается последующая инфор„ация. С появлением на выходе блока 8 восстановления сигнала нового дискретного значения сигнала xCty4-/f) со второго, счетчика 4 на первый вход второй схемы 15 сравнения поступает предшествующий отсчет времени , а на второй вход второй схемы 15 сравнения - последующий отсчет времени ty+ с выхода третьего блока 13 памяти. Следующие () точек 79 высвечиваются с амплитудой , ) /f t и т.д. Восстановление дискретных значений сигнала происходит следующим образом. При окончании регистрации шее той счетчик 26 обнуляется. Первое дискретное значение сигнала x(,) с выхода второго регистра 3 устанавливается в пятый счетчик 23. Результат суммирования модулей приращений с выхода второго блока 7 памяти поступает на один из входов третьей схемы 2 сравнения. Если код шестого счетчика 26 меньше, чем результат суммирования модулей приращений, то третья схема 2А сравнения пропускает импульсы частотой , (k 1J с выхода генератора 11 импульсов через второй коммутатор 25 до тех пор, пока коды, сравниваемые третьей схемой 2Ц сравнения, не будут равны. Шестой счетчик 26 работает все время на сум мирование, а пятый счетчик 23 либо на суммирование, либо на вычитание в зависимости от считанного знака приращения f;. Таким образом на выходе пятого счетчика 23 получаем вос становленные дискретные значения сиг нала x(tj) . Блок 16 управления управляет рабо той устройства. Перед началом регистрации переключателем 18 обнуляется накапливаюа1ий сумматор 5 первый 12 и четвертый 22 счетчики, во второй регистр 3 устанавливается первое дискретное значение сигнала xftp), триггер 21 устанавливается в режим, соответствующий записи информации в блоки 6, 7 и 13 памяти. При различии кодов, сравниваемых первой схемой 10 сравнения, вырабатывается управляющий сигнал, который во-первых, проходит через элемент ИЛИ 19 и устанавливает в первый регистр 2 текущее кодированное значение сигнала x(t), во-вторых, проходит через коммутатор 20 на блоки памяти 6, 7 и 13, при этом в них записывается соответствующая информация. Четвертый счетчик 22 считает тактовые импульсы. При его перёполнениитриггер 21 устанавливается в состояние, соответствующее считыванию информации из блоков 6, 7 и 13 памяти. Затем обнуляется шестой счетчик 26. При равенстве кодов, поступающих на вторую схему 15 сравнения, выраЬатывается управляющий сигнал, который проходит через коммутатор 20 на блоки 6, 7 и 13 памяти при этом из них считывается соответствующая информация. Устройство повышает точность регистрации за счет более эффективного использования емкости блоков памяти. Формула изобретения 1. Устройство для регистрации однократных сигналов, содержащее аналого-цифровой преобразователь, вход которого является входом устройства, а выход подкпючен к первому входу первой схемы сравнения, выходы которой соединены с первыми входами блока управления и первого блока памяти, второй вход первого блока памяти соединен с первыми входами второго и третьего блоков памяти и первым выходом блока управления, второй выход которого подключен к входу обнуления первого счетчика, выход которого соединен с вторым входом третьего блока памяти, а счетный вход с первым выходом генератора импульсов, второй, третий и четвертый выходы генератора импульсов подключены к второму входу блока управления и счетным входам второго и третьего счетчиков соответственно, выход третьего счетчика соединен-с первым входом индикатора, а выход второго счетчика - с первым входом второй схемы сравнения, второй вход которой подключен к входу обнуления второго счетчика и выходу третьего блока памяти, а выход - к третьему входу блока управления, отличающеес я тем, что, с целью повышения точности устройства, оно содержит два регистра, информационные входы которых подключены к выходу аналого-цифрового преобразователя, а управляющие входы - к второму и третьему выходам блока управления соответственно, вычитатель, первый вход которого соединен с выходом аналогоцифрового преобразователя, а второй вход - с вторым входом первой схемы сравнения и выходом первого регистра, накапливающий сумматор, информационный вход которого подключен к выходу вычитателя, выход - к второму входу второго блока памяти, а управляющий вход - к второму выходу бло99ка управления, и блок восстановления сигнала, первый, второй и третий информационные, управляющий и синхронизирующий входы которого соединены с выходом второго регистра, выходом . первого блока памяти, выходом второго блока памяти, четвертым выходом блока управления и пятым выходом генератора импульсов соответственно, а выход соединен с вторым входом .индикатора. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит первый коммутатор, первый вход которого соединен с первым входом элемента ИЛИ и является первым входом блока, второй вход является третьим входом блока, а выход является, первым выходом блока, третий вход первого коммутатора подключен к выходу триггера и является четвертым выходом блока, а нулевой вход триггера соединен с выходом четвертого счетчика, счетный вход которого является вторым входом блока, вход обнуления четвертого счетчика соединен с единичным входом триггера, вторым входом элемента ИЛИ, выходом переключателя и является вторым выходом блока, а выход элемента ИЛИ является третьим выходом блока. 1 . 1, о т л и3. Устройство по п, что блок восчающееся тем, становления сигнала содержит второй коммутатор, первый вход которого является синхронизирующим входом блока, второй вход подключен к выходу третьей схемы сравнения, а выход - к первому входу пятого и шестого счетчиков, второй и третий входы пятого счетчика являются соответственно первым и вторым информационными входами блока, а выход - выходом блока, второй вход шестого счетчика является управляющим входом блока, а выход подключен к первому входу третьей схемы сравнения, второй вход которой является третьим информационным входом блока. Источники информации, принятые во внимание при экспертизе 1.Гормон Коннели. Простая система для цифровой регистрации данных импульсного эксперимента по изучению кинетики химических реакций. - Приборы для научных исследований, 1972, № 8. 2.Авторское свидетельство СССР № 858075, кл. G Об К 15/00, 1981 (прототип).

ЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для формирования плана проходимости местности перед транспортным средством | 1988 |

|

SU1562933A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1539825A1 |

| Способ регистрации формы импульсных сигналов и устройство регистрации формы импульсных сигналов | 1988 |

|

SU1575133A1 |

| Линейный интерполятор | 1988 |

|

SU1538166A2 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983742A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1980 |

|

SU911504A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

;

м

/Ь

«

/ V

/

fy

/

1г

/

г

Ж

C4J

/ ч

/

I

/

4 «4J

io i,

ti/ is is /7 is

Ь

Авторы

Даты

1982-12-23—Публикация

1980-11-03—Подача