схемы сравнения и первым входом пятого двухвходового многоразрядного сумматора, выход которого соединен с вторым входом первой схемы сравнения, а второй вход - с вторым входом четвертой схемы сравнения и входом знака числа устройства, вход абсолютной величины коэффициента которого соединен с установочными входами второго и

четвертого реверсивных счетчиков, третьим входом четвертой схемы сравнения и первым входом шестого двухвходового многоразрядного сумматора, выход которого соединен с вторым входом второй схемы сравнения, а второй вход - с третьим входом третьей схемы сравнения и с входом абсолютной величины числа устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель | 1984 |

|

SU1171784A1 |

| Вычислительное устройство | 1985 |

|

SU1259253A1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2829014C1 |

| Счетное устройство | 1980 |

|

SU930685A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1977 |

|

SU742985A1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2840388C1 |

| Устройство для вычитания частоты из опорной частоты | 1983 |

|

SU1185353A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2010 |

|

RU2444781C1 |

| Устройство для дистанционного измерения потребления электроэнергии | 1990 |

|

SU1718125A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА НА ПОСТОЯННЫЙ КОЭФФИЦИЕНТ, содержащее генератор тактовых импульсов, триггер, два элемента И, два управляемых делителя частоты, реверсивный счетчик и схему сравнения, причем выход реверсивного счетчика соединен с первым входом схемы сравнения, а выход триггера - с первыми входами первого и второго элементов И, отличающееся тем, что, с целью повышения быстродействия, в него введены три элемента И, делитель частоты, шесть двухвходовых многоразрядных сумматоров, два управляемых делителя частоты, восемь коммутаторов, семь реверсивных счетчиков, три схемы сравнения и четырехвходовой многоразрядный сумматор, причем выход генератора тактовых импульсов соединен с первыми управляющими входами делителя частоты и всех управляемых делителей частоты, вторые управляющие входы которых соединены с выходами «Сравнение соответствующих схем сравнения и с соответствующими входами третьего элемента И, выход которого соединен с входом установки нуля триггера и с вторым управляющим входом делителя частоты, выход которого соединен с информационными входами первого, второго, третьего и четвертого коммутаторов и с входом установки единицы триггера, выход которого соединен с первыми входами четвертого и пятого элементов И, информационные входы всех управляемых делителей частоты соединены с выходами первого, второго, третьего и четвертого двухвходовых многоразрядных сумматоров соответственно, первые входы которых соединены с выходами первого, второго, третьего и четвертого реверсивных счетчиков соответственно, суммирующие и вычитающие входы которых соединены соответственно с первыми и вторыми выходами первого, второго, третьего и четвертого коммутаторов, выходы всех управляемых делителей частоты соединены с вторыми входами первого, второго, четвертого и пятого элементов И соответственно, выходы которых соединены с информационными входами пятого, щестого, седьi мого и восьмого коммутаторов соответственно, первые и вторые выходы пятого и шес(Л того коммутаторов соединены с суммирующими и вычитающими входами пятого и шестого реверсивных счетчиков соответственно, суммирующие и вычитающие входы седьмого и восьмого реверсивных счетчиков соединены соответственно с вторыми и первыми выходами седьмого и восьмого коммутаторов, выходы «Больше всех схем сравнения соединены соответственно с вторыми входаО5 ми первого, второго, третьего и четвер00 того двухвходовых многоразрядных суммасо к торов и с первыми управляющими входами соответствующих пар коммутаторов, вторые управляющие входы которых соеди00 нены с выходами «Меньше соответствующих схем сравнения, первые входы второй, третьей и четвертой схем сравнения соединены с выходами второго, третьего и четвертого реверсивных счетчиков, выходы пятого, щестого седьмого и восьмого реверсивных счетчиков соединены с входами четырехвходового многоразрядного сумматора, выход которого соединен с выходом устройства, вход знака коэффициента которого соединен с установочными входами первого и третьего реверсивных счетчиков, вторым входом третьей

t

Изобретение относится к цифровым (дискретным) вычислительным машинам, в которых по меньшей мере часть вычислений осуществляется с помощью электрических устройств, к устройствам для обработки данных с воздействием на порядок их расположения или на содержание обрабатываемых данных, в частности - для умножения, и может быть использовано в различных устройствах цифровых (дискретных) вычислительных мащин.

Целью изобретения является повышение быстродействия устройства.

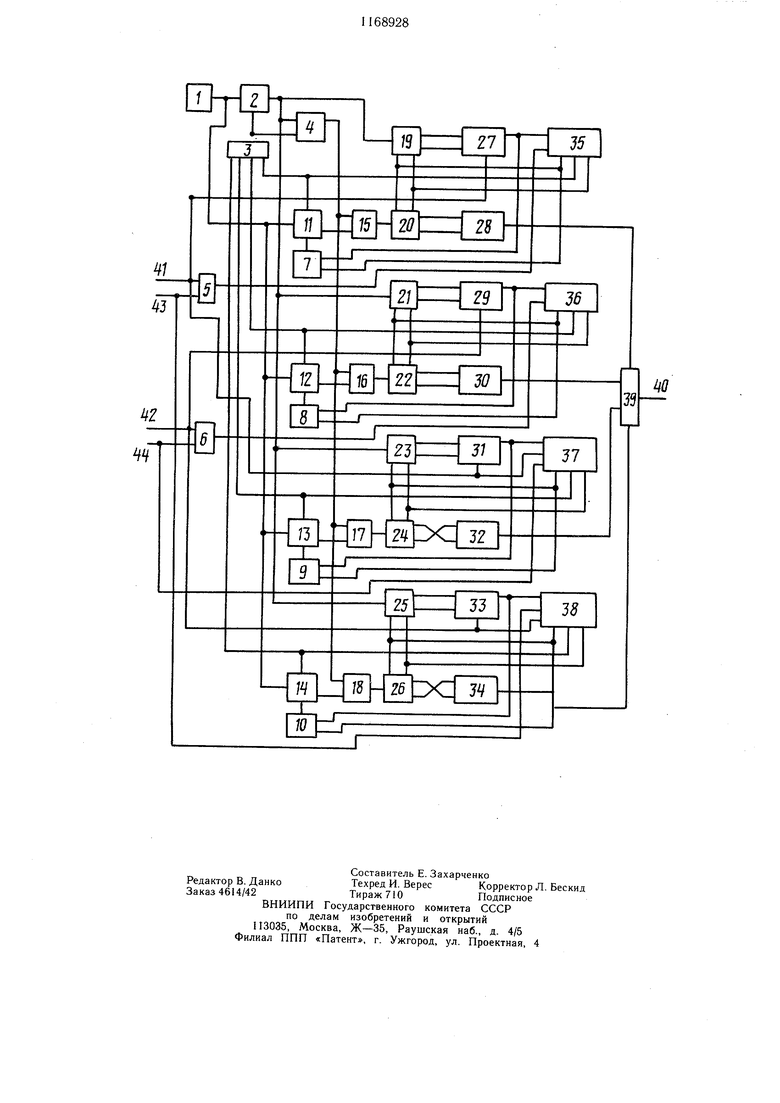

На чертеже представлена структурная схема устройства для умножения числа на постоянный коэффициент.

Устройство для умножения числа на постоянный коэффициент содержит генератор 1 тактовых импульсов 1, делитель 2 частоты, элемент И 3, триггер 4, двухвходовые многоразрядные сумматоры 5-10, управляемые делители 11 - 14 частоты, элементы И 15-18, коммутаторы 19-26, реверсивные счетчики 27-34, схемы 35-38 сравнения, четырехвходовой многоразрядный сумм.атор 39, выход 40 устройства, входы знака 41 и абсолютной величины коэффициента устройства 42 и входы знака 43 и абсолютной величины числа устройства 44.

Устройство для умножения числа на постоянный коэффициент работает следующим образом.

Число и постоянный коэффициент представлены в дoпoлнJ тeльнoм коде. Их можно записать как , X и Вд В, В, где X и В - знаки соответственно числа и коэффициента, а X тл В - абсолютные величины при . 0 или дополнения абсолютных величин при .Х 1 и В.,

Для простоты рассмотрим работу умножителя на примере постоянного коэффициента Вл 2 и числа 3. При этом X Q, Х 3 и В 0, S 2. Пусть в итаодном состоянии на входы 41-44 поданы нулевые коды, все реверсивные счетчики 27-34 и триггер 4 сброшены в нуль. Во всех схемах 35-38 сравнения по этой причине вырабатываются сигналы «Сравнения, которыми сбрасываются управляемые делители 11 -14 частоты и -через элемент И 3 сбрасывается делитель 2 частоты. После этого на вход 41 поступает знак S 0, который поступает на установочные входы реверсивных счетчиков 27 и 31, на схему 37 сравнения и на первый вход сумматора 5. Знак Х 0 с входа 43 поступает на схему 38 сравнения и на второй вход сумматора 6, с выхода которого результат 00 поступает на схему 35 сравнения.

Абсолютная величина В 2 с входа 42 поступает на установочные входы реверсивных счетчиков 29 и 33, на схему 38 сравнения и первый вход сумматора 6. Абсолютная величина А 3 с входа 44 поступает на схему 37 сравнения и второй вход сумматора 6, с выхода которого результат поступает на схему 36 сравнения. После этого в схеме 35 сравнения вырабатывается сигнал «Сравнение, который сбрасывает управляемый делитель 11, а также поступает на один из входов элемента И 3, коммутаторы 19 и 20 при этом оказываются закрытыми. Код 00000 поступает с выхода реверсивного счетчика 28 на один из входов сумматора 39. В схеме 36 сравнения вырабатывается сигнал «Больше, который открывает коммутаторы 21 и 22 так, что счетные импульсы будут поступать на суммирующие входы реверсивных счетчиков 29 и

30,а также поступает в качестве кода 00001 на вход сумматора 8, на другой вход которого поступает код 000010 с выхода реверсивного счетчика 29. Код 00001+00010 00011 с выхода сумматора 8 поступает на управляющий вход управляемого делителя 12 частоты.

В схеме 37 сравнения вырабатывается сигнал «Больше, который открывает коммутаторы 23 и 24, причем счетные импульсы с выхода коммутатора 23 будут поступать на суммирующий вход реверсивного счетчика

31,а с выхода коммутатора 24 - на вычитающий вход реверсивного счетчика 32, чем обеспечивается образование дополнения в

реверсивном счетчике 32. Сигнал «Больше со схемы 37 сравнения поступает в качестве кода 00001 на вход сумматора 9, на другой вход которого поступает код 00000 с выхода реверсивного счетчика 31. Код 00001 + +00000 00001 поступит с выхода сумматора 9 на управляющий вход управляемого делителя 13 частоты. В схеме 38 сравнения вырабатывается сигнал «Сравнение, который сбрасывает управляемый делитель 14 частоты и поступает на один из входов элемента И 3, коммутаторы 25 и 26 оказываются закрытыми. После этого в устройстве начинается переходной процесс, который протекает следующим образом. После подсчета первого импульса в реверсивном счетчике 29 будет код 00010+0001 00011, в реверсивном счетчике 30 - код 0000 + + 00011 00011, в реверсивном счетчике 31 - код 00000 + 00001 00001, а в реверсивном счетчике 32 в результате вычитания одного импульса будет дополнение 1, т.е. 100000-00001 11111.

На управляющем входе делителя 12 частоты с выхода сумматора 8 установится код 00011+00001 00100, а на управляющем входе делителя 13 частоты с выхода сумматора 9 - код 00001+00001 00010. После подсчета второго импульса в реверсивном счетчике 29 установится код 00100, а в реверсивном счетчике 30 будет храниться код 00011+00100 00111. После подсчета второго импульса в реверсивном счетчике 31 установится код 00001 + 00001 00010, а в реверсивном счетчике 32 в результате вычитания будет храниться код 11111-00010 11101. На управляющем входе делителя 12 частоты с выхода сумматора 8 установится код 00100 + 00001 00101, а на управляющем входе делителя 13 частоты с выхода сумматора 9 - код 00010-f 00001 00011. Поеле подсчета третьего импульса в реверсивном счетчике 29 установится код 00101, а в реверсивном счетчике 30 будет храниться код 00111+00101 01100. При этом в схеме 36 сравнения вырабатывается сигнал «Сравнение, который сбросит управляемый делитель 12 частоты, поступит на один из входов элемента И 3, а также закроет коммутаторы 21 и 22. Код 01100 с выхода реверсивного счетчика 30 поступит на вход сумматора 39. После подсчета третьего импульса в реверсивном счетчике 31 установится код 00010 + 00001 00011, а в реверсивном счетчике 32 в результате вычитания будет храниться код 11101-00011 11010. При этом в схеме 37 сравнения вырабатывается сигнал «Сравнение, который сбросит

управляемый делитель 13 частоты и через элемент И 3 делитель 2 частоты и триггер 4. Переходной процесс завершится суммированием на сумматоре 39 четырех кодов: 00000 + 01100 + 11010+00000 00110, т.е. 5 +6 2x3.

Если теперь число X получит положительное приращение, то рассмотренные процессы повторятся для любых чисел, соответствующих выбранной разрядной сетке.

0 При этом отработка приращения переменной начнется с тех кодов, которые храняться в реверсивных счетчиках. Если же число получит отрицательное приращение, то процесс умножения коэффициента на приращение числа будет происходить несколько иначе.

Продолжим рассмотренный пример для случая, когда Х . В результате достигнутого равновесия в реверсивном счетчике 29 хранится код 00101, в реверсивном счетчике 30 - код 01100, в реверсивном

0 счетчике 31 - код 00011, в реверсивном счетчике 32 - код 11010, в остальных реверсивных счетчиках - коды 00000. После приходас входа 44 вместо Х 2 с выхода сумматора 6 на схему 36 сравнения поступит код 00010 + 00010 00100, а на схему 37 срав нения - код 00010.

В результате схемы 36 и 37 сравнения вырабатывают сигналы «Меньще, откроют коммутаторы 21-23 так, что счетные импульсы будут поступать на вычитающие входы реверсивных счетчиков, а с коммутатора 24 - на суммирующий вход реверсивного счетчика 32, причем на вторые входы сумматоров 8 и 9 поступают коды 00000. Поэтому код 00101 с выхода реверсивного счетчика 29 пройдет через сумматор 8 на управляю5 щии вход делителя 12 частоты без изменения. Код 00011 с выхода реверсивного счетчика 31 поступит без изменения на управляющий вход делителя 13 частоты через сумматор 9. В результате вычитания одного импульса из реверсивного Счетчика 29 в нем установится код 00101-00001 00100, а в реверсивном счетчике 30 будет храниться код 01100-00101 00111. В результате вычитания одного импульса из реверсивного счетчика 31 в нем установится код 00011 -

5 00001 00010, а в реверсивном счетчике 32код 11010 + 00011 11101. После этого схемы 36 и 37 сравнения вырабатывают сигналы «Сравнение, которые произведут указанные сбросы делителей частоты и триггера. Переходной процесс заверщится суммированием на сумматоре 39 кодов 00000 + + 000111 + 11101+00000 00100, т.е. +4 2x2.

| Устройство для умножения числаНА КОэффициЕНТ | 1976 |

|

SU807277A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1976 |

|

SU590735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-22—Подача