1

Изобретение относится к вычислительной технике и может найти при1мепение в специализированных вычислительных устройствах обработки измерительной информации, системах управлени|Я и т. д.

Известно устройство 1, содержащее генератор Иiмпyльcoв, делитель частоты, счетчик, триггер, вентиль, дешифратор и .блок преобразования кодов. Известное устройство выполняет оиерацию Л вых Л Л2: jVs над величинами ;V, и NZ, заданными в кодовой форме.

В известном устройстве требуется преобразовать прямой код сомножителя N в дополнительный для повышения быстродействия счета число-импульсного эквивалента сомножителя NI. Это понижает его быстродействие из-за затрат времени на преобразование кодов.

Известно устройство 2, содержащее генератор импульсов, первый и второй делители частоты, счетчик, первый элемент И, причем выход генератора импульсов соединен с первым входом первого элемента И, выход которого связан с первыми входами первого и второго делителей частоты, вторые входы этих делителей - соответственно с первой и второй входными иифор1мационными шинами, а выход первого делителя частоты подключен к первому входу счетчика.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повыщенне быстродействия.

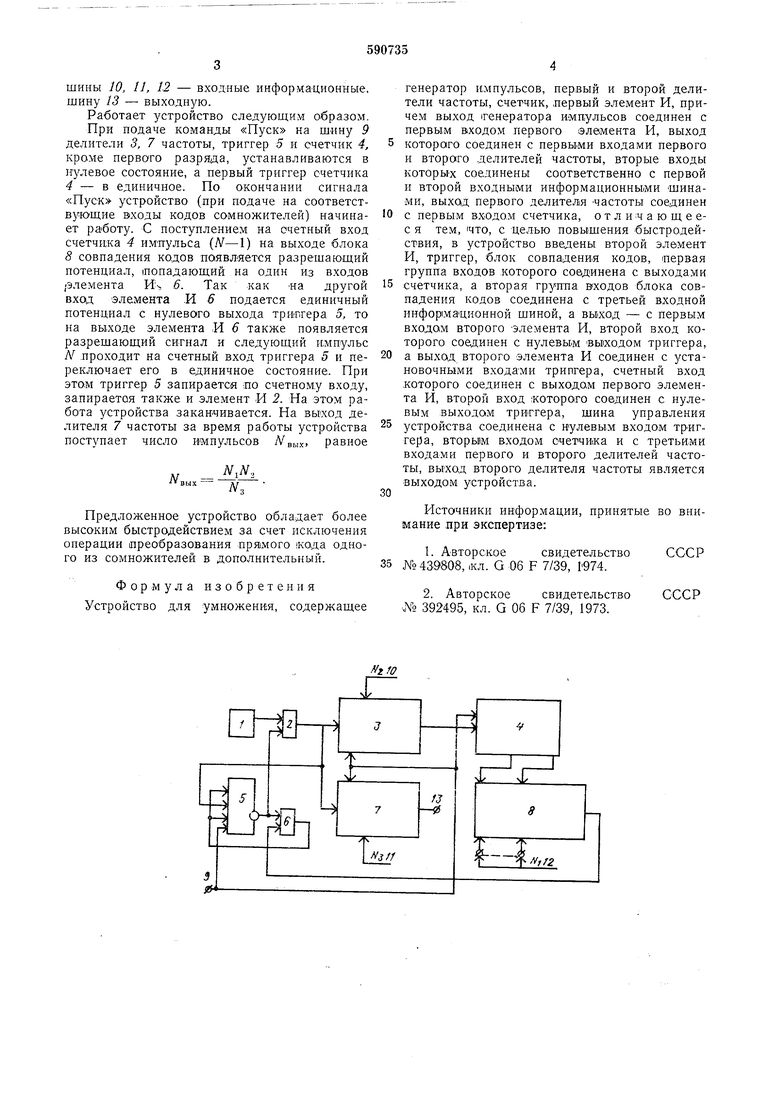

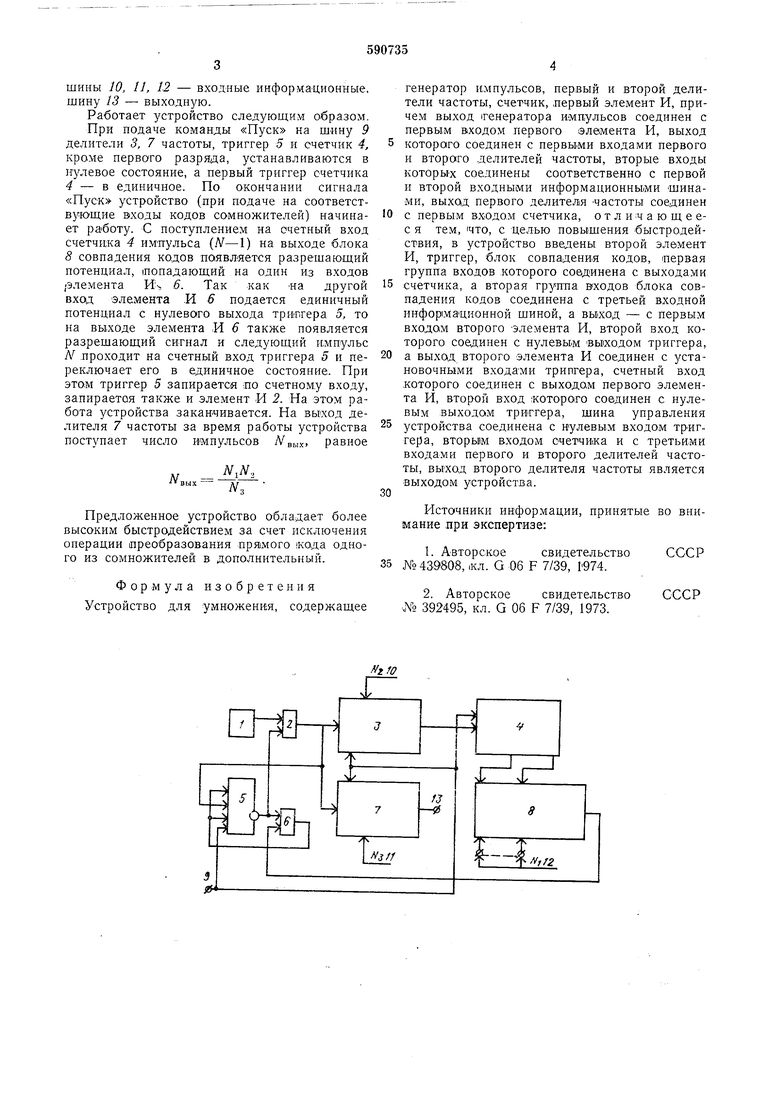

С этой целью в устройство введены второй элемент И, триггер, блок совпадения кодов, первая группа входов которого соединена с выходами счетчика, вторая ;группа входов блока совпадения кодов - с третьей входной информационной шиной, а выход - г первым входом второго элемента И, второй вход которого соединен с нулевьш выходо-м триггера. Выход второго элемента И подключеп к установочным входам триггера, счетный вход триггера соединен с выходом первого элемента И, а второй вход первого элемента И - с нулевым выходом триггера. Шина управления устройства соединена с нулевым входом триггера, вторЫМ входом счетчИКа и с третьими входами первого и второго делителей частоты, выход второго делителя частоты является выходом устройства.

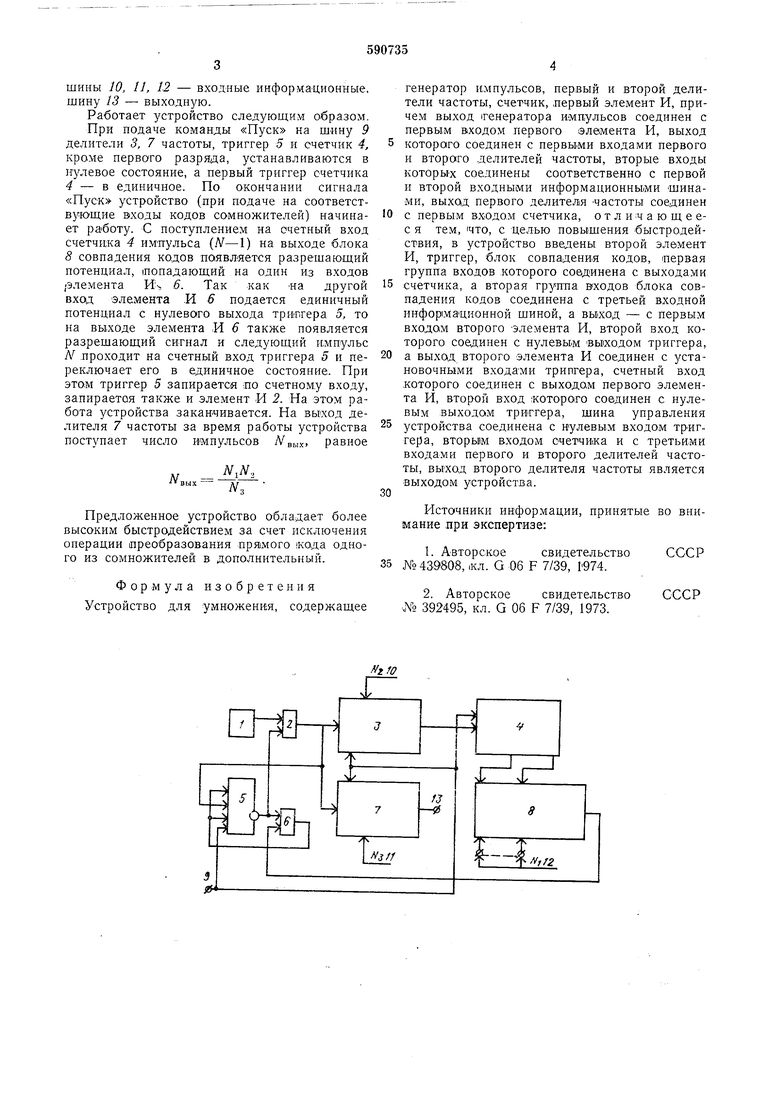

Структурная схема устройства приведена на чертеже.

Устройство содержит генератор / импульсов, первый элемент И 2, первый делитель 3 частоты, счетч 1х 4, триггер 5, второй элемент И 6, второй делитель 7 частоты, блок 8 совпадения кодов, а также шину 9 управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Множительно-делительное устройство | 1984 |

|

SU1238062A1 |

| Устройство для кусочно-линейной аппроксимации | 1985 |

|

SU1259258A1 |

| Цифровой кодирующий преобразователь частоты | 1980 |

|

SU938402A1 |

| Вычислительное устройство | 1980 |

|

SU997033A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Цифровой кодирующий преобразователь частоты следования импульсов | 1980 |

|

SU919080A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для воспроизведенияКВАдРАТичНыХ фуНКций | 1978 |

|

SU842802A1 |

Авторы

Даты

1978-01-30—Публикация

1976-04-17—Подача